* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Design and Simulation of Frequency Divider by Negative Differential

Spark-gap transmitter wikipedia , lookup

Cavity magnetron wikipedia , lookup

Stage monitor system wikipedia , lookup

Spectrum analyzer wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Ringing artifacts wikipedia , lookup

Buck converter wikipedia , lookup

Mathematics of radio engineering wikipedia , lookup

Opto-isolator wikipedia , lookup

Zobel network wikipedia , lookup

Two-port network wikipedia , lookup

Wien bridge oscillator wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Resonant inductive coupling wikipedia , lookup

Regenerative circuit wikipedia , lookup

Rectiverter wikipedia , lookup

Chirp spectrum wikipedia , lookup

Superheterodyne receiver wikipedia , lookup

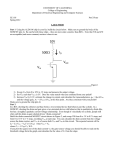

Design and Numerical Analysis of Frequency Divider by Negative Differential Resistance Devices Yaw-Hwang Chen, Chi-Pin Chen, Kwang-Jow Gan, Cher-Shiung Tsai, Dong-Shong Liang, Long-Xian Su, 孫偉倫, and 陳家弘 Department of Electronic Engineering, Kun Shan University of Technology [NSC93-2215-E-168-002] Abstract which is called chaos. In this paper, we We studied the novel frequency divider discuss this problem based on numerical using the chaotic circuit with respect to simulation using a test circuit consisting of input signal distortions and the variations in discrete devices. the current-voltage characteristics of the MOS-BJT-NDR. The MOS-BJT-NDR device is consisted of the metal-oxidesemiconductor field-effect-transistor (MOS) 2.The MOS-BJT-NDR Devices Figure 1 shows a MOS-BJT-NDR device, which is composed of three NMOS devices. This device could exhibit the negative differential resistance (NDR) characteristics in the current-voltage curve by suitably arranging the parameters of the MOS devices. devices ,one NPN device and one PMOS device. This MOS-BJT-NDR device can exhibit various NDR current-voltage (I-V) characteristics by choosing appropriate parameters for transistors. In this paper, we select the parameters of MOS-BJT-NDR: mn1 width=3um, mn2 Keywords: Negative Differential Resistance (NDR), Frequency bifurcation Divider, chaos, 1.Introduction Recently, we have proposed a novel frequency divider using MOS-BJT-NDR devices, which exploit the strong nonlinearity of the MOS-NDR devices. Negative differential resistance (NDR) devices have generated substantial research width=50um, bjt3=ln02, mp4 width=30u. The length parameters of three MOS are all fixed at 0.35μm. Figure 2 shows the measured I-V characteristics, when the Vgg voltage is fixed at 3.3V. interest owing to their unique NDR characteristic [1]-[2]. Taking advantage of the NDR feature, circuit complexity can be greatly reduced and novel circuit applications have also obtained. A circuit consisting of such nonlinear elements often shows complex behavior Figure 1. The circuit configuration for a MOS-BJT-NDR device. fabricated circuit. This frequency divider Figure 2. This is the I-V characteristic curve of MOS-BJT-NDR devices when the Vgg is fixed at 3.3V. III. The Frequency Divider based on MOS-BJT-NDR Device Here we will use mathematica software to simulate and verify our purposed circuit. MATHEMATICA is a powerful and convenient tool for solving complex mathematic problem. We use the piecewise-linear (PWL) approximation method to describe the I-V characteristics of a MOS-BJT-NDR device which is shown in figure 3. In PWL approximation, the I-V cure is composed of three linear regions. They are the first positive resistance region, the negative resistance region, and the second positive resistance region. They can make the analysis more easier and still have accurate results. consists of a MOS-BJT-NDR device, an inductor L and a capacitor C. This is a type of van der Pol oscillator having an input terminal. The differential equations determining the system’s behavior are expressed as di L (t ) Vin (t ) Vout (t ) ………………(1) dt L dVout (t ) i L (t ) i NDR (Vout ) ………….(2) dt Cout Generally, in nonlinear systems which generate chaos, long-period behavior is also observed in some parameter regions. This is called the bifurcation phenomenon. In the bifurcation region, the system’s output period is the integer-multiple of the input period. It should be noted that the operation frequency range depends on the LC characteristic frequency, determined as 1 2 LC . Therefore, a frequency range close to the cutoff frequency of the MOS-BJT-NDR device is expected if the appropriate values are chosen for L and C. Figure 4.This figure shows the circuital configuration of the chaotic generator. Figure 3. This I-V curve shows the piecewise-linear (PWL) approximation for the MOS-BJT-NDR device. Figure 4 shows the configuration of the Now, we analyze the mechanism of the frequency dividing operation of our proposed circuit. The frequency dividing operation is explained by the relation between the charging time of the figure 7. When the input frequency is any capacitance Ctot, and the input period. At low input frequency, charges sufficient to switch the MOS-BJT-NDR are supplied to the output capacitance during a cycle of the input. However, when the input frequency increases, the charges supplied to the capacitance during a cycle decrease due to the shorter period and the increased impedance of the inductor. Then, the amount of charges supplied to the capacitance is not value, besides the above-mentioned values, the system will be a chaotic state as in figure 8. sufficient to switch the MOS-BJT-NDR. Consequently, two or more cycles are necessary to switch the MOS-BJT-NDR. This causes the frequency dividing operations of 1/2, 1/3, and so on. The operation frequency range is decided to the LC characteristic frequency, i.e. V. Conclusions In summary, frequency divider is a bulk and complexity circuit fabricated many devices. The novel frequency divider our purposed is fabricated fewer devices, an inductor L, a capacitor C and one MOS-BJT-NDR device. 1 2 LC . Therefore, the frequency range of our circuit is decided to the chosen LC, too. IV. Numerical Analysis Result To confirm our analysis results, we tested a circuit consisting of inductor, capacitor, and MOS-BJT-NDR devices. The values of the Vout, i.e. the periods of Vin and Vout are equal as shown in figure 5. When the input frequency is equal to 3GHz, we can observe the relation of Vin and Vout, i.e. the period of Vout is twice as the period of Vin as shown in figure 6. And then we change the input frequency is equal to 2GHz, we can observe the relation of Vin and Vout, i.e. the period of Vout is triple as the period of Vin as shown in Vout 0.8 0.4 0 0.2 0.4 0.6 0.8 1 Vin Fig.5 The periods of Vin and Vout are equal. 1.2 0.8 Vout inductor and capacitor were chosen to be L is equal to 2nH, and Cout is equal to 1.443pF. The input signal amplitude A is equal to 0.3V with a dc bias voltage, Vo, of 0.6 V. The current-voltage characteristics of the MOS-BJT-NDR used in our proposed circuit were similar to those shown in figure 3. When the input frequency is equal to 6GHz, we can observe easily the relation of Vin and 1.2 0.4 0 0.2 0.4 0.6 0.8 1 Vin Fig.6 the period of Vout is twice for the period of Vin. divider using resonant tunneling chaos 1.2 Vout 0.8 0.4 0 0.2 0.4 0.6 0.8 1 Vin Figure 7. The period of Vout is triple for the ‘88 GHz dynamic 2 : 1 frequency divider using resonant tunnelling chaos circuit’, Electron. Lett., 2003, 39, (21), pp. 1546–1548 6. To-Kai Liang, Kwang-Jow Gan, Cher-Shiung Tsai, Yaw-Hwang Chen, ‘Frequency Multiplier Using Multiple-Peak MOS-NDR Devices and Circuits’, ASTC, 2004. period of Vin. 1.2 Vout 0.8 0.4 0 0.2 circuit’. Proc. Int. Conf. on Indium Phosphide and Related Materials, Nara, Japan, 2001, pp. 236-239 4. Kawano, Y., Ohno, Y., Kishimoto, S., Maezawa, K., and Mizutani, T.: ‘50 GHz frequency divider using resonant tunnelling chaos circuit’, Electron. Lett., 2002, 38, (7), pp. 305–306 5. Kawano, Y., Ohno, Y., Kishimoto, S., Maezawa, K., Mizutani, T., and Sano, K.: 0.4 0.6 0.8 1 Vin Figure 8. The system is in a chaotic state. VI. Reference 1. KAWANO, Y., KISHIMOTO, S., MAEZAWA, K., and MIZUTANI, T.: ‘Robust operation of a novel frequency divider using resonant tunneling chaos circuit’, Jpn. 1 Appl. Phys., 1999, 39, pp. 3334-3338 2. KAWANO, Y., KISHIMOTO, S., MAEZAWA, K., and MIZUTANI, T.: ‘Resonant tunneling chaos generator for high-speed/low-power frequency divider’, Jpn. 1 Appl. Phys., 1999, 38, pp. L1321-Ll322 3. KAWANO, Y., OHNO, Y., KISHIMOTO, S., MAEZAWA, K., and MIZUTANI, T.: ‘High-speed operation of a novel frequency