* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download QUANTUM AND COULOMB EFFECTS IN NANODEVICES 1

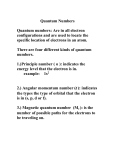

Old quantum theory wikipedia , lookup

Density of states wikipedia , lookup

History of quantum field theory wikipedia , lookup

Aharonov–Bohm effect wikipedia , lookup

Electron mobility wikipedia , lookup

Hydrogen atom wikipedia , lookup

Quantum potential wikipedia , lookup

Quantum vacuum thruster wikipedia , lookup

Anti-gravity wikipedia , lookup

Quantum tunnelling wikipedia , lookup

Monte Carlo methods for electron transport wikipedia , lookup