* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download - aes journals

Standby power wikipedia , lookup

Electronic engineering wikipedia , lookup

Wireless power transfer wikipedia , lookup

Ground (electricity) wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Electrical ballast wikipedia , lookup

Audio power wikipedia , lookup

Opto-isolator wikipedia , lookup

Power factor wikipedia , lookup

Current source wikipedia , lookup

Power over Ethernet wikipedia , lookup

Power inverter wikipedia , lookup

Electric power system wikipedia , lookup

Electrification wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Power MOSFET wikipedia , lookup

Amtrak's 25 Hz traction power system wikipedia , lookup

Voltage regulator wikipedia , lookup

Electrical substation wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Surge protector wikipedia , lookup

Three-phase electric power wikipedia , lookup

History of electric power transmission wikipedia , lookup

Buck converter wikipedia , lookup

Stray voltage wikipedia , lookup

Power engineering wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Voltage optimisation wikipedia , lookup

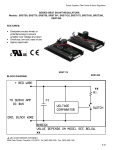

JOURNAL OF INFORMATION, KNOWLEDGE AND RESEARCH IN ELECTRICAL ENGINEERING POWER QUALITY PROBLEMS STUDY ON IEEE 14 BUS SYSTEMS AND THEIR MITIGATION USING UPQC WITH DIFFERENT CONTROL SCHEMES 1 MR. H. M. KARKAR, 2 DR. S. N. PANDYA 1M.E. [Power System] Student, Department Of Electrical Engineering, L.D. College Of Engineering, Ahmedabad 2Associate Professor, Department Of Electrical Engineering, L.D. College Of Engineering, Ahmedabad [email protected], [email protected] ABSTRACT: In little more than ten years, electricity power quality has grown from obscurity to a major issue. Power quality is among the main things that is emphasized and is taken into consideration by utilities in order to meet the demands of their customer. At each passing day this issue has becoming more serious and at the same time the user’s demand on power quality also gets more critical.Thus it is essential to establish a power quality monitoring system to detect power quality disturbance. Several research studies regarding the power quality have been done before and their aims frequently concentrated on the collection of raw data for a further analysis, so the impacts of various disturbances can be investigated. This thesis deals with the implementation of fact device UPQC on IEEE 14 BUS system. Different control schemes have been suggested for UPQC. Also a methodology is shown for determining the most sensitive bus and the most sensitive load. UPQC is installed between the sensitive bus and the load with three different control schemes and results are shown for different types of fault at different-different locations. Also a comparison is shown between all the control schemes. Keywords— UPQC, Voltage Sag, Voltage Swell, Power Quality. Hysteresis control,Unit vector template generation technique,PWM technique I: INTRODUCTION Due to the extensive use of power electronic based equipments/loads almost in all areas, the point of common coupling (PCC) could be highly distorted [1]-[3]. The switching ON/OFF of high rated load connected to PCC may result into voltage sags or swells on the PCC. There are several sensitive loads, such as computer or microprocessor based AC/DC drive controller, with good voltage profile requirement; can function improperly or sometime can lose valuable data or in certain cases get damaged due to these voltage sag and swell conditions. One of the effective approaches is to use a unified power quality conditioner (UPQC) at PCC to protect the sensitive loads. A UPQC is a combination of shunt and series APFs, sharing a common dc link [1-3], [610]. It is a versatile device that can compensate almost all power quality problems such as voltage harmonics, voltage unbalance, voltage flickers, voltage sags & swells, current harmonics, current unbalance, reactive current, etc. The Unified Power Quality Conditioner (UPQC) has evolved to be one of the most comprehensive custom power solutions for power quality issues relating to non-linear harmonic producing loads and the effect of utility voltage disturbance on sensitive industrial loads. To investigate the performance of the proposed control schemes for the UPQC, simulations are carried out and validated with experimental results. II: SYSTEM CONFIGURATION The system configuration for UPQC is shown in the Fig.1.The voltage at PCC may be or may not be distorted depending on the other non-linear loads connected at PCC. Also, these loads may impose the voltage sag or swell condition during their switching ON and/or OFF operation. The UPQC is installed in order to protect a sensitive load from all disturbances. The UPQC consists of two voltage source inverters connected back to back, sharing a common dc link. Each inverter is realized by using six IGBT switches. One inverter is connected parallel with the load, acts as shunt APF, helps in compensating load harmonic current, reactive current and maintain the dc link voltage at constant level. The second inverter is Fig.1 Block Diagram of UPQC connected in series with the line using series transformers, acts as a controlled voltage source maintaining the load voltage sinusoidal and at desired. ISSN: 0975 – 6736| NOV 12 TO OCT 13 | VOLUME – 02, ISSUE - 02 Page 186 JOURNAL OF INFORMATION, KNOWLEDGE AND RESEARCH IN ELECTRICAL ENGINEERING III: STEADY STATE POWER FLOW ANALYSIS The UPQC is controlled in such a way that the voltage at load bus is always sinusoidal and at desired magnitude.In the following analysis the load voltage is assumed to be in phase with terminal voltage even during voltage sag and swell condition. In this particular condition, the series APF could not handle reactive power and the load reactive power is supplied by shunt APF alone [5]. Fig.2 Equivalent Circuit of a UPQC The source voltage, terminal voltage at PCC and load voltage are denoted by Vs, Vt and VL respectively. The source and load currents are denoted by is and iL respectively. The voltage injected by series APF is denoted by VSr, whereas the current injected by shunt APF is denoted by iSh. Taking the load voltage, VL, as a reference phasor and suppose the lagging power factor of the load is Cos L then we can write;[5] VL=VL00 (1) IL=IL-L (2) Vt=VL(1+k) 00 (3) Where factor k represents the fluctuation of source voltage, defined as, k= (4) The voltage injected by series APF must be equal to, VSr=VL−Vt=−kVL∠00 (5) The UPQC is assumed to be lossless and therefore, the active power demanded by the load is equal to the active power input at PCC. The UPQC provides a nearly unity power factor source current, therefore, for a given load condition the input active power at PCC can be expressed by the following equations, Pt=PL (6) Vt.iS=VL.iL.cosφL (7) VL(1+k).iS=VL.iL.cosφL (8) iS =iL/(1+k)*cosφL (9) The above equation suggests that the source current i S depends on the factor k, since φLand iL are load characteristics and are constant for a particular type of load. The complex power absorbed by the series APF can be expressed as, S Sr =VSr .iS * (10) PSr =VSr .iS . cosφs =-k .VL .iS .cosφs (11) QSr=VSr .iS .sinφS (12) φS = 0 , since UPQC is maintaining unity power factor PSr =VSr .iS=−k .VL .iS (13) QSr ≅0 (14) The complex power absorbed by the shunt APF can be expressed as, S Sh =VL .iSh * (15) The current provided by the shunt APF, is the difference between the input source current and the load current, which includes the load harmonics current and the reactive current. Therefore, we can write; iSh =iS −iL (16) iSh =iS ∠00 −iL ∠ φL (17) iSh =iS −( iL .cosφL –j iL .sinφL ) (18) iSh =(iS −iL .cosφL ) + j iL .sinφL (19) PSh =VL .iSh .cosφsh =VL .(iS −iL .cosφL) (20) QSh=VL .iSh .sinφsh V L .iL .sinφL (21) When a sag is detected such that |Vs2| <|Vs1| (rated), then for UPQC-Q , Vinj is calculated from as.[21] Vinj2 = (Vs12 – Vs22) Now from PWM method √2Vinj = MI (Vdc/2), where MI is the desired modulation index (MI). Therefore, MI = (2√2 .Vinj)/Vdc If x is the p. u. sag to be mitigated, minimum dc link voltage would be Vdc= 2√(2 )* √(x(2-x)) * Vs1, for maximum value of MI =1 (taking the injection transformer turns ratio to be 1:1). IV: CONTROL SCHEMES FOR UPQC The control strategy is basically the way to generate reference signals for both shunt and series APF. The effectiveness of the UPQC depends on its ability to follow the reference signals with a minimum error to compensate the voltage sag and swell or any other undesirable condition. The series APF acts as a controlled voltage source. The shunt APF acts as a control source for maintaining the DC link voltage. The shunt APF also provides required var to the load such that the power factor at PCC is unity and only fundamental active power is supplied by the source. The voltage injected by series APF can be varied from 0o to360o .The series injected voltage has to be in phase (out of phase) with PCC voltage to compensate voltage sag swell. 4.1 Different Control Schemes for UPQC 1. Control for Series and Shunt APF 2. Unit Vector Template Generation(UVTG) Technique for Series and Shunt APF 3. Sinusoidal Pulse Width Modulation(SPWM) Technique for Series and Shunt APF V: IEEE 14 BUS TEST SYSTEMS The IEEE 14 Bus Test Case represents a portion of the American Electric Power System (in the Midwestern US) as of February, 1962. A muchXeroxed paper version of the data was kindly provided by Iraj Dabbagchi of AEP and entered in IEEE Common Data Format by Rich Christie at the University of Washington in August 1993. ISSN: 0975 – 6736| NOV 12 TO OCT 13 | VOLUME – 02, ISSUE - 02 Page 187 JOURNAL OF INFORMATION, KNOWLEDGE AND RESEARCH IN ELECTRICAL ENGINEERING Fig.3 IEEE 14 Bus System 5.1 SYSTEM VARIFICATION FROM LOAD FLOW AND SIMULATION Table No.1 Bus No. 1 2 3 4 5 6 7 8 9 10 11 12 13 14 Actual Value (p.u) 1.06 1.0450 1.01 1.016 1.018 1.0700 1.06 1.0901 1.05334 1.0489 1.0559 1.0558 1.050 1.0339 Bus Voltage From Load Flow(p.u) 1.06 1.0448 1.0097 1.0162 1.01194 1.0698 1.05947 1.08931 1.0524 1.0481 1.05487 1.05422 1.05494 1.03308 Bus Voltages from Simulation (p.u) 1.06 1.0449 1.0099 0.9967 0.999 1.069 1.0208 1.0900 1.0193 1.0243 1.0438 1.0614 1.05705 1.02889 Table No.2 Bus No. 1 2 3 4 5 6 7 8 9 10 11 12 13 14 IEEE Bus Voltages (kv) 69 69 69 69 69 13.8 13.8 18 13.8 13.8 13.8 13.8 13.8 13.8 Simulation Results (kv) 69.00 69.00 69.00 67.18 67.42 13.81 13.45 18.07 13.28 13.25 13.43 13.67 13.60 13.24 VI: METHODOLOGY FOR DECIDING THE LOCATION OF UPQC As our test system is the IEEE 14 BUS system which has 22 lines and 14 buses. Bus 1 is Slack Bus and Buses 2,3,6,8 are the generator buses. All the buses except bus 1 contains loads also. So it is important to decide that which bus is the most critical bus. For deciding the location of UPQC a fault based technique is suggested. The bus which is always affected by the faults, no matter where the fault is taking place in the system, is called as most critical bus and the load connected to that bus is called as the most critical load. The location of UPQC is decided in two steps : 6.1 STEP 1 1. At first we created the 3 phase fault at the mid-point of each line for a short period, as the 3 phase fault is the most severe one. 2. Then we measured the voltages of all the buses except the generator and slack bus. 3. Then we selected the 2 most critical lines. They are called critical because when we created the fault on these lines, the effect of 3 phase fault was most severe and they are affecting the most number of buses in the system. 4. After preparing the table for these results we selected the line 7-9 and line 9-10 as the most critical lines. 6.2 STEP 2 1. After selecting the bus 9-10 & 7-9 as most critical line, we created the different types of faults at 5-5 % distance on these lines. 2. We plotted the graph between the distance and the voltage magnitude. 3. After analyzing all the graphs and tables, we prepared the table for all conditions which shows that during all types of faults which buses are mostly affected. VII: ANALYSIS FROM ABOVE RESULTS Sr. No 1 2 3 7.1 Fault Type 3Phase fault PhaseA fault PhaseA-B fault Table No.3 Buses Line with 7-9 sag Most Critical 4,7,9,10 7,9,10 ,11,14 7,9,10, 7,9,10 11,14 7,9,10 7,9,10 11,14 Line 9-10 Most Critical 9,10 9,10 9,10 Conclusion from above Results 1. Above table shows that bus 9 and bus 10 are the most critical buses because they are always suffering from sag created by different types of faults at different – different locations. ISSN: 0975 – 6736| NOV 12 TO OCT 13 | VOLUME – 02, ISSUE - 02 Page 188 JOURNAL OF INFORMATION, KNOWLEDGE AND RESEARCH IN ELECTRICAL ENGINEERING 2. But we chose bus 9 as the most critical bus as larger load is connected at that bus. VIII: SIMULATION RESULTS WITH DIFFERENT CONTROL SCHEMES 8.1 Load and Bus Voltages during Fault Condition Fig. 6 Waveforms at Load Side with Hysteresis Controller 8.3 SPWM Based Series and Shunt Controller Fig. 4 Source and Load side wave forms during fault condition 8.2 Hystersis Based Series and Shunt Controller Fig. 7 SPWM based Controller Fig. 5 Hysteresis Control ISSN: 0975 – 6736| NOV 12 TO OCT 13 | VOLUME – 02, ISSUE - 02 Page 189 JOURNAL OF INFORMATION, KNOWLEDGE AND RESEARCH IN ELECTRICAL ENGINEERING Fig. 10 Load Side Waveforms with UVTG Technique Fig. 8 Load side waveforms with SPWM Technique 8.4 Unit Vector Template Generation Technique IX: CONCLUSION If the sags are more frequent and for a very short duration then it is better to use Hysteresis Controller.since it is faster and in-sensitive to system parameters with inherent peak current limiting capability. Also it is easy to implement and in closed loop, offers current protection with excellent dynamic response. It ensures the elimination of higher order harmonics of the load without the need of any additional filter circuits. SPWM technique takes more simulation time and it takes more time to maintain dc link voltage. If the duration of sag is more but not occurring frequently then it is better to use SPWM technique If the sags are more frequent and for a very short duration and the load is most sensitive then it is better to use Hysteresis controller Unit vector template generation technique is more accurate and precise as we are generating a pu. Reference signal and then locking the phase other wise results are similar to hysteresis control. Fig. 9 UVTG Technique REFRENCES ISSN: 0975 – 6736| NOV 12 TO OCT 13 | VOLUME – 02, ISSUE - 02 Page 190 JOURNAL OF INFORMATION, KNOWLEDGE AND RESEARCH IN ELECTRICAL ENGINEERING [1] H. Akagi, “New trends in active filters for improving power quality”, Proceedings of the 1996 International Confe, Vol.1, Jan 1996, pp. 417 –425 [2] B. Singh, K. Al-Haddad, A. Chandra, “A Review of Active Power Filters for Power Quality Improvement”, IEEE Trans on Industrial Electronics, Vol. 45, No.5, Oct1999, pp. 960-071. [3] Khadkikar V, Agarwal P, Chandra A, Barry A O and Nguyen T.D, “A simple new control technique for unified power quality conditioner (UPQC)”, Harmonics and Quality of Power, 2004. 11th International Conference on Sept.2004, pp. 289 – 293. [4] Vinod Khadkikar, A.Chandra, A.O. Barry, T.D. Nguyen “Steady state power flow analysis of unified power quality conditioner (UPQC), Proceedings of International conference on Industrial Electronics and Control Applications (ICIECA), 2005, pp. 6. [5] M.A. Hannan, Azah Mohamed, “PSCAD/EMTDC simulation of unified series shunt compensator for power quality improvement”, IEEE Transactions on power delivery, Vol.20, No.2, 2005, pp.1650-1656. [6] Analysis of power flow in upqc under voltage sag and swell condition V. Khadkikar Student Member, IEEE A. Chandra, Senior Member, IEEE ETS, Montreal, CA [7] Hind Djeghloud, Hocine Benalla, Amar Bentounsi, “Supply current and load voltage distortions suppression using the unified powe quality conditioner”, Proceedings of International Multi confence on Systems,Signals and Devices, 2008. [8] New Control Scheme for a Unified Power Quality Compensator-Q With Minimum Active Power Injection Woo Cheol Lee, Dong Myung Lee, Member, IEEE, and Taeck Kie LeeIEEE TRANSACTIONS ON POWER DELIVERY, vol. 25, no. 2, april 2010 [9] H. Fujita and H. Akagi, “The unified power quality conditioner: The integration of seriesand shunt-active filters,” IEEE Trans. Power Electronics., vol. 13, no. 2, pp. 315–322, May 1998 [10] D. O. Kisck, V. Navrapescu, and M. Kisck, “Single-phase unified power quality conditioner with optimum voltage angle injection forminimum VA requirement,” in Proc. IEEE Power Eng. Soc. Comm.,2007, vol. 2, pp. 574– 579. [11] S. S. Choi, B. H. Li, and D. M. Vilathgamuwa, “Dynamic voltage restoration with minimum energy injection,” IEEE Trans. Power Syst.vol. 15, no. 1, pp. 51–57, Feb. 2000. [12] B. H. Li, S. S. Choi, and D. M. Vilathgamuwa, “A new control strategy for energy-saving dynamic voltage restoration,” in Proc. IEEE Power Eng. Soc. Summer Meeting, Jul. 16–20, 2000, vol. 2, pp. 1103–1108. [13] S. Muthu and J. M. S. Kim, “Steady-state operating characteristics of unified active power filters,” in Proc. IEEE App. Power Electron. Conf. Expo., Feb. 1997, vol. 1, pp. 199–205. [14] Y. Kolhatkar and P. Das, “Experimental investigation of a single-phase UPQC with minimum VA loading,” IEEE Trans. Power Del., vol. 22,no. 1, pp. 373–380, Jan. 2007. [15] B. Han, B. Bae, S. Baek, and G. Jang, “New configuration of UPQC for medium-voltage application,” IEEE Trans. Power Del., vol. 21, no.3, pp. 1438–1444, Jul. 2006. [16] Khadikikar V, Chandra A, Barry A.O, Nguyen T.D. Conceptual Study of Unified Power Quality Conditioner (UPQC).IEEE International Symposium on Industrial Electronics 2006; 2: 1088 – 1093. DOI: 10.1109/ISIE.2006.295788. [17] Khadkikar, V, Chandra A, Barry A.O, Nguyen T.D. Application of UPQC to protect a sensitive load on a polluted distribution network. IEEE Power Engineering Society General Meeting 2006; DOI: 10.1109/PES.2006.1709522. [18] S. Srinath, M.P. Selvan, “A combined mode of control for UPQC connected to a low voltage distribution system”, In press for publication in the Australian Journal of Electrical and Electronics Engineering. [19] Khadkikar V, Agarwal P, Chandra A, Barry A O and Nguyen T.D, “A simple new control technique for unified power quality conditioner (UPQC)”,Harmonics and Quality of Power, 2004. 11th International Conference on 12-15 Sept. 2004, pp. 289 – 293. [20] Yunping Chen; Xiaoming Zha; Jin Wang; Huijin Liu; Jianjun Sun;Honghai Tang,“ Unified Power Quality Conditioner (UPQC): the theory,modeling and application.” Power System Technology, 2000. Proceedings.Volume: 3, 4-7 Dec. 2000. Page(s): 1329 -1333. [21] Muthu, S.; Kim, J.M.S, “Steady-state operating characteristics of unified active power filters.” Applied Power Electronics Conference and Exposition 1997. APEC '97 Conference Proceedings 1997, Twelfth Annual, Volume: 1, 23-27 Feb 1997, pp. 199 -205. [22] Li R.; Johns A T. and Elkateb M.M., “Control concept of Unified Power Line Conditioner.” Power Engineering Society Winter Meeting, 2000. IEEE,Volume:4 , 23-27 Jan 2000, pp. 2594 -2599 [23] Investigation on the Performance of UPQC-Q for Voltage Sag Mitigation andPQ Improvement at a Critical Load Point, Malabika Basu1* S. P. Das Gopal k dubey ISSN: 0975 – 6736| NOV 12 TO OCT 13 | VOLUME – 02, ISSUE - 02 Page 191