* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Second Stage Tuning Procedure for Analog MOS Design Reuse

Current source wikipedia , lookup

Voltage optimisation wikipedia , lookup

Stray voltage wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Transmission line loudspeaker wikipedia , lookup

Alternating current wikipedia , lookup

Mains electricity wikipedia , lookup

Buck converter wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Rectiverter wikipedia , lookup

Two-port network wikipedia , lookup

Regenerative circuit wikipedia , lookup

Semiconductor device wikipedia , lookup

Integrated circuit wikipedia , lookup

History of the transistor wikipedia , lookup

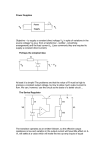

Second Stage Tuning Procedure for Analog MOS Design Reuse Methodology A. F. Adnan, A. N. Other [Three main elements in abstract 1) problem statement, 2) Contribution, 3) Significance.] This work proposes a two-stage analog circuit design reuse methodology by extending existing fabrication process rescaling procedures with a follow-on systematic tuning procedure stage based on DC output voltage scaling. It increases the potential for design reuse with shortchannel MOSFET circuit designs when compared to the current single stage rescaling work. Two Miller amplifier circuits were designed on 0.18 μm and 0.13 μm CMOS processes in order to analyze circuit performance achieved with the proposed method compared to the existing methods. The additional tuning stage results in an improved amplifier gain up to 16 dB and up to 2.5 times faster settling time compared to single stage scaling with 33% power reduction and 28% smaller silicon area when compared to the original design. [Must be concise and provide the following. 1) Introduction to the problem, 2) Critical review of stateof-the art related works, 3) Motivation for extended work.] Introduction: Circuit design reuse methodology has been developed to reduce analog design time during fabrication process migration from one process to another. Scaling techniques (constant inversion-level scaling and channel-length scaling found in previous literature [1-4]) share the same goal which is to maintain circuit performance on various CMOS processes, but with different scope of work. The channel scaling rule proposed in [1] was tested on long-channel devices and resulted in extra silicon area than the original design. In [2], the Cadence optimization function is used to solve the problem of voltage gain degradation in the migrated design on a 0.12 m process. The work in [3] added a second tuning stage to fine-tune the compensation network based on complex Levenberg-Marquardt algorithm, but at the expense of 3 times bigger silicon area due to the requirement for a larger size compensation capacitor. This work extends the design reuse methodology by applying systematic device tuning on transistor sizing to increase the reliability of the methodology for short-channel transistor design. [Must state the limitation of existing works and how improvement is made. Basically answering why you have to do this?] Problem Statement: Fig. 1 illustrates the difference of ID0 as in (1) and simulation of I-V curves using the same process and design parameters. In the saturation region, data analysis shows that the difference between NMOS short-channel current, ID2, and ID0 is more than 2 times higher than the difference between long-channel current, ID1, and ID0, even though they have the same sizing ratio, overdrive voltage and theoretically the same threshold voltage, VTH. The channel modulation effect term, (1+λVDS) which provides a positive slope straight line starting from ID0 reduces the difference between ID1 and ID0 but at the same time increases the difference between IDS and ID0. The difference reflects the accurateness of the scaling rules which is affected by short and long channel transistor characteristics. [Statement of your proposed work, i.e., objective. May include figure that illustrate the framework of the proposed work (algorithm or architecture or system or model etc.] Proposed Algorithm: This work is motivated by work in [2] with an improvement for short-channel transistor migration. The most crucial circuit tuning actions will be undertaken in the second stage to soften the impact of the short-channel effect. The proposed methodology has been tested down to minimum transistor length, L = 0.33 m compared to [2] which is L = 1.5 m. Instead of tuning the compensation network which has been done before in [3], this work attempts to tune the size of the transistor to optimize performance of the short-channel migrated design focussing on the voltage gain at reduced silicon area. The scaling rule proposed in [2] considers the following key performance parameters in the scaling rules derivation compared to other literature: voltage gain, bandwidth, phase margin, power and area. It was derived based on the level-1 MOSFET current equation (1). This work utilizes scaling rules in [2] on the first stage of the circuit design instead of deriving new scaling rules. [Procedure describing how the result/proof is obtained. The proposed work can be as one of these types: experimental, simulation, mathematical. Clearly specify development/ design/ analysis setup. What verification method/procedure (data, tool, observed criteria) are used.] Methodology: Second Stage - Tuning: MOSFET current equation (1) poorly relates device sizing with VDS. Therefore, by assuming a constant biasing point on both Fig. 3 The relationship between VY/VDD and voltage load lines of 0.18 m and 0.13 m devices, output nodes gain VY/VX for the short-channel Miller amplifier on 0.18 and 0.13 m process. [Font 9pt, high quality graphic.] VY shall be rescaled to KVVY1, where KV = VDD1/VDD2 is supply voltage scaling coefficient. The effect of VY on the gain is shown in Fig. 3. MiCEX2012 | 1 To shift the node voltages, it is proposed here to adjust the device width compared to the length to avoid complex current behaviour related to channel modulation effects. Therefore, the width of M5 and M6 are reassessed first to satisfy VEG2=VEG1 as suggested in [2]. Practically, VTH is ‘varied’ by changing the transistor dimensions [5]. Therefore, an optimization loop can be derived from (4) when needed. For better continuity of the device sizing, all the remaining PMOS transistors are rescaled according to next width scaling parameter, KWP+ = W3/W2. By doing so, it ensures that the remaining PMOS transistors with the same ratio of sizing remain same. Notice that VY3 for long-channel shifts to KVVY1 after the PMOS width is rescaled to KWP+ but not for short-channel. Therefore, manual tuning is done to adjust the VY to 3.29/0.39 m and VY shifted to 0.58V. [Results may be presented in a graph/ table form. Clearly analyze the results.] Results and Discussion: The result in Table 2 shows that by applying the second stage tuning, the original gain can be maintained and settling time can be improved up to 2.5 times faster compared to the single stage rescaling work. Power dissipation is reduced about 33% according to KV coefficient and area is reduced 25-28% from the original design. Table 2: The Miller amplifier circuit performances on 0.18 0.13 m processes for long and short-channel. MiCEX2012 | 2 Table 1: Transistor sizing (W/L, W2→W3/L) and output node voltages for the Miller amplifier designed on 0.18 m and 0.13 m processes. [Font 9pt] LongShort0.18 m 0.13 m channel channel 18.20/0.72 7.5/0.45 6.80/0.33 5/1.0 8.54/0.72 4.55/0.72 2.5/0.54 2.27/0.39 [Stress on the contribution and significance of work] Conclusion: The proposed systematic tuning for analog design reuse result in improved design scaling accuracy especially in the short-channel design. The performance of the migrated design can be further optimized compared to scaling work alone. References [1] Carlos, G.M., Marcio, C.S., and Rafael, M.C.: “Resizing rules for MOS analog-design reuse”, IEEE Design & Test of Computers, 2002, vol. 19, no. 3, pp. 50-58 [journal/ periodicals] [2] Savio, A., Colalongo, L., Kovacs-Vajna, Z.M., Quarantelli, M.: “Scaling rules and parameter tuning procedure for analog design reuse in technology migration”, Int. Symp. Circuits and Systems (ISCAS), 2004, pp. 117- 120 [conference proceedings] [3] Lekkas, P.: “Network on Chip”, Springer, 2004. [book] [4] Altera, “Stratix Handbook”, www.altera.com/docs/stratix_handbook.pdf. Last access: June 2012. [web]