* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download PNIMNiPE_nr56

Survey

Document related concepts

Schmitt trigger wikipedia , lookup

Josephson voltage standard wikipedia , lookup

Radio transmitter design wikipedia , lookup

Operational amplifier wikipedia , lookup

Integrated circuit wikipedia , lookup

Regenerative circuit wikipedia , lookup

Index of electronics articles wikipedia , lookup

Current mirror wikipedia , lookup

Valve RF amplifier wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Opto-isolator wikipedia , lookup

RLC circuit wikipedia , lookup

Surge protector wikipedia , lookup

Power electronics wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Transcript

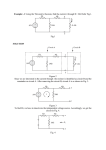

Nr 63 Prace Naukowe Instytutu Maszyn, Napędów i Pomiarów Elektrycznych Politechniki Wrocławskiej Nr 63 Studia i Materiały Nr 29 2009 Dual axes drive, Voltage Source Inverter, short circuit protection of paralleled MOSFETs Radoslaw NALEPA*, John MUCKIAN*, Hagai LEVY*, Maurice KEARNEY* DESIGN OF HIGH CURRENT FAST SWITCHING POWER STAGE FOR PMSM SERVODRIVES Practical design and implementation of high performance and high reliability, dual axes, MOSFETs based Voltage Source Inverter (VSI) for two 28V/500Apk PMSMs is presented in this paper. An existing drive system based on IGBTs was used as the start point for this work. New power end is presented in brief. Main parasitic components of the power amplifier are identified and discussed. Locations for a standard R and C snubber components are included. Simple and reliable short circuit protection solution for paralleled MOSFETs is presented and its performance is analyzed over wide operating temperature range. Design solutions and experimental results are included and discussed. 1. INTRODUCTION Nowadays more efficient, compact and cost effective solutions for electric drives are needed. Such demands may be satisfied once proven and reliable solutions are available in given area. At present power electronics updates seem to be an option for potential improvements. One obvious way to enhance overall performance of well proven IGBT based power stages is to use power MOSFET switches, which have lower conduction losses [3]. This is due to lower on-state resistance rDS(on) when compared with IGBTs, see Fig. 1. In addition their switching dynamics is higher – the rise/fall times (tr, tf) are shorter. This leads to reduced drives turn-on/off delays (td(on), td(off)) and in consequence improved overall “dynamic” performance. The facts were encouraging enough to trigger an activity aiming on update of an existing IGBT power amplifier of a PMSM drive system to a MOSFETs based one. _________ * MOOG Ltd., Ringaskiddy, Co. Cork, Ireland; e-mail: [email protected]. 2 0.016 rCE(on) [V] at 25°C VGS=10 [V] VGE=10 [V] 0.014 rCE(on) [V] at 125°C r(on) [Ohm] 0.012 0.01 0.008 rDS(on) [V] at 25°C 0.006 rDS(on) [V] at 125°C 0.004 0.002 0 0 100 200 300 i [A] 400 500 600 700 Fig. 1. On-state resistance of a MOSFET vs. an equivalent resistance of an IGBT. 2. The SYSTEM A task based on replacement of IGBTs with MOSFETs in dual axes, low voltage (28V/2x500A) PMSM drive system was undertaken. The final goals were set and prioritized as following: 1) Minimum design risk, 2) Improved controller efficiency, 3) The same level of short circuit protection as with IGBTs. a) +DC -DC +DC Csn Rsn Motor 1 PhaseA Csn Gate Drive Csn Rsn Csn Rsn Gate Drive Csn Gate Drive Rsn Csn Gate Drive -DC Gate Drive Rsn Csn Rsn Csn Gate Drive Rsn Motor 1 Phase C Rsn Motor 1 Phase B Gate Drive Gate Drive Csn +DC Gate Drive Motor 2 Phase A Gate Drive -DC Rsn +DC Csn -DC Rsn Csn +DC Rsn b) -DC Gate Drive Motor 2 Phase B Motor 2 Phase C Gate Drive Fig. 2. Simplified power-ends of: a) drive 1 VSI - two MOSFETs in parallel, two power modules sharing (phase B), b) drive 2 VSI - three MOSFETs in parallel, single power module sharing. 3 In order to achieve the 1st goal the mechanical layout of upgraded drive had to be as close as possible to the original one. This became troublesome from electrical point of view. Built dual power stage consists, in short, of an input filter, a single DC bus (power laminate) and two power ends, see Fig. 3. The power ends are made of paralleled low voltage (100V) MOSFETs in order to lower even more the on-state resistance of each switch. One VSI consists of in-module switches, see Fig. 2b, and the other one shares switches between two modules (1st design constraint), see Fig. 2a. Locations of the power modules arose from original system configuration with IGBTs (2nd design constraint). The 1st constraint caused difficulties in effective cycle-by-cycle short circuit protection of drive 1 at low temperature (-40C and below). The 2nd constraint created two troublesome circuit impedances, Z b=R+jXL, Fig. 4. Resultant circuit needed three different sets of RC snubber components. Additionally two dumping locations had to be identified, see Fig. 2. Drive 1 Drive 2 Fig. 3. Dual axes power stage – main components. +DC Z+b1 Z+b2 DRIVE 1 Phase A B C C in Z-b1 DRIVE 2 Phase A B C Z -b2 -DC Fig. 4. Simplified drive 1 and drive 2 VSI with major circuit parasitic impedances. 4 3. CIRCUIT PARASITIC COMPONENTS The power stage used contains unwanted parasitic components. The most influential ones present in the bus positive (Z+b1 & Z+b2) and the negative (Z-b1 & Z-b2) rails, Fig. 4, had negative impact on high speed switching performance, especially at low ambient temperature. To deal with them, first they were identified and combined in an equivalent circuit diagram. Such a circuit for a single phase (phase A only) of drive 2 can be seen in Fig. 5, where points A with A’ represent drive 1 terminals and B with B’ drive 2 terminals. Cc stands for a high frequency coupling capacitance. This capacitance is much smaller than that of electrolytic capacitors, Cin, shown in Fig. 3. For simplicity reason equivalent serial resistance and inductance, commonly known as esr and esl, of the two capacitances are not explicitly shown. In this case it can be assumed that they are blended in with parasitic resistance and inductance of the loop. Lb1 and Rb1 represent drive 1 bus parasitic inductance and resistance. Lb2 and Rb2 stand for parasitic inductance and resistance between drive 1 and drive 2 bus terminals. Ldu(l)A and Lsu(l)A represent combined parasitic inductance of paralleled upper (lower) MOSFET’s drain and source appropriately. Load is created by PMSM phases. A gate drive circuit is responsible for “on” and “off” commands. DC bus cap. L+b1 dr1 bus terminal L+b2 R +b1 +DC A Cc Cin dr2 phaseA driver L-b1 R-b1 R+b2 B LduA LsuA LdlA LslA A’ -DC dr2 bus terminal L-b2 Lload Rload R-b2 B’ Fig. 5. Phase A only, drive 2 dominant parasitic network equivalent circuit. 4. SNUBBER NETWORKS Once a prototype unit had been built work on dumping of parasitic resonances during switching started. Circuit presented in Fig. 5 helped to make right decisions about locations of the snubbing networks. 5 A simple dissipative RC voltage snubber had been selected for the first go and it proved to be effective. Values and power ratings of components were selected at room temperature following common practice [5]. Locations of terminals of snubbers were initially determined based on parasitic resonant network analyses from Fig. 5 and confirmed in a prototype. Drive 1 snubbers are connected directly across each switch, see Fig. 2a. Snubbers of drive 2 are connected across the bus, see Fig. 2b. They did not work effectively in the same configuration as for drive 1. 5. SHORT CIRCUIT PROTECTION The low on-state resistance can influence well-proven short circuit detection mechanism. IGBT’s protection circuit is based on a desaturation (DESAT) voltage monitoring by the IC, HCPL-316J isolated switch driver. Collector-emitter voltage, vCE, is sensed through a diode, see Fig. 6a. When the voltage on DESAT exceeds an internal reference voltage of 7V, while the IGBT is on, a fault is reported. The diode does not provide match between MOSFET’s vDS and the HCPL-316J DESAT level. Switch-on resistance can be as low as 500, which means that currents would have to be larger than 10kA before being interrupted. For this reason a new circuit based on an amplifier has been introduced, see Fig. 6b. a) b) C2 R2 Vcc+ R3 R D3 OpAmp D vC C HCPL-316JDESAT pin C3 D1 Vcc- HCPL-316JDESAT pin vE R1 D2 HCPL-316JVE pin D1 vS R1 R2 vD C2 HCPL-316JVE pin Fig. 6. Voltage sensing circuits: (a) IGBT’s VCE, (b) MOSFET’s VDS. Above circuit, Fig. 6b, provides gain and bandwidth control in the switch-on state. Components of the circuit were selected to provide short circuit protection in power module temperature range from –40C to +125C. Currents of both drives are limited to stay within 2.3kA (–40C) to 1.4kA (+125C) envelope. Example plots from opera- 6 tion can be seen in Fig. 7. In Fig. 7a vDS can be seen together with the OpAmp output voltage, coming out of saturation at the beginning of the on-time, followed by the DESAT voltage (increased by D3 forward voltage drop) after initial blanking time, tB, of the HCPL-316J IC. In Fig. 7b vDS and DESAT signals during normal (maximum current) operation at +60C can be seen. It must be noticed that there is a small distortion in steady state DESAT voltage from switching action in the rest of phases of both drives. That became a problem at low temperature, below -35C. Examples of short circuit currents with the DC bus voltage at the power laminate input terminal, at +60C ambient, can be seen in Fig. 8. a) b) Fig. 7. Drive 2: (a) phase to –DC short circuit condition at room temperature, (b) normal operation at +60C ambient. a) b) Fig. 8. Drive 1: (a) phase B to –DC short circuit current and the bus voltage at +60C, (b) phase B to phase C short circuit current and the bus voltage at +60C. 7 6. LOW TEMPERATURE OPERATION The prototype had proven to be fully functional at both room (+21C) and +60C (+125C power modules) temperatures. When the same test procedures were applied at –40C, at full current demand for both drives, DESAT faults of phase B of drive 1 appeared during normal operation (without a short circuit). From circuit signal analysis it became evident, that at low temperature loop resistance decreased making dominant electrical time constant, = L /R, of the drive 2 circuit larger. Drive 2 circuit transient currents were taking more time during switching-on and -off. This in the presence of the common impedance Zb1 became unacceptable. Changes of currents in drive 2 caused changes of voltages at the terminals of drive 1. It had the most harmful effect on phase B of drive 1 with split switching poles, see Fig. 2a. DESAT bandwidth set at room temperature was too high for those “slow” changes during on-state. In result the phase B DESAT voltage contained transient spikes exceeding fault levels. The OpAmp circuit gain and bandwidth together with HCPL-316J’s blanking time had to be readjusted. It worked but there was not enough margin. Two different solutions to that problem have been identified. First one was based on the power laminate modification with two additional double layer copper bars at drive 2 terminals between: 1st +DC phase C and +DC phase B, 2nd -DC phase C and DC phase B. Their inductance had to be lower than Lb2 in order to provide effective local power distribution path. Second solution is based on slower switching achieved by increase of the MOSFET’s gate resistors, results shown in Fig. 9. From system mechanical robustness point of view the second one is better. It is a compromise between design constraints and initially set project goals. Efficiency of the new system with paralleled MOSFETs is higher than with IGBTs, see Fig. 10. Fig. 9. Phase B of drive 1, normal operation at -40C at maximum current demand. 8 1.0 efficiency / max_efficiency 0.9 0.8 0.7 0.6 System based on IGBTs 0.5 0.4 0.3 System based on MOSFETs 0.2 0.1 0.0 0 50 100 150 200 250 300 350 PMSM phase current [Arms] Fig. 10. System performance comparison, /max = f (I). 7. CONCLUSIONS The project goals were achieved. As a result of using the original system platform designing time was minimized. The changes have not influenced reliability of the original system and its efficiency has been improved. Highly effective paralleled MOSFETs short circuit protection mechanism based on monitoring of the voltage across the on-state switch resistance has been proposed and successfully implemented. Behaviour of the protection circuit at low temperature has been discussed. REFERENCES [1] BOSE B. K. (Ed.), Power Electronics and Variable Frequency Drives – Technology and Applications, IEEE press, 1997 New York. [2] KRAH J.O., HOLTZ J, High-Performance Current Regulation and Efficient PWM Implementation for Low-Inductance Servo Motors, IEEE Transactions on Industry Applications, vol.35, No.5, Sep/Oct 1999. [3] MOHAN N., UNDELAND T.M., ROBBINS W.P. Power Electronics – Converters, Applications and Design, JohnWilay & Sons, Inc., 1995 New York. [4] REN Y., XU M. X., ZHOU J., LEE F. C., Analytical Loss Model of Power MOSFET, IEEE Trans. Power Electronics, vol.21, Mar. 2006, pp. 310-319. [5] TODD P.C., Snubber Circuits: Theory, Design and Application, Unitrode Corp., May 1993. [6] WINTERHALTER C., KERKMAN R., SHLEGEL D.W., LEGGATE D., The effect of Circuit Parasitic Impedance on the Performance of IGBTs in Voltage Source Inverters, IEEE Applied Power Electronics Conference (APEC’01), 4-8 March 2001, Anaheim, California, US.