* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Analysis and Design of Controllable Class E Low dv/dt Synchronous

Transformer wikipedia , lookup

Stepper motor wikipedia , lookup

Spark-gap transmitter wikipedia , lookup

History of electric power transmission wikipedia , lookup

Electrical ballast wikipedia , lookup

Three-phase electric power wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Electrical substation wikipedia , lookup

Stray voltage wikipedia , lookup

Distribution management system wikipedia , lookup

Surge protector wikipedia , lookup

Two-port network wikipedia , lookup

Transformer types wikipedia , lookup

Voltage optimisation wikipedia , lookup

Current source wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Power inverter wikipedia , lookup

Power MOSFET wikipedia , lookup

Mains electricity wikipedia , lookup

Schmitt trigger wikipedia , lookup

Voltage regulator wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Alternating current wikipedia , lookup

Mercury-arc valve wikipedia , lookup

Current mirror wikipedia , lookup

Buck converter wikipedia , lookup

Switched-mode power supply wikipedia , lookup

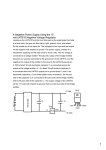

ECCTD’01 - European Conference on Circuit Theory and Design, August 28-31, 2001, Espoo, Finland Analysis and Design of Controllable Class E Low dv/dt Synchronous Rectifier Itsda Boonyaroonate* and Shinsaku Mori* Abstract -Class E synchronous rectifier regulating the output voltage at a fixed switching frequency is presented, analyzed and experimentally verified. This rectifier is derived from a class E low dv/dt rectifier by replacing a rectifier diode with a controlled switch. The rectifier is driven by a sinusoidal current source, and the output voltage is regulated by vary the conduction time of the controlled switch. The ZVS condition of a switch can be maintained from full-load to open-load operation. The experimental results measured at switching frequency 1 MHz were good agreement with the theoretical prediction.. isec 2 Circuit Operations Figure 1(a) shows the basic circuit of class E low dv/dt rectifier and (b) shows the proposed rectifier. The proposed rectifier consists of a transformer (T), switch (S1) with its body diode (D1), shunted capacitor (C1), output capacitor (Co) and the output load (RL) . C T i D N1 Lo Co RL + iC1 vC1 _ (a) isec Io N2 iD1 C1 iS1 D1 vg1 Co RL S1 (b) Figure 1: Class E low dv/dt rectifier. (a) Basic circuit. (b) Controllable synchronous rectifier. * Nippon Institute of Technology, Electrical and Electronics Engineering Dept, 4-1 Gakuendai Miyashiro Minamisaitama Saitama Japan 345-8501, email [email protected],Tel. 81-480-34-4111 ext. 698, Fax. 81-480-337680. θ -Io iS1+iD1 vg1 iC1 θ 2 π Dmin 2π D θ θ vC1 θ Figure 2: Idealized operating waveforms of class E controllable low dv/dt synchronous rectifier. 1 Introduction Class E zero-voltage switching rectifier [1]-[9] has been used in high-frequency converter circuits to reduce its size, weight, EMI noise and increase rectification efficiency. Many published papers [1][7] have been presented many topologies of the class E rectifier, in which the operating frequency is varied against the variation of load or line voltage. To avoid problems accompanied by variation of operating frequency, we present the current driven class E low dv/dt synchronous rectifier regulating the output voltage at a fixed switching frequency. φ The proposed rectifier is modified from the basic rectifier by replacing the rectifier diode (D) with the controlled switch (mosfet S1 with its body diode D1). The secondary coil inductance of the transformer (T) is to operate as the output choke (LO) forming the dc output current loop. The output voltage is filtered by first-order low-pass output filter, which is formed by the output capacitor (Co) and the load (RL). The filter attenuates the output voltage ripples, so that the output voltage (Vo) is supported approximately constant. Figure 2 shows the idealized operating waveforms of the proposed rectifier. The secondary coil current (isec) caused by the induced current from the driving input current (i’) and the output dc current (Io). The switch (S1) is driven by Vgs from 0 to 2 π D. The conduction time of switch (S1) begins at the time of the origin of the graph of Fig. 2, when the cathode of D1 reaches zero volts with respect to the anode, after having been positive with respect to the anode. The shunt capacitor (C1) shapes the voltage (vC1) across switch (S1) so that the switch turn-on and turn-off at zero-voltage. The control interval of D is Dmin ≤ D < 1 . The regulation of the output voltage can be described as follows. • D=Dmin: S1 and D1 conduct the negative current only. The conduction time of S1 is equal to the conduction time of D1 and Io is the maximum. • D=1: S1 and D1 conduct all cycle and Io equal zero. • Dmin ≤ D < 1:part of the positive current of iS1 flows through S1. The averaged current through S1 and D1 is between 0 and the values corresponding to D. I-301 i’ Io isec + iC1 vC1 _ C1 iS i’ i’ Io isec Vo Vo iS Io isec Vo iC1 (a) (b) (c) Figure 3: (a) Modeled of class E low dv/dt controllable synchronous rectifier, (b) when switch turn-on (c), when switch turn-off. 3. Circuit Analysis The analysis of the rectifier begins with the following assumptions. • The controlled switch (S1) and diode (D1) form an ideal switch. (S) • The transformer (T) is ideal and secondary inductance (LO) is large enough that the dc component current is constant and equals IO. • The rectifier is driven by an ideal sinusoidal current source (i). • The passive components in circuit are ideal. The driving input current (i’) of a rectifier is §N · i′ = ¨¨ 1 ¸¸ ⋅ i = I m cos(θ − φ ) © N2 ¹ (1) where N1,N2 are the number of transformer winding , i is the transformer primary current, Im is the current peak value, and φ is phase angle. If the transformer (T) is ideal, the induced current (i’) will be directly connected in parallel to equivalent dc current source (Io).The transformer secondary current is equal to (2) isec = − i′ + I o ( 2π (1 − D ) Im Because the secondary winding of the transformer has no dc voltage drop and the average value of vc1 is equal to Vo C1 S From (3), the boundary condition of C1 voltage when θ=2π is vc1(2 π )=0, yields I sin (2πD − φ ) + sin φ (6) M= O = VO = 1 2π 2π ³v C1 (7) dθ 2πD Rewrite the result of (7), then we have IO cos φ − cos (2πD − φ ) − (2πD − 2ωC 2 RL )sin (2πD − φ ) (8) =2 2 Im 4πωC 2 RL + 4π 2 (1 − D ) Solving φ by using (6) and (8), yields [ ] 2 ª º 4π 2 (1 − D ) − 4πωRL C2 sin 2πD + 4π (1 − D )(1 − cos 2πD ) φ = tan −1 « » 2 2 2 + − + 4π 2 (1 − D ) − 4πωRL C 2 cos 2πD + 4π (1 − D )sin 2πD ¼ ( ) 4 πω R C 4 π 1 D ¬ L 2 ( ) [ ] (9) The ac-to-dc current transfer function of rectifier is defined as 2I O I (10) K = O = = 2M I I Im where I is the rms value of input ac current. Substitute (9) into (10) and we obtain KI as function of ωC1RL and D shown in Fig. (4). Figure 5 shows the behavior of the maximum KI_max which occurred when ωC1RL= ωC1RLmin and D=Dmin. To obtain the relationship between ωC1RL and Dmin when KI_max occurred, we substitute D=Dmin in (6), θ=2πDmin in (5) and use the boundary condition of switch current iS(2πDmin)=0 in (5). We have phase angle φ when KI_max occurred as § sin 2πDmin + 2π (1 − Dmin ) cos 2πDmin · ¸¸ φ = − tan −1 ¨¨ © 1 − cos 2πDmin + 2π (1 − Dmin )sin 2πDmin ¹ ) (11) KI where Io is the dc component of secondary current and equal to the dc output current. The shunt capacitor voltage (vC1) is vC 2 = ω1C2 θ ³i sec ωC 2 RL dθ VO ª sin (θ − φ ) − sin (2πD − φ ) º (3) 2πD − θ − »¼ M ωC 2 RL «¬ where M=Io/Im and Io=Vo/RL. Since vS=vc1 and iS=i’+Io, the switch voltage and current waveforms normalized with respect to Vo and Io respectively expressed as = 0, vS ° =® 1 ª sin(θ − φ ) − sin(2πD − φ )º VO ° «2πD − θ − »¼, M ¯ωC2 RL ¬ cos(θ − φ ) iS °− 1 − =® M I O °̄ 0, D 0 2πD Figure 4: Plot KI as function of ωC1RL and D. ω C 2 R L min 0 < θ ≤ 2πD 2πD < θ ≤ 2π (4) Dmin 0 < θ ≤ 2πD 2πD < θ ≤ 2π (5) I-302 Figure 5: Relationship between ωC1RLmin and Dmin. VSM/VO,ISM/IO ISM/IO VSM/VO Dmin Figure 6: Normalized values of switch stress voltage and currents at any Dmin Substitute D=Dmin and ωC1RL= ωC1RLmin into (9), and solving ωC1RLmin from (9) and (11) yields ωC1RL min = 1 {(2π − 2πDmin )(2 sin 4πDmin + 4 sin 2πDmin ) 4π sin 2 2πDmin ( ) + 2(2π − 2πDmin ) (1 + cos 2πDmin ) − (2π − 2πDmin ) − 4 sin 2 2πDmin 2 2 } Table 1: Rectifier design parameters (12) We use this equation to select C1 and Dmin when the maximum load is given. We can see that, the maximum switch current occurred when θ = φ in (5). By substitution this angle in (5), we obtain I SM (2π − 2πDmin ) (13) = 1+ IO Ri/RLmin Dmin=0.6 Dmin=0.5 Dmin=0.4 Dmin=0.3 Dmin=0.2 Dmin=0.1 sin (2πDmin − φ ) + sin φ Similarly, the normalized switch stress voltage when KI_max occurred at any Dmin can be calculated by substitution θ = φ + π + cos −1 1 / M into (4). This yields Ci/C1 Dmin=0.6 VSM −1 {θ vS _ max − 2πDmin = VO ωC2 RL _ min Dmin=0.5 (2π − 2πDmin )(sin (θ vS _ max − φ ) − sin(2πDmin − φ ))½ (14) + ¾ sin (2πDmin − φ ) + sin φ ¿ The phase angle (φ) in (11) continues its sign in the range 0 ≤ Dmin ≤ 0.628 and will change in the sign inverse when out of this range; In practice, it is sufficient to use this range for design of the rectifier because the optimum circuit parameters occur around Dmin=0.5 (see Table 1). The ac-to-dc voltage transfer function (MR) of the rectifier is given by V I 1 . (15) = M = o = R VRi1 I O1 2M The equivalent input resistance (Ri) of the rectifier is Ri I O2 = = 2M 2 RL I 2 D (16) The fundamental component of equivalent input capacitance (Ci) voltage is expanded by using the Fourier series, yields v c1 = −V O + V Rim cos (θ − φ ) − VCim sin (θ − φ ) (17) where VRim and Vcim are the amplitudes of voltage across the equivalent input resistance (Ri) and capacitance (Ci) respectively. VCim is calculated by Dmin=0.2 Dmin=0.1 Dmin=0.4 Dmin=0.3 D Figure 7: Normalized input resistance Ri/RLmin and input reactance Ci/C1 versus Dmin when D is varied from Dmin to 1. 2π 1 (18) VCim = ³ vC 2 sin(θ − φ )dθ π 2πD I = m {[2π (D − 1)cos φ − sin φ − sin (2πD − φ )]M πω C 2 º½ 1 ª§ 1 · + «¨ − cos 2 φ ¸ sin 4πD − (1 − cos 2πD )sin 2φ cos 2πD + 2 sin 2πD cos 2 φ + 2π (1 − D )» ¾ 2 ¬© 2 ¹ ¼¿ The input reactance (Xci) at operating frequency is 1/ωCi or equal to Vcim/isec and from (18) the normalized equivalent input capacitance (Ci) respect to C1 can be expressed by Ci (19) = π /{[2π (D − 1) cos φ − sin φ − sin (2πD − φ )]M C1 º½ 1 ª§ 1 · + «¨ − cos2 φ ¸ sin 4πD − (1 − cos 2πD)sin 2φ cos 2πD + 2 sin 2πD cos2 φ + 2π (1 − D)» ¾ 2 ¬© 2 ¹ ¼¿ Figure 7 shows the normalized equivalent input resistance Ri/RLmin and the equivalent input reactance Ci/C1 versus Dmin when D is varied from Dmin to 1. After we known Ri and Ci, they will be transferred to the primary side of transformer by factor (N1/N2)2. I-303 the controlled switch (S). Figure 8 shows the operating waveforms when rectifier is driven by sinusoidal current 1A peak at frequency 1MHz. The duty ratio (D) of driving signal (Vgs) is equal to 0.5 (or D=Dmin) and loaded by resistor 25 Ω . The measured values are VO=13V, VSM=50V and ISM=1.54A. Figure 9 shows the output voltage control characteristic of the rectifier when the output load was fixed at 25 Ω , by vary the duty ratio (D) from 0.5 to 1, the output voltage is decrease from 13V to 0V. Figure 10 shows the voltage regulation characteristic of the rectifier. By varying the duty ratio (D) from 0.5 to 0.585, the output voltage can be maintained at 13V when the output load was changed from RL/RLmin=1 to 100. Figure 8: Rectifier operating waveforms at 1MHz. (ch.1 i 1A/div, ch.2 isec 1A/div, ch.3 vg1 , ch.4 vs1 ; horizontal 400nS/div.) Vo 6. Conclusion The controllable class E low dv/dt synchronous rectifier can regulate the output voltage at fixed switching frequency by control the conduction angle or duty ratio. The switching is satisfied with zerovoltage switching condition from full-loaded to openloaded D Figure 9: Output voltage control characteristic. D 7. Acknowledgments This work was partly supported by NTT and International communication foundation ICF Japan. References RL/RLmin [1] Figure 10: shows the output voltage regulation characteristic. [2] 4. Design example [3] To show the design example of the proposed rectifier, a resistor RL=25 Ω is given for the maximum output load. The class D inverter operates at switching frequency 1MHz with Q=10 with output current 1 A peak is used as the sinusoidal current source (i). From Table 1, we select Dmin=0.5, we have ωC1RLmin=0.319, ISM/IO =2.863, VSM/VO=3.650, Ri/RLmin=0.576, Ci/C= 4.717, KI=0.759, MR=1.318 and ωC1(VO/Im) =0.171. The rectifier parameters are C=2.03nF, IO=0.5367A, VO=13.417V, Ri=14.4 Ω , Ci=9.575nF, VSM=48.97V and ISM=1.534A. [4] [5] [6] [7] [8] 5. Experimental results [9] In experimentation, the high-frequency transformer with N1=N2 with secondary coil inductance (LO) equal 100uH is used as T, capacitor 4.7uF as the output capacitor (CO) and a Mosfet IRL640 is used as I-304 M. K. Kazimerczuk and J. Jozwik, “Class E Zero-VoltageSwitching Rectifier with a Series Capacitor,” IEEE Trans. Circuits Syst., vol.36, No. 6, pp. 926-928, June. 1989. M. K. Kazimerczuk and J. Jozwik, “Class E Zero-VoltageSwitching and Zero-Current-Switching Rectifiers,” IEEE Trans. Circuits Syst., vol.37, No. 3, pp. 926-928, June. 1989. M. K. Kazimerczuk, “Analysis of Class E Zero-VoltageSwitching Rectifier,” IEEE Trans. Circuits Syst., vol.37, No. 6, pp. 747-755, June. 1990. A. Ivascu, M. K. Kazimerczuk, and S. B. Galateanu, “Class E Resonant Low dv/dt Rectifier,” IEEE Trans. Circuits Syst., vol.39, No. 8, pp. 604-613, August. 1992. M. Mikolajewski and M. K. Kazimerczuk, “Zero-VlotageRipple Rectifiers and DC/DC Resonant Converters,” IEEE Power Electronics., vol.8, No. 1, pp. 12-17, Jan. 1993. M. K. Kazimerczuk, B. Tomescu and A. Ivascu, “Class E Resonant Rectifier with a Series Capacitor,” IEEE Trans. Circuits Syst., vol.41, No. 12, pp. 885-890, June. 1994. S. B. Galateanu and Jean-Louis Cocquerelle, “Class E Halfwave Low dv/dt Rectifier Operating in a Range of Frequencies Around Resonance,” IEEE Trans. Circuits Syst., vol.42, No. 2, pp. 83-94, Feb. 1995. M. Fujii, T. Suetsugu, K. Shinoda and Shinsaku Mori, “Class-E Rectifier Using Thinned-Out Method,” IEEE Power Electronics., vol.12, No. 5, pp. 832-836, Sep. 1997. M. K. Kazimerczuk and K. Puczko, “Class E Low dv/dt Synchronous Rectifier with Controlled Duty Ratio and Output Voltage,” IEEE Trans. Circuits Syst., vol.38, No. 10, pp. 11651172, Oct. 1991.