* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

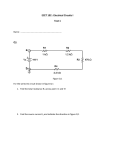

Download characterization, modeling, and design of esd

Ground (electricity) wikipedia , lookup

Power inverter wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Fault tolerance wikipedia , lookup

Electrical ballast wikipedia , lookup

History of electric power transmission wikipedia , lookup

Electrical substation wikipedia , lookup

Electromagnetic compatibility wikipedia , lookup

Two-port network wikipedia , lookup

Voltage regulator wikipedia , lookup

Earthing system wikipedia , lookup

Power electronics wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Voltage optimisation wikipedia , lookup

Current source wikipedia , lookup

Thermal runaway wikipedia , lookup

Stray voltage wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Semiconductor device wikipedia , lookup

Buck converter wikipedia , lookup

Mains electricity wikipedia , lookup

Alternating current wikipedia , lookup

Opto-isolator wikipedia , lookup

Network analysis (electrical circuits) wikipedia , lookup