* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Diagnosing Integrator Leakage of Single-Bit First

Three-phase electric power wikipedia , lookup

Buck converter wikipedia , lookup

Stray voltage wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Electromagnetic compatibility wikipedia , lookup

Schmitt trigger wikipedia , lookup

Opto-isolator wikipedia , lookup

Rectiverter wikipedia , lookup

Analog-to-digital converter wikipedia , lookup

Automatic test equipment wikipedia , lookup

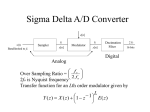

Diagnosing Integrator Leakage of Single-Bit First-Order ∆Σ Modulator Using DC Input Xuan-Lun Huang, Chen-Yuan Yang, and Jiun-Lang Huang Graduate Institute of Electronics Engineering Department of Electrical Engineering National Taiwan University Taipei 10617, Taiwan Email: [email protected] Abstract—Integrator leakage is a dominant factor in the SNR (signal-to-noise ratio) loss of ∆Σ modulators. In this paper, we propose a Design-for-Test (DfT) technique to diagnose the integrator leakage of the single-bit first-order ∆Σ modulator. The proposed technique is a low-cost solution; it only adds two multiplexers to the modulator, utilizes a single DC voltage as the test stimulus, and estimates the integrator leakage by analyzing the digitized bit stream. Furthermore, the technique can be easily extended to higher order ∆Σ modulators. Simulation results show that accurate estimations of the integrator leakage can be achieved even at the presence of noise. Keywords—analog/mixed-signal testing, diagnosis, design-for-test (DfT), ∆Σ modulation, integrator leakage. I. I NTRODUCTION ∆Σ modulation is a popular analog-to-digital converter (ADC) technique, especially for audio and communication applications that require high-resolution analog-to-digital interfaces. Due to its simple configuration and oversampling nature, a ∆Σ modulator can tolerate relatively high process variations and matching inaccuracy without failing its functionality. Therefore, ∆Σ modulation is an attractive solution when the ADC has to be integrated with other digital components, for example, in a System-on-Chip (SOC) design. In [1] [2], it is shown that the one-bit ∆Σ modulator is an area efficient solution to response extraction for analog/mixed-signal circuit Built-In Self-Test (BIST). Testing high-resolution ∆Σ modulators is a challenging task. First, it is difficult to generate the required high-quality test stimulus that has better resolution than the modulator under test (MUT). Second, output data analysis usually requires complex DSP (digital signal processing) operations, e.g., fast Fourier transform for dynamic performance characterization, which incur high computation complexity or need large memory storage. Over the years, several works have been proposed to facilitate ∆Σ modulator testing. In [3], Huang and Cheng propose to use a slow ramp as the test stimulus to estimate the ∆Σ modulator performance. While it needs no MUT modification and employs simple DSP operations to extract the MUT characteristics, it is limited by the required high-quality ramp signal. To relax the stringent requirements on the test stimulus, [4]–[7] propose to stimulate the MUT with digital bit sequences. In [4], the authors introduce an extra delay to the DAC (digital-to-analog converter) feedback path and use a periodic digital sequence as the test stimulus. From the output bit stream, the integrator leakage is derived; however, the added delay may itself contribute to the leakage, which affects the estimation results. [5]–[7] encode the sinusoidal waveform with a software ∆Σ modulator and use the resulting digital bit sequence as the test stimulus. The limitation is that the needed digital resources to generate or store the bit sequences may be unavailable. In this paper, we present a low-cost Design-for-Test (DfT) technique to diagnose the integrator leakage of a single-bit first-order ∆Σ modulator. Integrator leakage is a dominant factor in ∆Σ modulator performance, e.g., SNR (signal-tonoise ratio) [8]. Thus, leakage diagnosis and characterization help speed up the design and process tuning process, and may be included in the manufacturing testing. Note that, although demonstrated using the single-bit first-order modulator, the proposed leakage diagnosis technique can be easily extended to high-order configurations. The proposed integrator leakage testing method is based on integrator charging/discharging. It is an iterative three-phase approach. In phase I, the integrator is charged with a constant DC input to reach a stable, leakage-dependent voltage level. In phase II, the integrator is gradually discharged. The time it takes to discharge the integrator is recorded and used to derive the integrator leakage. In phase III, it is determined whether a new iteration can be executed to further enhance the characterization accuracy. Simulation results show that (1) the maximum leakage estimation error is below 0.4% at the presence of noise, and (2) it takes no more than 4 iterations for the test results to converge. The advantages and contributions of the proposed technique are as follows. 1) The required DfT circuitry is minimal; this reduces the incurred modulator performance and area overhead. In general, two analog multiplexers are needed; in some cases, no modification is needed at all. 2) Test stimulus generation is easy and the stored output response is minimal. The only test stimulus is a DC voltage whose value does not have to be very accurate; the recorded output response, on the other hand, is simply the time it takes to fully discharge the integrator. Fig. 1. The single-bit first-order ∆Σ modulator. Fig. 2. Thus, the proposed technique is also a feasible on-chip solution. 3) The leakage amplification technique is developed to facilitate the observation of leakage factors that are close to 1 (which corresponds to an ideal integrator). Leakage amplification also allows us to apply the same DC stimulus to observe all leakage factors. This paper is organized as follows. In Section II, we briefly review the operation principle of the single-bit first-order ∆Σ modulator and the integrator leakage effect. In Section III, we illustrate the proposed technique. Simulation results are given in Section IV and we conclude this paper in Section V. II. P RELIMINARIES A. The single-bit first-order ∆Σ modulator Fig. 1 depicts the block diagram of a single-bit first-order ∆Σ modulator. It consists of one integrator, one comparator, and one DAC in the feedback loop [9]. The multiplying factor p is the integrator’s leakage factor; for an ideal integrator, p = 1. The behavior of the ideal ∆Σ modulator is described by the following equations: yi+1 xi = = xi + yi vi − ei (1) (2) where yi is the integrator state, ei is the DAC output, and vi is the discrete time sample of the modulator input. If yi ≥ 0, the comparator output is 1 and the DAC output equals Vref (the reference voltage of the DAC); otherwise, the comparator output is 0 and the DAC output becomes −Vref . B. The effect of leaky integrator Due to finite op-amp gain, any practical realization of the integrator is leaky [10]. The leaky integrator is modeled by adding a leakage factor p < 1 to the integrator’s feedback path. The behavior of a leaky integrator is described by yi+1 = xi + p · yi (3) From (3), the leakage causes the integrator state to decay with a factor of (1 − p); this introduces non-linearity to the modulator’s I/O transfer curve. Shown in [10], [11], it prolongs the limit cycle effect and causes the modulator to output the same code for a continuous input range. The proposed DfT ∆Σ modultor III. T HE P ROPOSED L EAKAGE T ESTING T ECHNIQUE A. The DfT ∆Σ modulator The test circuitry needed to realize the proposed leakage testing technique depends on the MUT’s implementation. No modification is needed at all if the DAC reference voltage and analog ground of the MUT are both provided externally. On the other hand, if both are generated internally, two multiplexers are needed as shown in Fig. 2. The input side multiplexer allows us to zero the MUT input; this is accomplished by connecting vi to the internal analog ground. The DAC side multiplexer allows us to switch the DAC reference voltage among the normal value, the analog ground, and the MUT input. Note that the sole DC test stimulus may be implemented on chip for BIST applications; this is feasible because the proposed leakage testing method does not require knowing the exact value. B. The test flow The proposed integrator leakage testing flow is illustrated in Fig. 3. An iterative approach is adopted; the reason is to ensure high test quality. Each iteration consists of three phases: integrator charging, integrator discharging, and leakage amplification adjustment. 1) Phase I: Integrator charging: In this phase, the normal feedback path of the MUT is broken by zeroing the feedback signal ei ; this is accomplished by connecting the DAC reference voltage to analog ground. Under this configuration, the integrator integrates only the input voltage vi , which is set to a constant DC voltage. A leakage amplification technique is applied to accentuate the leakage effect; this facilitates the observation of close-to-unity leakage factors. Due to leakage, the integrator state yi will eventually stabilize at a leakagedependent voltage—leakage amplification ensures that the integrator is not saturated. 2) Phase II: Integrator discharging: In this phase, yi is implicitly measured. To accomplish this, we zero vi and use the DC input in phase I as the DAC’s reference voltage; this causes the integrator to be gradually discharged. The time it takes to discharge the integrator to zero is recorded; from the discharging time, the leakage factor can be derived. 3) Phase III: Leakage amplification adjustment: This phase is intended to improve the test accuracy by adjusting the leakage amplification factor (m). From the leakage factor (p) Although p can be derived from (11) if ys can be measured, this requires internal or external analog-to-digital conversion and is not adopted in our technique. Note that, from (11), C must be small enough so as not to saturate the integrator. For example, with p = 0.999 and an integrator saturation voltage of 1 V, C must be less than 1 mV. Such a small DC input is problematic; for example, a 1 mV offset in C will double ys and saturate the integrator. To solve this dilemma, we propose the leakage amplification technique; it accentuates the leakage effect so that we can avoid saturating the integrator regardless of the DC input value C. The way to realize leakage amplification is as follows: in each period of l = m+1 cycles, vi is switched to C in the first cycle and to the analog ground for the remaining m cycles. m is called the leakage amplification factor. With the leakage amplification technique, the stabilized integrator state ys now becomes: Fig. 3. The proposed test flow. y1 derived in phase II, the m that maximizes the test accuracy is computed. If it is smaller than the current value, a new iteration starts; otherwise, the leakage test process terminates. Note that a fairly large m is used at the beginning (m0 = 100); this ensures that the integrator is not saturated. In general, m keeps decreasing; it takes only a few iterations for m to converge (at most 4 in our experiments). In the following, we will give the details of the three phases. yl+1 y2l+1 ynl+1 = u (12) = C ·p +p ·u = C · pm + C · p2m+1 + p2l · u .. . C · pm (1 − pn(1+m) ) = + pnl · u 1 − p1+m m ys y1 y2 = u = C +p·u (4) (5) y3 = C + p · C + p2 · u .. . = C + p · C + · · · + pn−2 · C + pn−1 · u ( ) C · 1 − pn−1 = + pn−1 · u 1−p (6) (7) (8) It is easy to show that, for a leaky integrator, i.e., p < 1, yi will eventually reach a stable value ys : = = = lim yn n→∞ lim n→∞ C 1−p ( (15) = lim ynl+1 (16) C ·p 1 − p1+m (17) n→∞ m During phase I, the feedback from DAC is zeroed, i.e., ei = 0, and the integrator is charged with a constant DC input, i.e., vi = C. (Without loss of generality, we assume that C > 0 with respect to the analog ground in the following discussion.) Assuming that the initial state of the integrator is u, and the DC input is C, i.e., xi = C, the integrator state at clock cycle n can be derived as below. ys (13) (14) Similar to the case without leakage amplification, given sufficient time, a leaky integrator will reach a stable value ys : C. Phase I: Integrator charging yn l (9) ) n−1 C · 1−p 1−p + pn−1 · u (10) (11) = From equation (17), it is easy to see that one can reduce ys by increasing m; this implies that the same DC test voltage C can be used regardless of the actual leakage factor. D. Phase II: Integrator discharging In this phase, ys is implicitly measured; the proposed approach is to discharge the integrator and record the time it takes for the integrator state to becomes negative. (ys is positive because a positive DC test input C is used.) To facilitate integrator discharging, the DAC reference voltage is switched to C and the MUT input is zeroed. In this configuration, we have { p · yi − C if yi ≥ 0 yi+1 = (18) p · yi + C if yi < 0 At the beginning the integrator state yi is positive; thus, the MUT output bit is 1 and the integrator is discharged. As long as yi remains positive, the discharging process continues. However, once yi becomes negative, the integrator enters an oscillation state and its output toggles between 1 and 0. Let k be the length of the discharging duration. k satisfies the following constraints: yk+1 < 0 and yi > 0, ∀i < k. In phase II, the MUT output is monitored and k, the length of the 1’s run, is recorded. Fig. 4. Timing diagram of the proposed technique. Since yk > 0 and yk+1 = p · yk − C < 0, we have 0 < yk < C/p. If C is small enough, yk is approximately zero; thus, we have yk = −C · (1 − pk−1 ) C · pm · pk−1 + ≈0 1−p 1 − p1+m (19) which can be reduced to pm+k−1 − 2pm+k + pm+1 + pk−1 − 1 ≈ 0 (20) It is interesting that C does not appear in (20); this means that we do not need to know the exact value of C. Since m is user-controlled and k has been recorded in the discharging process, the leakage factor p can be derived from (20). To enhance the accuracy of ys measurement, a smaller C is preferred; however, note that the problem that “a smaller C can easily cause the integrator to saturate due to variation” is eliminated by leakage amplification. An example timing diagram of the integrator charging/discharging process is shown in Fig. 4. In this example, p = 0.985, m = 3, and C = 50 mV. During phase I, vi is periodically switched between 0 and C; this gradually charges yi until it stabilizes. In phase II, the integrator is discharged. After the charging process, the integrator oscillates; this can be observed from yi and Dout . E. Phase III: Leakage amplification adjustment In phase III, the leakage amplification factor m is adjusted to enhance the test accuracy. The choice of m is subject to the following two factors. 1) m must be sufficiently large so that ys is smaller than the integrator saturation voltage S; this is described by the following constraint: ys = C · pm <S 1 − p1+m (21) 2) Without violating (21), m should be as small as possible to enhance the test accuracy. When deriving p from (20), one can achieve higher accuracy if k is larger; this can be accomplished by using a smaller m which, according to (17), corresponds to higher ys and accordingly larger k. Since p is unknown, an iterative approach is adopted to find the best m. Our strategy is to start with a large leakage amplification factor m0 = 100. Then, in phase III of each iteration, we find the smallest m that satisfies (21) (with p substituted with value derived in phase II). If m cannot be further reduced, the test process is terminated; otherwise, a new iteration is executed with the updated m. In our simulation results, m converges in no more than 4 iterations. F. Discussions Although we demonstrate the leakage diagnosis technique using the single-bit first-order ∆Σ modulator, the technique is applicable to higher-order ∆Σ modulator configurations. In practice, as shown in Fig. 2, leakage diagnosis is possible if one can control the integrator’s input and observe the integrator’s digitized output (by the comparator). Thus, for higher-order ∆Σ modulator, the proposed technique can be applied after properly adding input multiplexers and digital observation points to the integrators. IV. S IMULATION R ESULTS Numerical simulations using Matlab are performed to validate the proposed leakage testing technique. The single-bit first-order ∆Σ modulator uses an integrator with unit gain and a saturation voltage of S = 1.2V . The DC test stimulus is C = 50 mV. The charging duration must be long enough for the integrator to stabilize; it is set to be 150 × (m + 1) in our experiment. Finally, the initial leakage amplification factor is m0 = 100. Fig. 5. Simulation results for leakage evaluation. Fig. 5 shows the test results for leakage factor (p) from 0.95 to 0.999. In the top plot, the x and y-axis correspond to the injected and measured leakage, respectively; “◦” and “×” represent the test results and actual values, respectively. This plot clearly shows that the test results match the actual values very well. The lower plot of Fig. 5 shows the test error. In general, higher test accuracy is achieved when p is close to unity. The maximum error is 0.27% when p = 0.957. Table I shows more detailed information. In this table, columns 1 and 2 are the injected and measured leakage factors, column 3 the test error, column 4 the final leakage amplification factor, column 5 the number of iterations, and column 6 the total test time. As we have expected, larger m is needed as p approaches unity. All the tests are completed within 4 iterations. In the following, experiments that consider circuit and test stimulus noise are conducted to validate the robustness of the proposed technique. A. Operational amplifier and switch noise The thermal noise associated with the sampling switches and the intrinsic noise of the operational amplifier (opamp) have substantially affects the ∆Σ modulator performance [12]. Their impact on the proposed technique is examined in the following experiments. As √shown in Table II, the sampling switch noise is modeled by KT /Cs and the opamp noise is modeled by Vn,out ; they are caused by flicker noise and wide-band thermal noise. Typical parameter values are used to derive the noise which is listed in column 3. The test results are shown in Fig. 6 which is nearly Fig. 6. Test results considering opamp and switch noise. TABLE I D ETAILED L EAKAGE T ESTING R ESULTS Injected Leakage Measured Leakage Estimation Error m # iterations Test Time (Clk Cycle) 0.995 0.990 0.985 0.980 0.975 0.970 0.965 0.960 0.955 0.950 0.99507 0.99001 0.98497 0.97966 0.97472 0.97112 0.96632 0.95961 0.95625 0.94993 6.5626 e-05 1.4671 e-05 -2.6120 e-05 -3.3657 e-04 -2.8264 e-04 1.1155 e-03 1.3171 e-03 -3.9281 e-04 1.2506 e-03 -7.1600 e-05 8 4 2 2 1 1 1 1 0 0 3 3 3 3 3 3 3 3 3 3 18193 16837 16533 16526 16376 16373 16370 16368 16223 16221 identically to Fig. 5; the explanation is that the injected noise tends to average out to zero during the long charging and discharging process. B. DC test input noise This experiment analyzes the impact of the noise associated with the DC test stimulus C. A Gaussian noise with variance TABLE II N OISE M ODEL AND VALUES Noise Source Function √ Sampling switches noise Op-amp noise Value KT Cs 32.171 µV Vn,out 60.76 µV Fig. 7. Test results considering opamp, switch, and test stimulus noise. of 5 mV is injected to the 50 mV DC test stimulus. Fig. 7 shows test results with test stimulus noise, switch noise, and op-amp noise injected. It shows that, in the existence of large input stimulus noise, the error is still under 0.3%. C. Comparator Offset The comparator offset, if existent, may elongate or shorten the discharging process depending on its polarity. To assess the impact of comparator offset on leakage estimation, a 10 mV comparator offset is injected; the results are shown in Fig. 8—the maximum leakage estimation error is 0.36%. D. Considering all of the noise Finally, in the experiment when circuit noise, DC input noise, and comparator offset are all injected, the maximum error is 0.0023; this shows the robustness of the proposed technique. V. C ONCLUSION We have presented a low-cost yet accurate leakage factor testing technique for the single-bit first-order ∆Σ modulator. First, only two multiplexers are required to realize the proposed testing technique. In some cases, no modification is needed at all. Second, only one DC test stimulus is used and its exact value need not be known. These make the proposed technique also a viable BIST solution and can be easily extended for higher order ∆Σ modulators. The measured leakage factor can be used to predict SNR performance. Simulation results show that very high accuracy is achieved even in the existence of circuit and input stimulus noise. Currently, a prototype is being designed for silicon validation. Fig. 8. Test results considering comparator offset. R EFERENCES [1] J.-L. Huang and K.-T. Cheng, “A sigma-delta modulation BIST scheme for mixed-signal circuits,” in Asia and South Pacific Design Automation Conference, 2000, pp. 605–610. [2] H.-C. Hong, J.-L. Huang, K.-T. Cheng, C.-W. Wu, and D.-M. Kwai, “Practical considerations in applying sigma-delta modulation-based analog bist to sampled-data systems,” IEEE Transactions on Circuits and Systems II, vol. 50, no. 9, pp. 553–566, Septmber 2003. [3] J.-L. Huang and K.-T. Cheng, “Testing and characterization of the onebit first-order delta-sigma modulator for on-chip analog signal analysis,” in IEEE International Test Conference, Oct. 2000, pp. 1021–1030. [4] G. Leger and A. Rueda, “A digital test for first-order Σ∆ modulators,” in IEEE Design, Automation and Test in Europe Conference and Exhibition, Feb. 2004, pp. 706–707. [5] C.-K. Ong and K.-T. Cheng, “Self-testing second-order delta-sigma modulators using digital stimulus,” in IEEE VLSI Test Symposium, May 2002, pp. 123–128. [6] L. Rolı́ndez, S. Mir, A. Bounceur, and J.-L. Carbonéro, “A SNDR BIST for Σ∆ analog-to-digital converters,” in IEEE VLSI Test Symposium, May 2006, pp. 314–319. [7] L. Rolı́ndez, S. Mir, J.-L. Carbonéro, D. Goguet, and C. Nabil, “A stereo audio Σ∆ ADC architecture with embedded SNDR self-test,” in IEEE International Test Conference, Oct. 2007, pp. 1–10. [8] F. Medeiro, B. Pérez-Verdú, and A. Rodrı́guez-Vázquez, Top-down design of high performance sigma-delta modulators. Kluwer Academic, 1999. [9] S. Ardalan and J. Paulos, “An analysis of nonlinear behavior in deltasigma modulators,” IEEE Transactions on Circuits and Systems, vol. 34, pp. 593–603, Jun. 1987. [10] O. Feely and L. O. Chua, “The effect of integrator leak in Σ − ∆ modulation,” IEEE Transactions on Circuits and Systems, vol. 38, no. 11, pp. 1293–1305, Nov. 1991. [11] V. Friedman, “The structure of the limit cycles in sigma-delta modulation,” IEEE Transactions on Communication, vol. 36, no. 8, pp. 972–979, Aug. 1988. [12] P. Malcovati, S. Brigati, F. Francesconi, F. Maloberti, P. Cusinato, and A. Baschirotto, “Behavioral modeling of switched-capacitor sigma-delta modulators,” IEEE Transactions on Circuits and Systems, vol. 50, pp. 352–364, Mar. 2003.