* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Document

Pulse-width modulation wikipedia , lookup

Power inverter wikipedia , lookup

Power engineering wikipedia , lookup

Stepper motor wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Three-phase electric power wikipedia , lookup

Electrical ballast wikipedia , lookup

Electrical substation wikipedia , lookup

History of electric power transmission wikipedia , lookup

Schmitt trigger wikipedia , lookup

Shockley–Queisser limit wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Optical rectenna wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Stray voltage wikipedia , lookup

Voltage regulator wikipedia , lookup

Current source wikipedia , lookup

Power MOSFET wikipedia , lookup

Alternating current wikipedia , lookup

Distribution management system wikipedia , lookup

Voltage optimisation wikipedia , lookup

Mains electricity wikipedia , lookup

Surge protector wikipedia , lookup

Network analysis (electrical circuits) wikipedia , lookup

Buck converter wikipedia , lookup

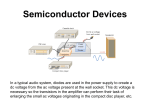

Chapter 2 DIODE MENJANA MINDA KREATIF DAN INOVATIF Introduction Biasing pn junction Load line concept & graphical analysis Diode Resistance Diode Model Review on PN Junction With the formation of the p and n materials combination of electrons and holes at the junction takes place. This creates the depletion region and has a barrier potential. This potential cannot be measured with a voltmeter but it will cause a small voltage drop. Forward Bias Voltage source or bias connections are + to the p material and – to the n material. Bias must be greater than 0.3 V for Germanium or 0.7 V for Silicon diodes. + - Negative side of bias voltage ‘pushes’ The electrons moves to the external circuit free electrons towards pn junction, and across it into the p region, & combine with becoming conducting electrons in metal. holes. As more electrons move into the depletion Positive side of voltage bias attracts the region, the number of + ions is reduced. valence electrons toward the end of p As more holes move into the depletion region region, holes providing the path. on the other side, the number of - ions is also reduced. The depletion region narrows. Holes appear to move towards the junction. Forward Bias FIGURE :A forward-biased diode showing the flow of majority carriers and the voltage due to the barrier potential across the depletion region. Reverse Bias Voltage source or bias connections are – to the p material and + to the n material. Bias must be less than the breakdown voltage. Positive side of battery pulls the free electrons, (majority in n ) away from the junction. As electrons move away from junction, more positive are created. In p region, electrons from negative side of battery enter as valence electrons. It moves from hole to hole toward the depletion region, creating more negative ions. This can be viewed as holes being pulled towards the negative side. The depletion region widens. The electric field increases in strength until the potential across depletion region equals the bias voltage. Only a very small reverse current Exist. Current flow is negligible in most cases. Reverse Bias FIGURE : The diode during the short transition time immediately after reversebias voltage is applied. Reverse breakdown voltage Reverse current is normally small and can be neglected. They result from movement of minority carriers. But if applied voltage is bigger than the breakdown voltage, the current will increase drastically. The high reverse biased voltage, imparts energy to the free minority electrons so that they speed through the p region. They collide with atoms with enough energy to knock valence electrons out of orbit into the conduction band. These electrons have high energy, and repeat the process, & they quickly multiply. They have high energy to move though pn junction, & not combine with holes. Known as avalanche – results in high reverse current Forward bias measurement Current & Voltage in a forward biased pn junction Figure: Forward-bias measurements show general changes in VF and IF as VBIAS is increased. Structure & Symbol Diodes packages LED (Light Emitting Diode) Signal Diode Zener diode Power Diode FIGURE :Typical diode. Diode Operating Conditions No Bias No external voltage is applied : VD = 0V No current is flowing: ID = 0A Only a modest depletion layer exists Diode Operating Conditions Forward Bias External voltage is applied across the p-n junction in the same polarity as the p-type and ntype materials. The forward voltage causes the depletion layer to narrow. The electrons and holes are pushed toward the p-n junction. The electrons and holes have sufficient energy to cross the p-n junction. Diode Operating Conditions Reverse Bias External voltage is applied across the p-n junction in the opposite polarity of the p-type and n-type materials. The reverse voltage causes the depletion layer to widen. The electrons in the n-type material are attracted toward the positive terminal. The holes in the p-type material are attracted toward the negative terminal. Forward bias a) Circuit connections showing the diode symbol. b) V-I characteristic Reverse Bias a) Circuit connections showing the diode symbol. b) V-I characteristic Ideal Diode equations A fit to the I-V characteristics of a diode yields the following equation, known as the ideal diode equation or the Shockley equation: VT = 26 mV when T = 300K, room temperature. η=1 for Ge; η= 2 for Si x The y intercept is equal to IS. The slope is proportional to 1/η. When η = 1, ID increased by approximately one order of magnitude for every 60 mV increase in VD. Example Plot the I-V characteristic for a silicon diode where IS=25nA at room temperature (25°C) Answer η = 2(silicon); IS=20nA; VT =26mV If VD =0.4V, = 0.04mA VD(V) 0.8 0.6 0.4 0.2 0 -0.1 -1.0 -100 VD(A) 120m 2.56m 0.04m 0.0011m 0 -21.25n -25n -25n Cont.. Answer Introduction Biasing pn junction Load line concept & graphical analysis Diode Resistance Diode Model Load Line Concept Simple diode circuit where ID and VD are not known. A simple analysis which used the diode characteristic to obtain the Q-point (operation point) Graphical Analysis Technique Load Line concept Kirchoff Voltage Law: VD = VPS – IDR On x-axis, ID = 0 ; => VD = VPS On y-axis, VD = 0; => ID = VPS/R In this case, When ID = 0, VD = 5V and When VD = 0, ID = (5/2k) = 2.5 mA Graphical Analysis Technique Load Line concept The x intercept of the load line is the open circuit voltage and the y intercept is the short circuit current. The quiescent point or Q-point is the intersection of diode I-V characteristic with the load line. I-V characteristics of diode must be known. Q point The x intercept of the load line is the open circuit voltage and the y intercept is the short circuit current. The Q-point is dependent on the power supply voltage and the resistance of the rest of the circuit as well as on the diode I-V characteristics. Q point with different R & voltage applied Load Line - Reverse Bias The Q-point is always ID = 0 and VD = the open circuit voltage Summary The load line plots all possible current (ID) conditions for all voltages applied to the diode (VD) in a given circuit. E/R is the maximum ID and E is the maximum VD. Where the load line and the characteristic curve intersect is the Qpoint, which specifies a particular ID and VD for a given circuit. Example 1 For the series diode configuration below, employing the diode characteristics of figure below, determine Q point,(VDQ, IDQ)and VR. Solution1 Step 1: Find the maximum ID. VD = 0V→ ID = IR= E/R Step 2: Find the maximum VD. ID=0A → E = VD + IDR Step 3: Plot the load line Step 4: Find the intersection between the load line and the characteristic curve. This is the Q-point Step 5: Checking !!!! Example 2 Find the Q point for the circuit if the IV characteristic as shown in the graph. Answer Q(0.5V,80mA) Introduction Biasing pn junction Load line concept & graphical analysis Diode Resistance Diode Model Effect of AC voltage on load line As VS varies with time, the load line also changes, which changes the Q-point (VD and ID) of the diode. Effect of AC voltage on load line Diode resistance For a specific applied DC voltage VD, the diode has a specific current ID, and a specific resistance RD Diode resistance In the forward bias region: •The resistance depends on the amount of current (ID) in the diode. •The voltage across the diode is fairly constant (26mV for25°C). •rB ranges from a typical 0.1W for high power devices to 2W for low power, general purpose diodes. In some cases rB can be ignored. In the reverse bias region: The resistance is essentially infinite. The diode acts like an open circuit. Diode resistance AC resistance can be determined by selecting two points on the characteristic curve developed for a particular circuit. Exist due to the semiconductor medium itself. Introduction Biasing pn junction Load line concept & graphical analysis Diode Resistance Diode Model V-I Characteristic curve 1. Ideal diode model The p-n junction only conducts significant current in the forward-bias region. ID is an exponential function in this region. Essentially no current flows in reverse bias. In this characteristic curve we do not consider the voltage drop or the resistive properties. V-I Characteristic curve 2. Practical diode model In most cases we consider only the forward bias voltage drop of a diode. Once this voltage is overcome the current increases proportionally with voltage. This drop is particularly important to consider in low voltage applications. V-I Characteristic curve 3. Complete diode model The voltage drop is not the only loss of a diode. In some cases we must take into account other factors such as the resistive effects as well as reverse breakdown. V-I Characteristic curve ideal & practical for silicon and germanium. ID Ideal - 150V Germanium Silicon - 50V 0.3V VD 0.7V -1uA + Silicon knee voltage = 0.7V, Germanium knee voltage = 0.3V VD ID - Diode Approximation Summary Diodes made of semiconductor material. P and N type materials are joined together to form a PN junction. At the junction a depletion region is formed. This creates barrier that requires approximately .3 V for a Germanium and .7 V for Silicon for conduction to take place.