* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download spring 2016 - Ecs.csus.edu

Direction finding wikipedia , lookup

Tektronix analog oscilloscopes wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Phase-locked loop wikipedia , lookup

Time-to-digital converter wikipedia , lookup

Electronic engineering wikipedia , lookup

Oscilloscope wikipedia , lookup

Radio transmitter design wikipedia , lookup

Regenerative circuit wikipedia , lookup

Broadcast television systems wikipedia , lookup

Battle of the Beams wikipedia , lookup

Oscilloscope types wikipedia , lookup

Valve RF amplifier wikipedia , lookup

Telecommunication wikipedia , lookup

Signal Corps Laboratories wikipedia , lookup

Dynamic range compression wikipedia , lookup

Television standards conversion wikipedia , lookup

Signal Corps (United States Army) wikipedia , lookup

Oscilloscope history wikipedia , lookup

Opto-isolator wikipedia , lookup

Cellular repeater wikipedia , lookup

Analog-to-digital converter wikipedia , lookup

Analog television wikipedia , lookup

Index of electronics articles wikipedia , lookup

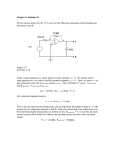

LABORATORY 3: ANALOG TO DIGITAL (A/D) and DIGITAL TO ANALOG (D/A) CONVERSION EEE 182: DIGITAL SIGNAL PROCESSING LABORATORY Department of Electrical & Electronic Engineering College of Engineering & Computer Science California State University, Sacramento SPRING 2016 EEE 182 LABORATORY 3 I. Practical circuit for A/D and D/A conversion using Simulink The schematic of a practical A/D circuit is shown in Figure 1 and the schematic of a practical D/A circuit is shown in Figure 2. The ideal Sample and Hold (S&H) circuit, as shown in Figure 1, is equivalent to impulse train modulation followed by linear filtering with the Zero-Order Hold (ZOH) system. The output of the ZOH system is followed by the uniform quantizer encoder. s(t) 0 T 2T x(t) EE E 181 Digital signal Zero-order hold, h0(t) X x0(t) Quantizer Encoder Digital Signal xs(t) EEE Figure EE 1. Schematic of Analog to Digital Conversion 181 E Quantizer 181 Decoder Zero-order hold h0(t) Reconstruction filter Reconstructed Signal xs(t) x0(t) ASSIG NMENT 3 EEE DSP Figure 2. Schematic of Digital to Analog Conversion Laboratory 3. 181 AS Design of ASSI analog to A In the design of the sample and hold circuit on Simulink, the following three digital SIG conversion GNMSSIGNM system using important blocks will have to be designed accurately: AS NM Simulink ENTENT 3 Definition: A source signalSIG block x(t): Assume a knownDSP input signal from the DSP Blockset sample and hold ENThe 3 (S & H) circuit is the key ASS Laborato library. Since this block design is necessary on this block. NM parameters are fixed, no further Telement DSP required in the IGN ry 3. EN 3 conversion of a LaboDesign of voltage from ME analog T DS to digital NT form. The S & ratoranalog to H circuit The pulse train block s(t): Two important parameters will have to be designed for this block. The first is the pulse amplitude, and the pulse period T sec. You can assume a rectangular pulse with 50 % duty cycle (i.e. half period on, and half period off). Since this pulse train samples the source signal, its frequency should be many times higher than that of the source signal. The zero-order hold block : One important parameter will have to be designed for this block, which is the sampling period of the hold circuit. The sampling period of the circuit should sufficient to hold the sample value over each period of the pulse train. (a) Select an appropriate audio signal from the Simulink DSP blockset library as the test signal in this simulation. Plot the signal on the scope and the FFT scope to obtain the frequency content of the signal. This will provide information on the maximum frequency content of the signal, and the require sampling rate limits. Sample the signal at the Nyquist rate. (b) Design the required parameters of the A/D circuit given in Figure 1, and plot the output of the zero-order hold circuit as seen on the scope block of the Simulink program. (c) Design a uniform quantizer to convert the sampled signal into quantized signal output in numerical or binary form. (d) Design the required parameters of the D/A circuit given in Figure 2 to reconstruct the signal at the receiver. The reconstruction filter is modeled as a low pass filter (analog or digital) with cutoff frequency as the sampling frequency utilized in the A/D process. (e) Plot the reconstructed signal, and compare with transmitted analog signal, and determine the error signal. Also test the audio signal output on a speaker. (f) Repeat the entire simulation for a case of under-sampling: choose a sampling frequency smaller than the Nyquist rate (ex. half the Nyquist rate), and plot the transmitted signal, reconstructed signal and the error signal. (g) Repeat the entire simulation for a case of oversampling: choose a sampling frequency larger than the Nyquist rate (ex. twice the Nyquist rate), and plot the transmitted signal, reconstructed signal and the error signal. II. Simulation of A/D Sample and Hold (S&H) Circuits with non-uniform quantization Repeat Exercise I, however, with the following modifications: In Figure 1, replace the uniform quantizer encoder with a -law quantizer encoder and similarly introduce a -law quantizer decoder in Figure 2. As in Exercise I, repeat steps (d)-(g), and plot the transmitted signal, reconstructed signal and the error signal for the cases of under-sampling, over-sampling and Nyquist sampling. Compare the error in reconstruction, between the cases of uniform quantization, and non-uniform quantization. Compare the audio quality between the case of uniform and non-uniform quantization.