* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download file (2.5 MB, doc)

Schmitt trigger wikipedia , lookup

Crystal radio wikipedia , lookup

Operational amplifier wikipedia , lookup

Wien bridge oscillator wikipedia , lookup

Power electronics wikipedia , lookup

Surge protector wikipedia , lookup

Opto-isolator wikipedia , lookup

Power MOSFET wikipedia , lookup

Current source wikipedia , lookup

Regenerative circuit wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Valve RF amplifier wikipedia , lookup

Index of electronics articles wikipedia , lookup

Electronic engineering wikipedia , lookup

Mathematics of radio engineering wikipedia , lookup

Current mirror wikipedia , lookup

Zobel network wikipedia , lookup

Rectiverter wikipedia , lookup

Two-port network wikipedia , lookup

Topology (electrical circuits) wikipedia , lookup

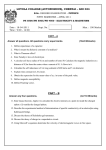

Network Analysis

Net work Topology

eNotes

By

Prof.R.V. Srinivasa Murthy

Assistant Professor, Dept. of E & C

A.P.S. College of Engineering

Bangalore

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

Net work Topology

Definition:

The term circuit topology refers to the science of placement of elements and is a study of the

geometric configurations.

“Circuit topology is the study of geometric properties of a circuit useful for describing the circuit

behavior“

Terms used in Topology:

The following terms are often used in network topology

Graph:

In the given network if all the branches are represented by line segments then the resulting figure

is called the graph of a network (or linear graph). The internal impedance of an ideal voltage

source is zero and hence it is replaced by a short circuit and that of an ideal current source is

infinity and hence it is represented by an open circuit in the graph.

Example: Network

Graph

Node

It is a point in the network at which two or more circuit elements are joined. In the graph shown 1,

2, 3 and 4 are nodes.

Branch (or Twig):

It is a path directly joining two nodes. There may be several parallel paths between two nodes.

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

Oriented Graph

If directions of currents are marked in all the branches

of a graph then it is called an oriented (or directed) graph .

Connected graph

A network graph is connected if there is a path between any two nodes .In our further

discussion,let us assume that the graph is connected. Since, if it is not connected each disjoint part

may be analysed separately as a connected graph.

1

2

4

3

Unconnected graph

If there is no path between any two nodes,then the graph is called an unconnected graph.

1

2

4

1

2

4

3

3

5

3

5

5

Planar graph

A planar graph is a graph drawn on a two dimensional plane so that no two branches intersect at

a point which is not a node.

B

A

C

A

B

E

D

D

E

E

C

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

Non – planar graph

A graph on a two – dimensional plane such that two or more

branches intersect at a point other than node on a graph.

Tree of a graph

Tree is a set of branches with all nodes not forming any loop or closed path.

(*) Contains all the nodes of the given network or all the nodes of the graph

(*) No closed path

(*) Number of branches in a tree = n-1 , where n=number of nodes

A

2

B

C

A

B

2

5

6

D

C

4

5

D

Two possible trees

Graph

Co- tree

A Co- tree is a set of branches which are removed so as to form a tree or in other words, a co- tree

is a set of branches which when added to the tree gives the complete graph. Each branch so

removed is called a link.

Number of links = l = b – (n-1) where b = Total number of branches

n = Number of nodes

Incidence Matrix

Incidence matrix is a matrix representation to show which branches are connected to which nodes

and what is their orientation in a given graph

(*) The rows of the matrix represent the nodes and the columns represents the branches of the

graph.

(*) The elements of the incidence matrix will be +1, -1 or zero

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

(*) If a branch is connected to a node and its orientation is away from the node the corresponding

element is marked +1

(*) If a branch is connected to a node and its orientation is towards the node then the corresponding

element is marked – 1

(*) If a branch is not connected to a given node then the corresponding element is marked zero.

Incidence Matrix

Complete Incidence matrix

Reduced incidence matrix

( i )Complete incidence matrix:

An incidence matrix in which the summation of elements in any column in zero is called

a complete incidence matrix.

( ii )Reduced incidence matrix:

The reduced incidence matrix is obtained from a complete incidence matrix by eliminating a

row. Hence the summation of elements in any column is not zero.

Example 1: Consider the following network and the oriented graph as shown

Network

Oriented graph

(*) There are four nodes A, B, C and D and six branches 1, 2, 3, 4, 5 and 6. Directions of

currents are arbitrarily chosen.

(*) The incidence matrix is formed by taking nodes as rows and branches as columns

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

Nodes

Branches

1

2

3

4

5

6

A

-1

+1

+1

0

0

0

B

0

-1

0

-1

+1

0

C

0

0

-1

+1

0

+1

D

+1

0

0

0

-1

-1

P =

-1 1 1

0

0

0

0 -1 0 -1

1

0

0

0

1

0 -1 1

1 0 0 0

-1 -1

In the above example the fourth row is negative of sum of the first three rows. Hence the fourth

can be eliminated as we know that it can be obtained by negative sum of first three rows. As a

result of this we get the reduced incidence matrix.

PR =

-1 1 1

0

0 0

0 -1 0 -1 1 0

0

0 -1 1

0 1

Properties of a complete incidence matrix

(*) Sum of the entries of each column is zero

(*) Rank of the matrix is (n-1), where n is the no of nodes

(*) Determinant of a loop of complete incidence matrix is always zero

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

Example 2 : The incidence matrix of a graph is as shown. Draw the corresponding graph.

Solution :

1

0

0

0

1

-1

-1

1

1

0

0

0

given matrix is zero. Hence it

0 -1 0

-1

0

1

is a compete incidence matrix.

0

-1 1 -1

0

The sum of each column of the

0

Number of nodes = n = 4 ( say A. B. C and D)

Number of branches = b = 6 ( say 1, 2, 3, 4, 5 and 6)

Prepare a tabular column as shown.

Nodes

Branches

1

2

3

4

5

6

A

1

0

0

0

1

-1

B

-1

1

1

0

0

0

C

0

-1

0

-1

0

1

D

0

0

-1

1

-1

0

From the tabular column, the entries have to be interpreted as follows:

From the first column the entries for A and B are one’s . Hence branch 1 is connected between

nodes A and B . Since for node A entry is +1 and for node B it is -1, the current leaves node

A and enters node B and so on.

From these interpretations the required graph is drawn as shown.

6

A

B

1

C

2

5

3

4

D

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

Example 3: The incidence matrix of a graph is as shown. Obtain the corresponding graph

1 1 0 0 0

0 0

0 -1 1 1

0

0

0

0 0 0 -1 1 1 0

0 0 0 0 0 -1 1

Solution:- Given incidence matrix is a reduced incidence matrix as the sum of each column is not

zero. Hence it is first converted in to a complete incidence matrix by adding the deleted row. The

elements of each column of the new row is filled using the fact that sum of each column of a

complete incidence matrix is zero.

In the given matrix in first, third, fifth and the seventh column the sum is made zero by adding –1

in the new row and the corresponding node is E. The complete incidence matrix so obtained and

also the graph for the matrix are as shown.

Nodes

Branches

1

2

3

4

5 6

7

A

1

1

0

0

0

0

0

B

0

-1

1

1

0

0

0

C

0

0

0

-1

1

1

0

D

0

0

0

0

0

-1

1

E

-1

0

-1

0

-1

0

-1

Graph:

6

7

E

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

Net work Topology

SESSION :2

Tie – set Analysis:

In order to form a tree from a network several branches need to be removed so that the

closed loops open up. All such removed branches are called links and they form a Cotree. Alternatively when a link is replaced in a tree, it forms a closed loop along with

few of the tree branches. A current can flow around this closed loop. The direction of

the loop current is assumed to be the same as that of the current in the link. The tree –

branches and the link that form a loop is said to constitute a tie – set.

Definition

A tie – set is a set of branches contained in a loop such that the loop has at least one link

and the remainder are twigs (tree branches)

6

6

4

B

4

5

A

C

C

x

1

1

3

5

A

2

Graph

z

B

y

2

3

D

tree (In thick lines) Co-tree (In dotted lines)

D

We see that by replacing the links 1, 4 and 5 three loops are formed and hence three loop

currents x, y and z flow as shown. The relationships obtained between loop currents, tree

branches and links can be scheduled as follows

Tie – set schedule

Tie – set

1

2

3

Tree – branches

2, 3

1, 4

4, 5

Link

5

2

6

Loop current

x

y

z

Tie – set matrix (Bf)

The Tie – set schedule shown above can be arranged in the form of a matrix where in the

loop currents constitute the rows and branches of the network constitute the columns

Entries inside the matrix are filled by the following procedure :

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

Let an element of the tie – set matrix be denoted by mik

Then

mik

=

1 Branch K is in loop i and their current directions are same

-1 If branch K is in loop i and their current directions are opposite.

0 If the branch K is not in loop i

By following this procedure we get the Tie – set matrix which is shown below:

Loop

Branches

currentss1

2

3

4

5

6

x

0

+1

+1

0

+1

0

y

+1

+1

0

+1

0

0

z

0

0

0

+1

-1

-1

Or

0 1 1 0 1 0

Bf =

1 1 0 1 0 0

0 0 0 1 -1 -1

Analysis of the net work based on Tie – set schedule

From the tie –set schedule we make the following observations.

(i) Column wise addition for each column gives the relation between branch and loop

currents

That is

i1

i2

i3

i4

i5

i6

=

=

=

=

=

=

y

x+y

x

y+ z

x-z

-z

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

Putting the above equations in matrix form, we get

i1

i2

i3

i4

i5

i6

=

0

1

1

0

1

0

1

1

0

1

0

0

0

0

0

1

-1

-1

x

y

z

In compact form IB = B fT IL

Where

IB = Branch current matrix

B fT = Transpose of the tie- set matrix

IL = Loop current column matrix

(ii)Row wise addition for each row gives the KVL equations for each fundamental

loop

Row - 1

Row - 2

Row - 3

:

:

:

0 1 1 0 1 0

1 1 0 1 0 0

0 0 0 1 -1 -1

In compact form

V1 + V2 + V3 = 0

V1 + V2 + V4 = 0

V4 - V5 - V6 = 0

V1

V2

V3

V4

V5

V6

= 0

B f VB = 0

- - - (1)

Where VB = Branch voltage column matrix and

B f = Tie - set matrix

Equilibrium equations

Let us consider a network

having b- branches. Each branch

of the network has a representation

as shown in figure

Vk = Ik Zk

+

Ik

Zk

Vk +

Vsk

±

-

VSK- - - (2)

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

Since the network has b branches one such equation could be written for every branch of

the network. That is

V1 = Z1 I1 + Vs1

V2 = Z2 I2 + Vs2

‘

,

‘

,

‘

,

,

,

,

, ,

,

Vb = Zb Ib + Vsb

Putting the above set of equations in a matrix form we get

VB = ZB IB+ VS

- - - (3)

Where VB = Branch – Voltage column matrix of order b x 1

Z1 0

0 Z2

0

0

ZB =

0

-

0

-

-

0

0 = Branch Impedance matrix (bX b)

ZB

IB = Branch current matrix of order b x 1

and Vs

=

Vs 1

Vs 2

Vs3

‘

‘

‘

=

Voltage source column matrix of order bx1

Vs b

The elements in the voltage source matrix are positive if the branch currents enter the

positive terminal of the source otherwise negative

From equation (1) BfVB =0

Substituting equation (3) we get, Bf ZB IB + Vs = 0

………(4)

Also the relation between branch and loop currents is given by IB = B fT IL

Substituting for IB in equation (4)

Bf [ ZB B fT IL + Vs ] = 0

Bf ZB B fT IL+ Bf Vs = 0

ZL IL + Bf Vs = 0 …………….(5)

impedance matrix

Where ZL = Bf ZB B

f

T

is defined as Loop

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

Action Plan for tie –set analysis

(*) Form the Tie-set Matrix (Bf )

(*) Construct the branch impedance matrix (ZB)

(*) Loop impedance matrix is formed by using the relation ZL = Bf ZB B fT

(*) Form the KVL or Equilibrium equations using the relation ZL IL + Bf Vs = 0

(*) The branch currents are then found using the matrix equation IB = B fT IL

(*) Finally the branch voltages are found using the matrix equation

VB = ZB IB+ VS

A

5

Example: For the network shown in figure, write a

Tie-set schedule and then find all the branch 50 ±

Currents and voltages

V

5

10

B

10

Solution: The graph and one possible tree is shown:

C

5

5

D

A

1

2

1

5

B

4 6

C

5

x

y

6

4

z

D

3

2

3

Loop

current

x

y

z

1

1

0

0

Tie set Matrix:

2

0

1

0

Branch Numbers

3

4

0

1

0

0

1

-1

5

-1

1

0

6

0

-1

1

Bf = 1 0 0 1 -1 0

0 1 0 0 1 -1

0 0 1 -1 0 1

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

Branch Impedence matrix

ZL =

ZB =

1 0 0 1 -1 0

0 1 0 0 1 -1

0 0 1 -1 0 1

5

0

0

0

0

0

0 0 0 0

10 0 0 0

0 5 0 0

0 0 10 0

0 0 0 5

0 0 0 0

0

0

0

0

0

5

5 0 0 0 0 0

0 10 0 0 0 0

0 0 5 0 0 0

0 0 0 10 0 0

0 0 0 0 5 0

0 0 0 0 0 5

1 0 0

0 1 0

0 0 1

1 0 -1

-1 1 0

0 -1 1

20 -5 -10

-5 20 -5

-10 -5 20

Loop Equations :

ZL IL = - Bf Vs

ZL

=

20 -5 -10

-5 20 -5

-10 -5 20

x

y

z

=-

1 0 0 1 -1 0

0 1 0 0 1 -1

0 0 1 -1 0 1

-50

0

0

0

0

0

20x-5y-10z =50

-5x+20y-5z = 0

-10x-5y+20z =0

Solving the equations, we get x = 4.17 Amps

y = 1.17 Amps

And z = 2.5 Amps

Branch Currents :

I1

I2

I3

I4

I5

I6

=

IB = B fT IL

1 0 0

0 1 0

0 0 1

1 0 -1

-1 1 0

0 -1 1

x

y

z

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

Which gives

I1 = 4.17 A

I2 = 1.17 A

I3 = 2.5 A

Branch Voltages:

V1

V2

V3

V4

V5

V6

=

I4 = 1.67 A

I5 = -2.5A

I6 = 0.833A

VB = ZB IB+ VS

5 0 0 0 0 0

0 10 0 0 0 0

0 0 5 0 0 0

0 0 0 10 0 0

0 0 0 0 5 0

0 0 0 0 0 5

I1

I2

I3

I4

I5

I6

+

-50

0

0

0

0

0

V1 = 29.17 volts

V2 = 16.67 volts

V3 = 12.5 volts

V4 = 16.67 volts

V5 = - 12.5 volts

V6 = 4.17 volts

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

Net work Topology

SESSION :3

Cut – set Analysis

A cut – set of a graph is a set of branches whose removal , cuts the connected graph in to two

parts such that the replacement of any one branch of the cut set renders the two parts

connected.

A

A

1

5

Example

4

B

3

D

4

B

D

2

6

3

C

C

Directed graph

Two separate graphs created by the cut set (1, 2, 5, 6)

Fundamental cut – set is a cut – set that contains only one tree branch and the others are

links

Formation of Fundamental cut – set

(*) Select a tree

(*) Select a tree branch

(*) Divide the graph in to two sets of nodes by drawing a dotted line through the selected

tree branch and appropriate links while avoiding interruption with any other tree – branches.

Example 1 : For the given graph write the cut set schedule

A

4

1

B

5

3

A

D

2

1

4

6

C

The fundamental cut –set of the

Selected tree is shown in figure

5

B

2

3

D

6

C

Note that FCS - 1 yields node A and the set of nodes ( B, C, D)

The Orientation of the fundamental cut – set is usually assumed to be the same as the

orientation of the tree branch in it, Which is shown by an arrow. By following the same

procedure the FCS- 2 and FCS -3 are formed as shown below:

A

A

1

5

1

5

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

4

B

3

D

B

3

2

2

4

D

6

6

C

C

FCS -2

FCS -3

It should be noted that for each tree branch there will be a fundamental cut – set. For a graph

having ‘n’ number of nodes the number of twigs is (n-1).Therefore there will be (n-1)

(n-1) fundamental cut-sets.

Once the fundamental cut sets are identified and their orientations are fixed, it is

possible to write a schedule, known as cut – set schedule which gives the relation between

tree – branch voltages and all other branch voltages of the graph.

Let the element of a cut – set schedule be denoted by Qik then,

Qik = 1

If branch K is in cut – set I and the direction

of the current in the branch K is same as cut – set direction .

-1 If branch k is in cut – set I and the direction of the current in

k is opposite to the cut – set direction.

O If branch is k is not in cut – set i

Cut set Schedule

Tree

Branch Voltages

branch 1

2

3

4

5

6

voltage

e1

1

0

0

-1

-1

0

e2

0

1

0

1

0

1

e3

0

0

1

0

1

-1

The elements of the cut set schedule may be written in the form of a matrix known as the cut

set matrix.

Qf =

1 0

0

-1

-1 0

0 1

0

1

0 1

0 0

1

0

1 -1

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

Analysis of a network using cut set schedule

(*) Column wise addition of the cut set schedule gives the relation between tree branch

voltage and the branch voltages for the above cut the schedule

V1 = e1

V2 = e2

V3 = e3

V4 = - e1 + e2

V5 = - e1+ e3

V6 = e2 - e3

In matrix form

V1

V2

V3

V4

V5

V6

1

0

0

= -1

-1

0

0

1

0

1

0

1

0

0

1

0

1

-1

e1

e2

e3

In compact form

VB = QTf VT

………. (1)

Where VB =Branch voltage Matrix

QTf = Transpose of cut set matrix

and VT = Tree branch voltage matrix.

(*) Row wise addition given KCL at each node

I1 - I4 - I5 =

0

I2 + I4 + I6 =

0

I3 + I5 + I6 =

0

In matrix form

1 0

0

-1

-1 0

I1

0 1

0

1

0 1

I2

0 0

1

0

1 -1

I3

=

0

I4

I5

I6

In compact form Qf IB = 0 …………………(2) Where Qf = cut set matrix

IB = Branch current matrix

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

IK

VK

(*) Let us consider a network having ‘b’ branches.

Each of the branches has a representation as shown in figure

YK

ISK

Referring to the figure Ik = Yk Vk + Isk

Since the network has b branches, one such equation could be written for every branch

of the network ie

I1 = Y1 V1 + Is1

I2 = Y2 V2 + Is2

-----------------------------…………………………

Ib = Yb Vb + Isb

Putting the above set of equations in a matrix form we get

………………………

IB = YB VB + Is

(3)

IB = Branch current matrix of order bx1

YB =

Y1

0

0

0 0 - - 0

Y2 0 - - 0 =

- - - - 0 - - - Yb

Branch admittance

matrix of order bx b

VB = Branch Voltage column matrix of order bx1 and

IB = Source current matrix of order bx1.

Substituting (3) in (2) we get

Qf

YB VB + IS =

0

Qf YB VB + Qf IS =

0

But from (1) we have VB = Qf T VT

Hence equation (4) becomes

Qf YB QTf VT + Qf IS

YC VT + QfIS

=

=

or

…………………….

YC VT = - Qf IS

0

0

(5)

Where YC = Qf YB Qf T is called cut - set admittance matrix

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

Action Plan for cut – set analysis.

(*) Form the cut- set matrix Qf

(*) Construct the branch admittance matrix YB

(*) Obtain the cut – set admittance matrix using the equation YC = Qf YB Qf T

(*) Form the KCL or equilibrium equations using the relation YC VT = - Qf IS

The elements of the source current matrix are positive if the directions of the branch

current and the source connect attached to that branch are same otherwise negative.

(*) The branch voltages are found using the matrix equation VB = Qf T VT

(*) Finally the branch currents are found using the matrix equation IB = YB VB + IS

Example 2 : For the directed graph obtain the cut set matrix

A

5

6

1

D

E

B

4

2

8

3 7

C

Solution : The tree (marked by thick lines)and the link (marked by doffed lines)are as

shown. The fundamental cut sets are formed at nodes A B C and D keeping ‘E’ as

reference node

Fcs - 1 --

( 1, 5, 6)

Fcs - 2 --

(2, 6,

7)

Fcs - 3 -- ( 3, 7,

8)

Fcs - 4 -- (4,

8)

5,

A

FCS-1

1

D

FCS4

4 E 2

B FCS2

FCS3 C

Hence the cut – set schedule is as follows:

Tree

Branch

branch 1

2

3

4

5

6

7

8

0

0

0

-1

1

0

0

voltage

e1

1

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

e2

0

1

0

0

0

-1

1

0

e3

0

0

1

0

0

0

-1

1

e4

0

0

0

1

1

0

0

-1

Hence the required cut –set matrix

Qf = 1

0

0

0

0

1

0

0

0 0 -1 1 0 0

0 0 0 -1 1 0

1 0 0 0 -1 1

0 1 1 0 0 -1

Example 3: Find the branch voltages using the concept of cut-sets

1

1

1

1

1

1V ±

1

Solution : The voltage source is Transformed in to an equivalent current source. It should be

noted that all the circuit Passive elements must be admittances and the net work should

contain only current sources.

The graph for the network is shown. A possible tree (shown with thick lines) and co tree

(shown by dotted lines) are shown

1mho

FCS 1 = 3, 1, 5

1mho

FCS 2 = 4, 2, 5

1mho

1mho

FCS 3 =

1 mho

1mho

6, 1, 2

1A

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

Cut set schedule

Tree

Branches

branch 1

2

3

4

FCS2

5

5

6

voltage

e3

-1

0

1

0

-1

0

e4

0

1

0

1

1

0

e6

1

-1

0

0

0

1

3

A

FCS1

4

8

6

1

2

FCS3

-1 0 1 0 -1 0

0 10 1 1 0

1 -1 0 0 0 1

Qf =

1 0

0 1

0 0

0 0

0 0

0 0

YB =

0

0

1

0

0

0

0 0

0 0

0 0

1 0

0 1

0 0

0

0

0

0

0

1

-1 0 1

-1 0 1 0 -1 0

YC=

=

0 1 0 1 1 0

1 -1 0 0 0 1

3

-1

-1

-1

3

-1

-1

-1

3

Equilibrium Equations

1 0 0 0 0 0

0 1 0 0 0 0

0 0 10 0 0

0 0 0 1 0 0

0 0 0 0 1 0

0 0 0 0 0 1

0

1

0

-1

0

1

0

1

1

0

-1

0

0

0

1

; YC VT = - Qf IS

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

3 -1 -1

-1 3 -1

-1 -1 3

e3

e4

e6

=

-1 0 1 0 -1 0

0 1 0 1 1 0

1 -1 0 0 0 1

-

-1

0

0

0

0

0

3 e3 – e4 – e6 = - 1

-e3 + 3 e4 – e6 = 0

- e3 – e4 + 3e6 = 1

Solving we get e3=-0.25 volt

e4=0

e6=0.25 volt

Branch voltages

VB = Qf T VT

V1

-1 0

V2

1

0

1 -1

V3

1

0

0

V4

0

1

0

V5

-1

1

0

V6

0

=

0

-0.25

0

0.25

1

0.5

-0.25

= -0.25

0.0

0.25

0.25

V1 = 0.5 Volts

V2 = -0.25 Volts

V3 = -0.25 Volts

V4 = 0 Volts

V5 = 0.25 Volts

V6 =0.25 Volts

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

SESSION- 4

DUALITY CONCEPT

Two electrical networks are duals if the mesh equations that characterize one have the same

mathematical form as the nodal equations of the other.

Example 1

Consider an R-L-C series network excited by a voltage

so source V as shown in the figure. The equation generating

the circuit behavior is Ri+Ldi +1 ∫idt =V ……..(1)

dt C

Figure 1

Now consider the parallel G-C-L network

fed by a

Current Source i is shown in the figure. The

equation generating the

Circuit behavior is GV+ CdV +1 ∫vdt = i

……..(2)

dt L

Figure 2

Comparing the equations (1) and (2),we get the similarity between the networks of fig(1) and

fig(2).The solution of equation (1) will be identical to the solution of equation (2) when the

following exchanges are made

R → G, L→ C, C→L and V →i

Hence networks of figure (1) and (2) are dual to each other.

Table of dual Quantities

1.Voltage Source

2.Loop currents

3.Iductances

4.Resistances

5.Capacitances

6. On KVL basis

7.Close of switch

Current source

Node voltages

Capacitances

Conductances

Inductances

On KCL basis

Opening of switch

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

Note:Only planar networks have duals.

Procedure for drawing dual network

The duals of planar networks could be obtained by a graphical technique known as the dot

method. The dot method has the following procedure.

Put a dot in each independent loop of the network. These dots correspond to

independent nodes in the dual network.

Put a dot outside the network. This dot corresponds to the reference node in the dual

network.

Connect all internal dots in the neighboring loops by dotted lines cutting the common

branches.

These branches that are cut by dashed lines will form the branches connecting the

corresponding independent nodes in the dual network.

Join all internal dots to the external dot by dashed lines cutting all external branches.

Duals of these branches will form the branches connecting the independent nodes and

the reference node.

Example 1:

Draw the exact dual of the electrical

circuit shown in the figure.

3ohm

2sin6t

4F

4ohm

±

1

6H

O

2

Solution: Mark two independent nodes 1 and

2 and a reference node 0as shown in the

figure.

Join node 1 and 2 by a dotted line

passing through the inductance of

6H.this element will appear as

capacitor of 6 F between node 1 and 2

in the dual.

Join node 1 and reference node

through a dotted line passing the

voltage source of 2sin6t volts. This

will appear as a current source of

2sin6t amperes between node1 and

reference node.

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

Join node 1 and reference node through a dotted line passing through 3 ohms resistor.

This element appears as 3mho conductance between node1 and reference node in the

dual.

Join node 2 and reference node through a dotted line passing through the capacitor of

4 Farads. This element will appear as 4 Henry inductor between node 2 and

reference node in the dual

Join node 2 and reference node through a dotted line passing through the resistor of 4

ohms. This element will appear as 4 mho conductance between node 2 and reference

node.

The Dual network drawn using these procedural steps is shown.

Loop equations for the original network

Applying Kirchoff’s Voltage Law to the two loops we get 3i1 + 6 di1 -6di2 =2 Sin6t

dt

dt

and -6 di1 + 6 di2 + 1 ∫ i 2 dt =0

dt

dt 4

N0DE EQUATIONS

Applying Kirchoff’s Current Law at nodes 1 and 2 ,we get, 3V1 + 6 dV1 -6dV2 =2 Sin6t

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

dt

dt

-6 dV1 +6dV2 + 1 ∫V2 dt + 4V2 =0

dt

dt

4

By looking at these equations it can be further understood that dual network drawn is the

correct one.

Example 2: Construct the dual electrical network for the network shown

K

L1

i1

i2

C1

vs

R1

±

R3

L2

R2 R2

i3

iS

Solution: Mark three independent nodes 1,2and 3 and a reference node 0 as shown in figure.

The dual of the network is then drawn using the dot-method.

L1

1

VS ±

C1

L2

2

R2

R3

R

R3

3

iS

0

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

Finally the dual circuit is redrawn in a more standard form as shown.

C1

L2

L1

1

iS

2

G1

3

C1

G3

±± VS

DUAL GRAPHS

For a given graph a dual graph can be constructed by converting each tie-set of the given

graph as

Cut-set in the dual graph. Two network graphs are said to be dual to each other when the

eqations

Written for one on loop current basis and the other on node-pair voltage basis are identical.

# ) Total number of branches in the graph is equal to the number of branches in the dual

graph

# ) The number of independent loops in the graph is equal to the number of node pairs in the

dual graph.

Procedure for constructing dual graphs

1.

2.

3.

4.

5.

Mark node-pairs equal to number of loops

Mark one reference node

Assign each of the nodes to each of the meshes in the graph

For each mesh note the tie-set and the corresponding cut-set in the dual graph

Common branch between loops appears as a branch between

corresponding nodes

6. Peripheral branch confined to a loop appears as a branch

between that node and the reference node.

7. Directions of branches in the dual are marked as follows:

4

i)

If the loop current and branch current directions

8

are same orientation is away from that node

ii)

On the other hand if they are opposite then the

orientation is into the node

7

Example1: Draw the oriented dual graph of the graph

Q

In figure

1

Solution:

In the given graph

n=4(P,Q,R and

b=8(

3

2

5

R

6

shown

S)

1,2,3,4,5,6,7and8)

d

a

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

b

e

c

c

l=b-(n-1)

=8-(4-1)=5

(*) Hence there are five tie-sets in the given graph. Correspondingly

there will be five node-pair voltages in its dual graph with one ref

node.

(*) Let the loop currents be a,b,c,d and e as shown.

(*) Mark nodes a,b,c,d and e as shown in figure

(*) Mark ‘f ‘ as the reference node

(*) For loop ‘ a ‘ branch 1 is peripheral and 4 is common

to a and b.Hence branch 1 is connected

between nodes a and f . Branch 4 is connected between

a and b.

P

S

(*) Loop current ‘a ‘ and branch 1 current are in same direction.Hence

the orientation of the branch 1 is away from node a,where as for branch 4

the directions are opposite.Hence the orientation of branch 4 is towards

node ‘a ‘(*) Following the same procedure other branches are drawn and their orientation

is marked

to get the required graph as shown.

8

b

4

a

c

5

7

6

d

e

1

2

3

f

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

Example 2 :

Determine the dual graph for the graph shown in figure

a

Solution: For the given graph b= 7

n =4

2

l

1

= 7-(4-1) = 4

b

(*) Hence there are 4 tie-set schedules and hence four loop currents

l= b-(n-1)

( i, j , k, l ) as shown

e

k

c

d

j

i

f

4

3

g

(*) Mark four nodes i , j , k and l on the sheet and also the reference

node o as shown in figure

(*) By following the same procedure as explained in the previous

example the dual oriented graph is drawn as shown in figure.

i

j

k

l

d

e

b

c

g

f

a

o

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

Resonant Circuits

Resonance is an important phenomenon which may occur in circuits containing both

inductors and capacitors.

In a two terminal electrical network containing at least one inductor and one capacitor, we define resonance as the condition,

which exists when the input impedance of the network is purely resistive. In other words a network is in resonance when the voltage and

current at the network in put terminals are in phase.

Resonance condition is achieved either by keeping inductor and capacitor same and

varying frequency or by keeping the frequency same and varying inductor and capacitor.

Study of resonance is very useful in the area of communication. The ability of a radio

receiver to select the correct frequency transmitted by a broad casting station and to

eliminate frequencies from other stations is based on the principle of resonance.

The resonance circuits can be classified in to two categories

1. Series – Resonance Circuits.

2. Parallel – Resonance Circuits.

R

L

C

1.Series Resonance Circuit

A series resonance circuit is one in which a coil and

a capacitance are connected in series across an alternating

I

voltage of varying frequency as shown in figure.

The response ‘I’ of the circuit is dependent on the impedance of the circuit,

V

Where Z= R +jXL - jXC

and I= V

at any value of frequency

Z

We have XL =2πfL

XL varies as f

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

and

XC

= 1

XC varies inversely as f

2πfC

In other words, by varying the frequency it is possible to reach a point where X L = XC

In that case Z = R

.

and hence circuit will be under resonance. Hence the series A.C.

circuit is to be under resonance, when inductive reactance of the circuit is equal to the

capacitive reactance. The frequency at which the resonance occurs is called as resonant

frequency ( fr)

Expression for Resonant Frequency ( fr )

At resonance XL = XC

i.e. ω r L = 1

ω rC

ω2 r L C = 1

ω2 r =

1

L C

f2r =

1

4π 2LC

fr =

1

2π √LC

Salient Features of Resonant circuit

(*) At resonance XL = XC

(*) At resonance Z = R i.e. impedance is minimum and hence I = V

is maximum

Z

(*) The current at resonance (Ir) is in phase with the voltage

(*) The circuit power factor is unity

(*) Voltage across the capacitor is equal and opposite to the voltage across the

inductor.

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

Frequency response of a series resonance circuit

For a R-L-C series circuit the current ‘I’ is given by

V

I=

____________

R + j ( XL- XC )

At resonance XL = XC and hence the current at resonance (Ir) is given by Ir = V/R

At off resonance frequencies since the impedance of the circuit increases the current

in the circuit will reduce. At frequencies f Where f> fr , the impedance is going to be more

inductive. Similarly at frequencies f < fr the circuit impedance is going to be more

capacitive. Thus the resonance curve will be as shown in figure.

I

Ir

Xc > Xl

Xl > Xc

f

fr

Qualify – factor (or Q – factor)

Another feature of a resonant circuit is the Q – rise of voltage across the resonating

elements.

If V is the applied voltage across a series resonance circuit at resonance, I r = V

R

The voltage across the inductance ‘L’, =V L = I r XL = V ω r L

R

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

ω rL

VL = V

R

V L = QV where Q = ω r L is the Q factor

R

From the above equation it is seen that the voltage across the inductive coil is Q times the applied voltage (V) The response of the series

resonant circuit is largely dependent on Q of the coil.

Band – width concept

Any circuit response, which is frequency dependent, has certain limitations. The output

response during limited band of frequencies only will be in the useful range. If the out put

power is equal to or more than half of the maximum powerout put that band of frequencies

is considered to be the useful band. If I r is the maximum current at resonance then

Power at resonance = Pmax = I2 r R

But If I= I r Then corresponding power is given by I2 R = Ir

√2

I2 R = 1

2

R

√2

I2 r R = 1 ( Max Power)

2

2

Hence the useful range of frequencies will be frequencies where current will be equal to or

more than Ir

= 0.707 Ir

√2

Consider the frequency response characterstic of a series resonant circuit as shown in figure

Ir

0.707 Ir

freq

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

F1

F2

Fr

In the figure it is seen that there are two frequencies where the out put power is half of the

maximum power. These frequencies are called as half power points f1 and f2

A frequency f1 which is below fr where power is half of maximum power is called

as lower half power frequency (or lower cut – off frequency). Similarly frequency f2

which is above fr is called upper half power frequency (or upper cut-off frequency)

The band of frequencies between f2 and f1 are said to be useful band of frequencies since during these frequencies of operation

the out put power in the circuit is more than half of the maximum power. Thus their band of frequencies is called as Bandwidth.

i.e Band width =B.W = f2 - f1

Selectivity : Selectivity is a useful characteristic of the resonant circuit. Selectivity is

defined as the ratio of band width to resonant frequency

Selectivity

= f 2- f 1

fr

It can be seen that selectivity is the reciprocal of Quality factor. Hence larger the value of Q

Smaller will be the selectivity.

The Selectivity of a resonant circuit depends on how sharp the out put is contained

with in limited band of frequencies. The circuit is said to be highly selective if the

resonance curve falls very sharply at off resonant frequencies.

Relation between Resonant frequency and cut-off frequencies

Let fr be the resonant frequency of a series

Ir

resonant circuit consisting of R,L and C

elements .From the Characteristic it is

0.707Ir

seen that at both half frequencies

f2 and f1 the out put current is 0.707 Io

which means that the magnitude of the

impedance is same at these points.

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

At lower cut-off frequency f1

———————

Impedance is given by √ R2 +

XC1 – XL1

f1

fr

f2

2

At upper cut-off frequency f2

___________________

Impedance is given by √R2 + ( XL2 – XC2 ) 2

But these impedances are equal

——————————

Hence

√ R2 + ( XC1 – XL1)

2

—————————

√ R2 + ( XL2 – XC2 )

=

2

XC1 – XL1 = XL2 – XC2

XC1 + XC2

1

1

C

= XL1 + XL2

=

+1

ω1

ω1 ω2

L

ω1 + ω2

ω2

= 1

LC

ωr

We have fr = 1

=

2π √LC

Hence ω r

√LC

= _1__

2

1

ωr

2

= ω1 ω2

or f 2r = f 1 f 2

LC

fr = √ f1 f2

i.e. Resonant frequency is the geometrical mean of half power frequencies.

Relation between resonant frequency (f r) Band width and quality factor (Q)

Let f 1and f 2 be the lower and upper

Ir

half power frequencies and f r the

resonant frequency .At both half

0.707Ir

power frequencies the magnitude

of impedance can be calculated as follows.

At lower cut- off frequency (f 1)

V

I=

——————————

√ R2 +

Xc1 – XL1

2

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

f1

But I1 = Ir / √ 2

Hence V

=

fr

f2

V/ √ 2 R

=

V

√ 2 R

——————————

√ R2 +

√ R2 + Xc1 – XL1

2

Xc1 – XL1

2

√ 2 R

=

i.e. Xc1 – XL1 = R ………(1)

Similarly at upper cut-off frequency,

I2 =

V

——————————

√ R2 +

XL2 – XC2

V

= V/ √ 2 R

2

=

√ 2 R

But I2 = Ir / √ 2

V

——————————

√ R2 + XL2 – XC2

2

——————————

√ R2 + XL2 – XC2

XL2 – XC2

=

2

= √ 2 R

R………(2)

Adding equations (1) and (2),we get Xc1 – XL1 + Xc2 – XL2

1/ω 1 C - 1/ω 2C + ω 2L - ω 1L

=2R

1/C 1/ω 1 - 1/ω 2 + L ω 2 - ω 1

1/C ω 2 - ω 1

+ Lω2-ω1

= 2R

=2R

= 2R

ω2ω1

ω 2 - ω 1 = 2R

1/ ω 2 ω 1C +L

=

2R/L

=

R/L

1/ ω 2 ω 1LC + 1

ω2-ω1 = R

ωr

ωr L

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

ω2-ω1 = ωr

ω r L/R

f2 – f1 = fr / Q

Band width = f r / Q

Resonance by varying Inductance

Resonance in RLC series circuit can also be obtained by varying resonating circuit

elements . Let us consider a circuit where in inductance is varied as shown in figure.

R

L

C

Ir

V, f Hz

0.707Ir

At resonance XL =Xc , ω L r = 1/ ωC

L r = 1/ ω2C,where L r = value of inductance at resonance.

L1

Lr

L2

At lower – half point

Let L1 be the value of inductance.

I= I0/ √ 2 and I0 = V/R

V

√R2 +

1

=

Xc1 – XL1

-ωL1 = R

ωC

2

V/

√2 R

L1 = 1

-R

ω 2C ω

At upper – half point

Let L 2 be the value of inductance. Then ω L 2 - 1 = R

ωC

L2 = 1

+ R

ω 2C

ω

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

Resonance by varying capacitance

R

L

V, f Hz

C

C1

Cr

C2

C

Consider an RLC series circuit in which

capacitance ‘C’ is varied.

At resonance Xc = XL

1

= ωL

ω Cr

Cr = 1

Cr =

Capacitance value at resonance.

ω2L

1

At lower – half point

1

= R+ωL .

-ωL = R

ω C1

ω C1

C1 =

1

Farad

ω 2L + ωR

At upper – half point

ωL- 1

-= R

1

= ω L- R.

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

ω C2

C2 =

ω C2

1

Farad

ω 2L - ωR

Expressions for maximum capacitor voltage and maximum inductor voltage

From the figure it is clear that voltage across L and voltage

across C are not maximum at resonant frequency (fr).

Rather voltages VL and VC are equal in magnitude and

opposite in phase at fr. The voltage Vc is maximum at

a frequency fc max which is less than fr and the voltage

VL is maximum at a frequency fL max which is greater than fr

Ir

VC

VL

fc

fr

max

f

l

max

Freq

Expression for fcmax

Voltage across capacitor Vc is given by Vc = I Xc = I 1/ ω C

But I =V/Z. So Vc =

V

ω C √R2 + ωL –1/ ωC

=

2

To find the frequency at which Vc is maximum we have to differentiate Vc with respect to ω and equate it to zero

V2 .

VC2 = _________________________

2 C2[ R2 + ( L – 1/ C )2 ]

V2.

=

______________________________

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

2 R2 C2 + ( 2 L C – 1 )2

V2 [ 2 R2 C2 + 2 ( 2 L C – 1 ) ( 2 L C ) ]

d VC2

____

=

_____________________________________

d

=0

[ R C +( LC–1) ]

2

2

2

2

2 2

2R2C2 + 2( 2LC) (2LC- 1) =0

2 2 L2 C2 =2 LC - R2 C2

2 =1/ (LC - R2 / 2L2 )

Cmax= √ 1/LC – R2/2L2

rad/sec

fCmax = 1/2 √ 1/LC – R2 / 2L2 Hz

Expression for fLmax

The voltage across inductor VL is given by

VL = I XL = I (L)

But I = V/ Z

Hence VL =

V(L)

√ R2 + ( L – 1/ C)2

V22 L2

VL2 =

______________

R2 + ( L – 1/ C)2

= V2 4 L2 C2

______________

2R2C2 + (2LC- 1)2

Differentiating with respect to time and equating it to zero we get

dVL2/ d = 0 which simplifies to

22LC -2 R2C2 – 2 = 0

2 ( 2LC - R2C2) = 2

2 =

2

or fLmax =

1/ 2√ LC - R2C2 /2

2LC - R2C2

Example 1 :

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

60

0.5H

40F

A series RLC circuit shown in figure is connected

across an A.C. variable frequency supply of 200

votes. Calculate the resonant frequency and half –

power frequencies.

Solution:

fr=

200V,

1

=

1_____

f

=35.6Hz

2π√0.5x40x10 –6

2π√LC

Q= ωr L = 2πx35.6 x0.5

R

= 1.86

60

B.W = fr =

35.6

Q

= 19

1.86

f2- f1 =

19………………(1)

Also fr 2 = f1f2

(35.6) 2 = f1f2

=

1266…………..(2)

Solving equations (1) and (2) we get,

f1 = 27.33 Hz

f 2 = 46.33 Hz

Example 2:

20

Inductor

Capacitor

A 20 ohm resistor is connected in series with

an inductor, a capacitor and an Ammeter across

25 volts variable frequency a.c supply .When the

A

I

frequency is 400 Hz the current is at its maximum

value of 0.5 A and the potential difference across the

capacitor is 150 volts .Calculate

i)

The capacitances of the capacitor

ii)

The resistance and inductance of the inductor.

25V

Solution : Given Ir = 0.5 A, fr = 400Hz

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

(1)

We have V C =I 0 X C

X C = V C = 150

1

I0

0.5

= 300Ω

or C=

ω0 C

= 300 ohms

1

= 3.33 microfarad

300 ω0

(ii) At resonance circuit impedance is pure resistance given by Z =R +r =V

=25

Io

=50 Ω

0.5

Where r =Internal resistance of the inductor.

R =50 –R =50-20 =30 Ohms

At resonance XL =XC = 300 ohms

L= 300 = 300

ω0

= 0.119 henry

2π x 400

100

0.02H

0.02F

Example 3:

A Series RLC circuit consists of R= 100 ohms

L= 0.02H and C = 0.02 μF. Calculate frequency

of resonance. A variable frequency sinusoidal

voltage

of

rms

value

of

50

volts

is

applied

to

the

5

0V

circuit. Find the frequency at which voltage across L and C is maximum

Solution:

Given R=100 ohms,L =0.02H,C=0.02μF

(i) Resonant frequency fo = 1

________ =

2π √LC

1

——————

2π √0.02x0.02x10-6

fo = 7.957 KHz

(ii) The frequency at which voltage across C is maximum is given by

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

fC = 1 /2π √ 1/ ( LC – R2 / 2 L2 )

= 1 /2π √ (1/ 0.02 X 0.02 X 10-6 ) – ( 1002 ) / 2( 0.002)2

= 7.937 KHz

(iii) The frequency at which voltage across L is maximum is given by

fL =

1

2π √ LC – (R2 C2 / 2)

= 1 /2π √ (0.02 X 0.02 X 10-6 ) – ( 1002 ) ( 0.002 x 10-6)2 /2

= 7.977 KHz

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

Parallel Resonance

A parallel resonant circuit is one in which a coil and a capacitance are connected in parallel

across a variable frequency A.C. Supply. The response of a parallel resonant circuit is

somewhat different from that of a series resonant circuit.

I .A coil in parallel with a pure capacitor

R

L

Consider the parallel circuit shown in the figure.

Let ZL be the impedance of the coil given by ZL =R +j ω L

Then YL=1 =

1

= R-j ω L

ZL R +j ω L

R2+ ω2L2

Similarly let ZC = -j /

I

C

ωC

1 = jωC

ZC

Total admittance of the circuit = Y= YL + YC

YC

=

Y = R-j ω L

R2+ ω2L2

V

+ jωC

+ jωC -

R

R2+ ω2L2

ωL

R2+ ω2L2

At resonance the impedance ( or admittance) of the circuit is purely resistive( or conductive)

.For this to be true the j part of equation (1) should be zero.

ω 0C - ω 0L

R2+ ω 02 L

ω 0C

=

=0

2

ω 0L

R + ω 02 L

2

R2 +ω0 2 L

ω0 2 =

2

=

L/C - R2

L2

2

L

C

= 1 LC

R2

L2

f0 = 1/ 2 √ (1/LC – R2 / L2 )

Impedance at resonance

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

We know that at resonance the susceptive part of the admittance is zero.

Hence Y0 =

R

R2 +ω0 2 L 2

But R2 +ω0 2 L

2

= L/C

So Y0 = RC/L or Zo = L/RC

Where Zo is called the dynamic resistance. when coil resistance R is small, dynamic

resistance of the parallel circuit becomes high. Hence the current at resonance is minimum.

Hence this type of circuit is called rejector circuit.

Frequency –response characterisitics

The frequency response curve of a parallel resonant circuit is as

shown in the figure. We find that current is minimum at resonance. The half –power points

are given by the points at which the current is √2 Ir .From the above characteristic it is clear

that the characteristic is exactly opposite to that of series resonant.

I

2Ir

Ir

Frequency

f1

fr

f2

Quality factor ( Q-factor)

The quality factor of a parallel resonant circuit is defined as the current

magnification

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

Q = Current through capacitance at resonance

Total Current at resonance

= IC0 / I0

= V / ( 1/ 0C ) V / Z0

= Z00C = (L / RC) 0C

= 0L / R

Hence the expression for the Q- factor for both series and parallel resonant circuit are the

same

Also Band width= f0 / Q

II A coil and a Practical Capacitor in parallel

IL

Consider a parallel resonant circuit in which

the resistance of the capacitance is also considered

Impedance of the coil = ZL = RL + j L

YL = 1 / ZL = 1/ RL+j L

= RL – j L / RL2 +2L2

I

RL

XL

IC

RC

Impedance of the Capacitor = ZC = RC – j / C

= RC + j / C

XC

V

Rc2 +1/2C2

Therefore total admittance = Y=YL+YC

=( RL – j L / RL2 +2L2)+ RC + j / C

Rc2 +1/2C2

At resonance the susceptance part of the total admittance is zero, which gives

1/0C

0L

=

RC2 + 1/20C2

RL2 +20L2

1/LC [ RL2 +20L2] = 20[ RC2 + 1/20C2 ]

20 ( RC2 – L/C ) = RL2/ LC – 1/ C2

20 = 1/LC(RL2 – L/C )

( RC2 – L/C)

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

0 = 1/√ LC

f0 =

RL2 – L/C

√ ( RC2 – L/C)

( RL2 – L/C)

1

2 √ LC

( RC2 – L/C)

At Resonance the admittance is purely conductive given by

Y0 =

RL

RC

+

RL2 +20L2

RC2 + 1/20C2

Example 1 : Determine the value of RC in the

Shown in figure to yield Resonance

Solution: Let ZL be the impedance of the inductive branch

then ZL = 10+ j 10

RC

10

YL = 1/ (10 +j 10)

= 10 – j 10 = 10- j 20

102 +102

200

Let ZC be the impedance of the capacitive branch then

-j2

j10

ZC = RC – j 2

YC =

1

RC – j 2

=

RC – j 2

R C2 + 4

Total admittance of the circuit = Y = YL + YC

For the circuit under Resonance the Susceptance part is zero

( 2/ RC2 + 4) - (10 / 200) = 0

RC2 = 36

25

25

mH

RC = 6 ohms

Answer

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

Example 2: An Impedance coil of 25 ohms

Resistance and 25 mH inductance

is connected in parallel with a variable

capacitor. For what value of Capacitor

will the circuit resonate.If 90 volts,400

Hz source is used, what will be the line

Current under these conditions

Volts,400Hz

Solution:

C

90

0 = 2f0 = 2( 400)

ω0 2 = 1 LC

6.316 x 106 = 1 LC

R2

L2

R2

L2

1

= ω0 2 + R2

LC

L2

= 6.316 x 106 + 252 / (25 x 10-3)2

= 7.316 x 106

C= 5.467 F

Z0 = L/RC = (25 x 10-3)/ 25 x 5.467 x 10-6

= 182.89 ohms

I0 = V0/ Z0 = 90/ 182.89 = 0.492 ampere

Example 3: In a parallel resonant circuit

R, L and C are all in parallel

Half – power frequencies are

R

L

C

103 and 118 rad / sec respectively

The magnitude of impedance at

105 rad/ sec is 10 ohms.Find R,L and C

Solution : The given circuit is an ideal parallel resonantCircuit.

Total admittance= Y = YR + YL + YC

YR = 1/R

YL = 1/ j XL

YC = 1/ -j XC

So Y = 1/R + j (1/ XC - 1/ XL)

At Resonance the j part of the equation is zero

(1/ XC - 1/ XL)=0

XC= XL

1/ 2f0C =2f0L

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

Or f0= 1/ 2√ LC

Q= IC / I or IL / I is the current magnification

At Resonance Y0 = 1/ R or Z0 =R

Since (2 - 1) = 0/ Q

118 – 103 = 105 / Q

Q= 7

But Q= 0L / R

7= 105 x L / 10

L= 0.67 Henry

0= 1/√ LC

105= 1 / √ 0.67 x C

C=1.35 x 10-4 farard

Effect of Generator resistance on Band width and Selectivity

Rg

L

Ig

V

C

Rg

ZL

R

Consider parallel resonant circuit driven by a generator having internal resistance

Rg as shown in figure.

At anti- resonance the parallel resonant circuit behaves like a resistive network

Zr = L / CR

Q = rL / R = 1 / rRC

And B.W= f2 – f1= fr / Q

But now as the parallel circuit is driven by a generator having internal

resistance(Rg)

Which comes in parallel with Zr at resonance.

Hence the total impedance becomes Zr’ = Rg11 Zr

= Rg11( L / CR)

Rg L

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

=

= L / C( R+ L/ CRg)-----------(1)

RgCR+L

From equation (1) it is clear that driving a parallel resonant circuit with a

Generator having internal Rg is nothing but to increase a resistance in series

With an inductor by value L /RgC

Hence Quality factor of parallel circuit driven by generator with internal

Resistance Rg is given by

Q’ = rL

R+ L / RgC

= ( rL / R)

( 1+ L/CR)

Rg

Q’ =

Q0

( 1 + Zr / Rg)

Bandwidth = B.W= fr / Q’ = fr ( 1+ Zr / Rg )

Q

’

B.W = B.W ( 1+ Zr / Rg)

100 k

Example 4: A coil of 10 henry and Resistance

of 10 ohm is in parallel with 100

picofarad capacitor.The combination

10 H

is connected across a generator of 100

volts, having internal resistance 100 k

100

Volts

100

Determine (i)Voltage across the ckt

picofarad

10

(ii)Band-width

ohm

Solution:

fr = 1/ 2 √ (1/LC – R2 / L2 )

= 1/ 2√( 1 / 10 x 100 x 10-12 )– (102 / 102)

= 5.032 khZ

Dynamic resistance =Zr= L / CR

= 10 / 100 x 10-12 x 10 = 1010 ohms

Q=rL / R

= 2 x 5.032 x 103 x10

10

= 31617

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

100 k

100 V

Zr

(i)Voltage across parallel circuit at Resonance = 100 x 1010

1010 + 100 x103

= 100 volts

(ii) Band width = fr / Q [ 1+ Zr / Rg)

5.032 x 103 { 1 + 1010 / 100 x 103 }

31617

= 15.91 KHz

=

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

TRANSIENT RESPONSE

Electrical circuits are connected to supply by closing the switch and disconnected

from the supply by opening the switch. This switching operation will change the

current and voltage in the device.

A purely resistive device will allow instantaneous change in current and voltage.

An inductive device will not allow sudden change in current or delay the change in

current.

A capacitive device will not allow sudden change in voltage or delay the change in

voltage.

Hence when switching operation is performed in inductive or capacitive device the current

and voltage in the device will take a certain time to change from preswitching value to steady

value after switching. This study of switching condition in network is called transient

analysis. The state (or condition) of the current from the instant of switching to attainment of

steady state is called transient state or transient. The current and voltage of circuit elements

during transient period is called transient response.

The transient may also occur due to variation in circuit elements. Transient analysis is an

useful tool in electrical engineering for analysis of switching conditions in Circuit

breakers, Relays, Generators etc.

It is also useful for the analysis of faulty conditions in electrical devices. Transient analysis is

also useful for analyzing switching Conditions in analog and digital Electronic devices.

R

R-L Series circuit transient:

Consider The R-L series circuit shown in the fig. Switch K

is closed at t=0. Referring to the circuit, balance equation

ldit

using Kirchoff’s law can be written as V t Ri t

dt

Taking Laplace Transform we get

V s

Is R LSIs i0

s

Assuming there is no stored energy in the inductor

I(0)=0

V s

RIs LSIs

s

K

t=0

L

i(t)

V

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

V s

V s

1

Is

R

SR SL

L

S S

L

A

B

Is

S SR

L

R

V s

A S BS

L

L

R V s

A

Put s=0

L

L

V s

A

R

V s

R

R

S

B

put

L

L

L

V s

B

R

V s 1

1

Therefore Is

R S S R

L

Taking inverse Laplace we get

R

t

V

it

1 e L

R

The equation clearly indicates transient nature of current, which is also shown in

figure.

L

Tune constant of the circuit, which is denoted by Z given in seconds.

Where

R

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

Hence

it

V

1 e

R

Z

t

V

V

Where

= steady state current. Hence Time

R

R

constant for an R-L series current circuit is defined as the time taken by the circuit to

reach 63.2% of its final steady value.

Putting t=z we get

i(z) = 0.632

R-C series circuit Transient

Consider the RC circuit shown. Let the switch be closed at t=0.

Writing the balance equation using Kirchoff’s voltage law ,

1

v t iR i dt

c

Taking Laplace transform, we get

V s

1 Is Q 0

IsR

S

c s

s

Let us assume that there is no stored energy in the circuit.

Q o =0

Hence

V s

Is

1

IsR

IsR

s

CS

CS

V s

1

Is

R S 1

RC

Taking Laplace inverse we get

1

V t RC t

it

e

R

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

The sketch of transient current is shown in figure Where

the circuit. Putting

1

the time constant of

RC

1

in the current equation we get

RC

V

R

Hence time constant of RC series current can be defined as the time taken by

current transient to fall to 36.7% of its initial value.

i(z) = 0.367

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

Example 1:

In the circuit shown in figure the switch ‘K’ is moved from position 1 to position 2 at

time t = 0. The steady state current having been previously established in R-L circuit.

Find the current i(t) after switching.

Solution:

From the given data the circuit is under steady state when switch K is in position 1

10

under steady state condition inductance is a short and hence i(0) =

= 1 Amp.

10

When the circuit is switched to position 2, this 1 Amp current constituted the stored

energy in the coil.

Writing the balance equation for position 2 we get 20i 4

di

0

dt

Taking Laplace transformation

20Is 4s Is i0 0

20Is 4s Is 1

4

1

Is

4s 5 s 5

taking inverse Laplace we get

it e5 t

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

Example 2:

A series R-C circuit is shown in figure. The capacitor has an initial charge of

800µCoulombs on its plates, at the time the switch is closed. Find the resulting

current transient.

Solution: From the data given q(0) = 800 106 C

Writing the balance equation we get

1

100 10it

i(t )dt

4 106

Taking Laplace transformation

100

1

I(s) Q(0)

10I(s)

S

4 10 6 S

106 100 800 10 6

I(s)10

4S

S

4 10 6 S

100 200

5

40S 106 30

I(s)

4S

S

1200

1200

I(s)

6

40S 10

106

40 S

40

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

30

S 25000

Taking Inverse Laplace we get

i( t ) 30e25000 t

I(s)

Example3:

For the circuit shown in figure the relay coil is adjusted to operate at a current of 5

Amps. Switch K is closed at t = 0 and the relay is found to operate at t = 0.347

seconds. Find the value of inductance ‘L’ of the relay.

Soln: Writing the balance equation for the relay circuit

di

V( t ) Ri( t ) L

dt

Applying Laplace transformation

V( s)

RI(S) LSI(S) i(0)

S

Since there is no mention of initial current in the coil i(0) =0

10

I(s) I(s)LS

Hence

S

10

I(S)SL 1

S

10

10

A

B

L

I(s)

1 S

1

S1 SL

S S

S

L

L

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

10

1

A S BS

L

L

A=10 B= -10

10

I(S) 10

1

S

L

Taking Inverse Laplace we get

t

L

i( t ) 10 10e

The relay operates at t = 0.347 seconds when the current value reaches 5A. Hence

5 10 10e

0.347

10e L

0.347

L

10 5 5

0.347

5

e L

Solving the equation we get

L=0.5H

Example 4:

In figure the switch ‘K’ is closed. Find the time when the current in the circuitry

reaches to 500 mA

Soln: When the switch is closed Vc (0) = 0

When the switch is closed at t = 0

I1 (t)×50 = 10

I2 ( t ) 70

1

10

100 10 6 i2dt

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

Taking Laplace for both the equations

10

0. 2

I1(S)

(1)

50S

5

1 I (s) 10

I2 (S) 70 2

c S

5

I2 (S)

10

70I2 (s)

6

100 10 s 5

10

1

1

1

I2 (S)

'

(2)

4

3

70S 10

7s 10 7 S 142.86

Taking inverse Laplace for equation (1) and (2)

I1 (t) =0.2 A

1

I2 ( t ) e 142.86 t

7

Total current from the battery i(t) =I1 + I2

1

i( t ) 0.2 e142.86 t

7

when this current reaches 500 mA

1

500 10 3 0.2 e142.86 t

7

-3

Solving we get t = 5.19 × 10 Seconds.

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

R-L-C Series Transient circuit:

Assuming zero initial conditions when switch K is closed the balanced equation is

di 1

given by V iR L idt

dt C

Taking Laplace transformation we get

V ( s)

I(s)

1(s)R LSI(s)

s

CS

1

I(s)R SL

CS

V( s)

V ( s)

L

I(s)

1

R

1

S(R SL

) S2 S

CS

L

LC

The time response of the circuit depends on the poles or roots of the characteristic

equation

R

1

S2 S

0

L LC

Roots of the characteristic equation are given by

2

R

1

R

4

L

LC

L

S1, S 2

2

2

R

1

R

S1, S2

2L

2L LC

2

1

R

Case1: If

the roots S1 and S2 are real positive and unequal.

LC

2L

The response of such a case is called is known as over damped.

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

2

1

R

Case 2 : If

the root S1 and S2 are complex conjugate the response of

LC

2L

such a case is called as undamped.

2

1

R

Case 3 : If

then the roots S1 and S2 are complex conjugate. The

LC

2L

response of such a case is called as under damped.

Example 5 :

A circuit is made up of an inductance of 10 H, a resistance of 2000 Ω and a capacitance

of 15.62 µF all connected in series. A voltage of 100 Volts is suddenly applied across this

circuit. Calculate the circuit current. What is its maximum Value?

Soln : At t = 0 switch ‘K’ is closed. There is no initial inductor current and capacitor

voltage.

di( t ) 1

it R L

it dt 100

dt

c

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

Taking Laplace transformation we get

106

100

I(s)2000 10SI(s)

15.625

s

31240s 156.252 106 100

I(s)

15.625

s

10

1562

I(s)

2

2

156.2 s 200s 6402

S 200s 6402

2

S + 200s +6402=0 is the characteristic equation

S1

200 2002 4 6402

40

2

200 2002 4 6400

160

2

S2 200S 6402 S 40S 160

10

K1

K2

I(s)

S 40S 160 S 40 S 160

K1=0.0833 and K2=-0.0833

1

1

I(s) 0.0833

S 40 S 160

Taking inverse Laplace

i( t ) 0.0833 e40 t e160 t

S2

To find the maximum value of i(t)

di d

0.0833 e 40 t e160 t

dt dt

di

0

for i(t) to be maximum

dt

0.0833 [ 40e 40 t 160e 160 t ] 0

e40t 4e160t 0

e40t

4 e120t 4

160 t

e

Solving we get t = 0.0166 seconds

Substituting this value of ' t ' in the current equation we get

imax 0.0833 [e400.0166 e1600.0166 ]

imax = 0.04A

Prof.R.V. Srinivasa Murthy, Assistant Professor, Dept. of E & C, A.P.S. College of Engineering

Bangalore

(*) In the R-L-C circuit the capacitor has an initial voltage of 40 Volts when the switch

is closed at t=0 find an expression for the current.

Solution : Writing the balance equation for the circuit

1

40 100

2I(s) 10sI(s)

I

(

s

)

4S

S

S

1 100 40

I(s)2 10S

4S

S

S

60

S

I(s)

6

S 0.25 0.025

1

4S

Hence the characteristic equation is

S2+0.25+0.025=0

2 10S

2

0.2 0.22 4 0.025

0.1 j0.1225

2