* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download Low Voltage Low Power constant-gm Rail to

Audio power wikipedia , lookup

Electric power system wikipedia , lookup

Flip-flop (electronics) wikipedia , lookup

Electrical ballast wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Power over Ethernet wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Three-phase electric power wikipedia , lookup

Power engineering wikipedia , lookup

Electrical substation wikipedia , lookup

Power inverter wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

History of electric power transmission wikipedia , lookup

Current source wikipedia , lookup

Stray voltage wikipedia , lookup

Surge protector wikipedia , lookup

Power MOSFET wikipedia , lookup

Voltage regulator wikipedia , lookup

Power electronics wikipedia , lookup

Voltage optimisation wikipedia , lookup

Schmitt trigger wikipedia , lookup

Buck converter wikipedia , lookup

Alternating current wikipedia , lookup

Mains electricity wikipedia , lookup

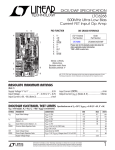

Low Voltage Low Power constant - gm Rail to Rail CMOS Op-Amp with Overlapped Transition Regions ECEN 5007 9/3/02 Vishwas Ganesan Motivation Low Supply Voltage Operation Constant gm Low power consumption making it suitable for portable applications. Reduced chip area. Why this paper came up ? Complementary differential pairs operate in parallel. This leads to one pair turned on and one off when input is near rails and both pairs on at the middle of the input range leading to gm being twice the value than the former case Other Circuit Proposals 1. 2. 3. 4. Variation in the tail current in the differential paper doubling gm when only one pair is active. Comparing currents from p and n differential pairs and the maximum current between them is selected and processed for gm constant by maximum-selecting circuitry. Current bleed circuits Square root circuit Difficulties with other circuits Increase in slew rate due to increase in tail current. Extra circuitry – Signal processing circuits and many more current mirrors. All this leads to complication, Power consumption and more die. Complementary Input Stage Gm is constant if √ (βnIsn) + √ (βpIsp) = constant Cutoff : Isn = 0 Vss ≤ Vcm ≤ Vn- Transition Isn = Isn ( Vcm ) Vn- < Vcm ≤ Vn+ Saturation Isn = ßMBn ( VGMBn – Vss – Vt n) 2 Vn+ < Vcm ≤ Vdd General Transition graph This shows the transition region overlap of a general n-p differential pair. Design Lower boundary of the transition region : Vn- = Vss + Vtn + VDSMBn Neglecting VDSMBn we get Vn- ≈ Vss + Vtn Upper boundary of the transition region VDGMBN = - Vtn VDGMBn = Vn+ - Vtn - √(Isno/ßM1n) – VGMBn We get Vn+ = VGMBn + √ (Isno/ ßM1n) Deriving expression for Isn : Isn = ßM1n ( Vcm – VDMBN – Vtn ) 2 eqn 1 Isn = ßMBn ( VGMBn – Vss – Vtn – VDMBN – Vss ) ( VDMBn – Vss ) Assuming ßMBn = 2 ßM1n and solving for VDMBn from above VDMBn =Vcm+VGMBn– Vtn –½√ [2(-Vtn+VGMBn-Vss)2 –(Vcm-VGMBn)2] Using this in eqn 1 Isn=ßM1n[(Vcm–VGMBn)/2+1/2√(2(-Vtn+VGMBN–Vss)2 –(VCM-VGMBn)2)2 Design Similarly for Pmos Vp+ = Vdd + Vtp Vp-=VGMBp - √Ispo/ßM1p Isp=ßM1p[(-Vcm+VGMBp)/2+1/2√(2(Vtp–VGMBP+Vdd)2–(VCM-VGMBp)2]2 To overlap the transition regions of the n and p pairs we equate Vp- = Vn- and Vn+ = Vp+ Also we assume symmetry between the pairs and so Ispo = Isno , ßM1p = ßM1n , VGMBn = - VGMBp and Vtp = - Vtn Solving we get ßM1n = ßM1p = Isno/(Vdd + Vtp – VGMBN)2 Complementary Input Stage with DC Level Shifter Use a dc level shifter to shift the p-transition curve leftward to overlap the n-transition curve. Vshift small gm exceeds normal limit Vshift large gm drops below limit ∆ Voptimal yields constant Gm 2VGMBN<∆Voptimal< 2VGMBN+ √(Isno/βM1) Plot Of gm vs Vcm OPAMP Circuit OPAMP Implementation 1. 2. 3. 4. DC level shifters implemented by 2 pairs of PMOS source followers MS1-MS4 Three stages Complementary input stage Folded cascoded stage M21-M28 provides high gain Class AB output stage M30-M33 MB1 and MB11 are biasing transistors. Frequency Response Amplitudes and phase plots show unstability due to varying gm. My simulation results Input offset voltage 30 mV Power dissipation .36 mW Output Voltage swing 1.1 V to -1V Simulation plots Paper Results Input offset voltage 3 mV Power dissipation .31 mW OpAmp area .12 mm2 Output Voltage swing Vss + 0.04 to Vdd – 0.07 V Conclusions DC level shifters can be used to overlap transition regions to obtain constant gm. Low Power dissipation was achieved Low supply voltages . There is considerable gain achieved leading to CMRR improvement.