4-channel sampling chip doc

... -1 DC Tests. Goals: Measure Vdd current vs biasing voltage for all test blocks. Disable, enable blocks one by one. Compare with simulations. Test card: use packaged chips and DC inputs, some LEMOs to check the test structures. -2 AC Tests. Goals: Measure the AC performance of the test structures. RO ...

... -1 DC Tests. Goals: Measure Vdd current vs biasing voltage for all test blocks. Disable, enable blocks one by one. Compare with simulations. Test card: use packaged chips and DC inputs, some LEMOs to check the test structures. -2 AC Tests. Goals: Measure the AC performance of the test structures. RO ...

1346KB

... Output during AT, Pattern end output, Output by communication command, Heating/Cooling control output OUT2 (for EV2 option only) For Event output EV1/EV2, Heater burnout alarm output and Output by communication command are available when C5W, EIW, C5 or W option is ordered. (*4) For the BCS2, 2 poin ...

... Output during AT, Pattern end output, Output by communication command, Heating/Cooling control output OUT2 (for EV2 option only) For Event output EV1/EV2, Heater burnout alarm output and Output by communication command are available when C5W, EIW, C5 or W option is ordered. (*4) For the BCS2, 2 poin ...

FXMAR2104 Dual-Supply, 4-Bit Voltage Translator / Isolator for Open-Drain and Push-Pull Applications

... specification voltage levels. Eight internal 10KΩ pull-up resistors are integrated. The device is designed so that the A port tracks the VCCA level and the B port tracks the VCCB level. This allows for bi-directional A/B port voltage translation between any two levels from 1.65V to 5.5V. VCCA can eq ...

... specification voltage levels. Eight internal 10KΩ pull-up resistors are integrated. The device is designed so that the A port tracks the VCCA level and the B port tracks the VCCB level. This allows for bi-directional A/B port voltage translation between any two levels from 1.65V to 5.5V. VCCA can eq ...

AD2S81A/AD2S82A: Variable Resolution, Monolithic Resolver-to-Digital Converters Data Sheet

... The converters allow users to select their own dynamic performance with external components. This allows the users great flexibility in defining the converter that best suits their system requirements. The AD2S82A allows users to select the resolution to be 10, 12, 14 or 16 bits and to track resolve ...

... The converters allow users to select their own dynamic performance with external components. This allows the users great flexibility in defining the converter that best suits their system requirements. The AD2S82A allows users to select the resolution to be 10, 12, 14 or 16 bits and to track resolve ...

BDTIC www.BDTIC.com/infineon Power Management & Multimarket

... means of the inputs D0...D7 without any additional logic signal. The IC can replace 8 optocouplers and the 8 high-side switches in conventional I/O-Applications as a galvanic isolation is implemented by means of the integrated coreless transformer technology. The µC compatible interface allows a dir ...

... means of the inputs D0...D7 without any additional logic signal. The IC can replace 8 optocouplers and the 8 high-side switches in conventional I/O-Applications as a galvanic isolation is implemented by means of the integrated coreless transformer technology. The µC compatible interface allows a dir ...

Rev. PrG

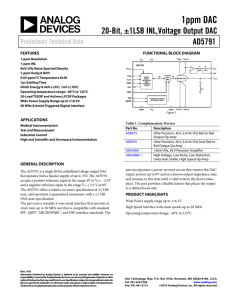

... Active Low input. Asserting this pin sets the DAC register to a user defined value (See Table 11) and updates the DAC output. The output value will depend on the DAC register coding that is being used, either binary or 2scomplement. Active low Load DAC logic input, This is used to update the DAC reg ...

... Active Low input. Asserting this pin sets the DAC register to a user defined value (See Table 11) and updates the DAC output. The output value will depend on the DAC register coding that is being used, either binary or 2scomplement. Active low Load DAC logic input, This is used to update the DAC reg ...

Datasheet - Integrated Device Technology

... The ICS853S9252I is a 2.5V/3.3V ECL/LVPECL fanout buffer designed for high-speed, low phase-noise wireless infrastructure applications. The device fanouts a differential input signal to two ECL/LVPECL outputs. Optimized for low additive phase-noise, sub-100ps output rise and fall times, low output s ...

... The ICS853S9252I is a 2.5V/3.3V ECL/LVPECL fanout buffer designed for high-speed, low phase-noise wireless infrastructure applications. The device fanouts a differential input signal to two ECL/LVPECL outputs. Optimized for low additive phase-noise, sub-100ps output rise and fall times, low output s ...

Multivibrators - Slot Tech Forum

... the one you don’t want to use. Others may have an Enable (high or low level) that must be present before the trigger is applied. Some chips have one input with a Schmitt Trigger design to the circuit that allows clean triggering from dirty or slowly changing input signals. Retriggerable Normally, on ...

... the one you don’t want to use. Others may have an Enable (high or low level) that must be present before the trigger is applied. Some chips have one input with a Schmitt Trigger design to the circuit that allows clean triggering from dirty or slowly changing input signals. Retriggerable Normally, on ...

11.3 Gbps Optical Receiver ADN3010-11

... TIA that provides guaranteed performance and improved manufacturing reliability. The 50 μm diameter photodetector enables an easy optical coupling design when aligned with a single mode fiber (SMF). With a 1310 nm optimized ARC, the ADN3010-11 supports 10GBASE-LR and other applications with extended ...

... TIA that provides guaranteed performance and improved manufacturing reliability. The 50 μm diameter photodetector enables an easy optical coupling design when aligned with a single mode fiber (SMF). With a 1310 nm optimized ARC, the ADN3010-11 supports 10GBASE-LR and other applications with extended ...

hxlvdsr - Honeywell

... These are the common enable control signals. As shown in Truth Table, the combination of EN = L and EN* = H puts the outputs into the high impedance state. The outputs are enabled for all other combinations of EN and EN*. R IN1 – R IN4 These are LVDS differential input pins. ...

... These are the common enable control signals. As shown in Truth Table, the combination of EN = L and EN* = H puts the outputs into the high impedance state. The outputs are enabled for all other combinations of EN and EN*. R IN1 – R IN4 These are LVDS differential input pins. ...

AN21 - Composite Amplifiers

... gain, similar to Q1 and Q2 in Figure 11. Q7-Q10 form the output buffer stage. The feedback scheme is identical to Figure 11’s, with summing action at the Q3-Q4 emitter connection. To obtain maximum bandwidth, quiescent current is quite high. Without closed-loop control, the circuit will quickly go i ...

... gain, similar to Q1 and Q2 in Figure 11. Q7-Q10 form the output buffer stage. The feedback scheme is identical to Figure 11’s, with summing action at the Q3-Q4 emitter connection. To obtain maximum bandwidth, quiescent current is quite high. Without closed-loop control, the circuit will quickly go i ...

OP-AMP

... • Input Offset Voltage- Even when there is no input voltage the Op-Amp gives off a small voltage. This can be canceled out by use of the Offset Null pin on the chip. (Non-Ideal) • Common Mode Rejection Ratio (CMRR)Ability of an Op-Amp to reject a signal applied to both inputs simultaneously. ...

... • Input Offset Voltage- Even when there is no input voltage the Op-Amp gives off a small voltage. This can be canceled out by use of the Offset Null pin on the chip. (Non-Ideal) • Common Mode Rejection Ratio (CMRR)Ability of an Op-Amp to reject a signal applied to both inputs simultaneously. ...

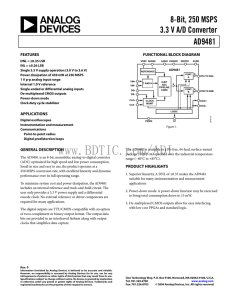

8-Bit, 250 MSPS 3.3 V A/D Converter AD9481

... The AD9481 is an 8-bit, monolithic analog-to-digital converter (ADC) optimized for high speed and low power consumption. Small in size and easy to use, the product operates at a 250 MSPS conversion rate, with excellent linearity and dynamic performance over its full operating range. To minimize syst ...

... The AD9481 is an 8-bit, monolithic analog-to-digital converter (ADC) optimized for high speed and low power consumption. Small in size and easy to use, the product operates at a 250 MSPS conversion rate, with excellent linearity and dynamic performance over its full operating range. To minimize syst ...

DMS-40PC Series - Murata Power Solutions

... The DMS-40PC’s simplified schematic, shown in Figure 1, can be very useful when debugging a malfunctioning circuit, especially if the user has some knowledge of operational amplifiers (op amps). The meter’s high-impedance input consists of an op amp powered from a ±5Vdc power supply (the –5V is intern ...

... The DMS-40PC’s simplified schematic, shown in Figure 1, can be very useful when debugging a malfunctioning circuit, especially if the user has some knowledge of operational amplifiers (op amps). The meter’s high-impedance input consists of an op amp powered from a ±5Vdc power supply (the –5V is intern ...

AD7666 数据手册DataSheet下载

... When SER/PAR is LOW, this output is used as Bit 8 of the parallel port data output bus. When SER/PAR is HIGH, this output, part of the serial port, is used as a serial data output synchronized to SCLK. Conversion results are stored in an on-chip register. The AD7666 provides the conversion result, M ...

... When SER/PAR is LOW, this output is used as Bit 8 of the parallel port data output bus. When SER/PAR is HIGH, this output, part of the serial port, is used as a serial data output synchronized to SCLK. Conversion results are stored in an on-chip register. The AD7666 provides the conversion result, M ...

Study the characteristics of negative feedback amplifiers and design

... As the frequency of input signal is changed, the control voltage will change correspondingly, so as to lock the output frequency to the input frequency. As a result, there is a change of phase difference between the two signals away from 90˚. ...

... As the frequency of input signal is changed, the control voltage will change correspondingly, so as to lock the output frequency to the input frequency. As a result, there is a change of phase difference between the two signals away from 90˚. ...

74VHC161284 IEEE 1284 Transceiver 7 4

... standards for bidirectional parallel communications between personal computers and printing peripherals ...

... standards for bidirectional parallel communications between personal computers and printing peripherals ...

Manual - Ashly Audio

... Note: The VCM-88E will remember the last level settings when the AC power is switched off and will restore these settings on power-up. Master Attenuation Control - This control attenuates all eight channels uniformly, and was designed as a simple means of turning down all eight audio channels n the ...

... Note: The VCM-88E will remember the last level settings when the AC power is switched off and will restore these settings on power-up. Master Attenuation Control - This control attenuates all eight channels uniformly, and was designed as a simple means of turning down all eight audio channels n the ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.