AD7671 数据手册DataSheet下载

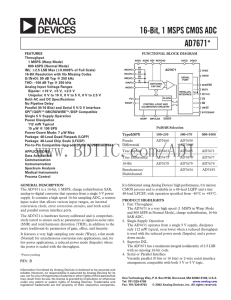

... When SER/PAR is LOW, this output is used as Bit 8 of the Parallel Port Data Output Bus. When SER/PAR is HIGH, this output, part of the Serial Port, is used as a serial data output synchronized to SCLK. Conversion results are stored in an on-chip register. The AD7671 provides the conversion result, M ...

... When SER/PAR is LOW, this output is used as Bit 8 of the Parallel Port Data Output Bus. When SER/PAR is HIGH, this output, part of the Serial Port, is used as a serial data output synchronized to SCLK. Conversion results are stored in an on-chip register. The AD7671 provides the conversion result, M ...

MT-076 TUTORIAL Differential Driver Analysis

... product design or the use or application of customers’ products or for any infringements of patents or rights of others which may result from Analog Devices assistance. All trademarks and logos are property of their respective holders. Information furnished by Analog Devices applications and develop ...

... product design or the use or application of customers’ products or for any infringements of patents or rights of others which may result from Analog Devices assistance. All trademarks and logos are property of their respective holders. Information furnished by Analog Devices applications and develop ...

CMX469A 1200/2400/4800 Baud FFSK/MSK Modem

... 2400/4800 Hz respectively. Tone frequencies are phase continuous; transitions occur at the zero crossing point. A common Xtal oscillator with a choice of two clock frequencies (1.008MHz or 4.032MHz) provides baud-rate, transmit frequencies, and Rx and Tx synchronization. The transmitter and receiver ...

... 2400/4800 Hz respectively. Tone frequencies are phase continuous; transitions occur at the zero crossing point. A common Xtal oscillator with a choice of two clock frequencies (1.008MHz or 4.032MHz) provides baud-rate, transmit frequencies, and Rx and Tx synchronization. The transmitter and receiver ...

ADM3232E 数据手册DataSheet 下载

... Internally Generated Positive Supply (6 V Nominal). External Capacitor 2 is connected between these pins. A 0.1 μF capacitor is recommended, but larger capacitors of up to 47 μF can be used. Internally Generated Negative Supply (−6 V Nominal). Transmitter (Driver) Outputs. These are RS-232 signal le ...

... Internally Generated Positive Supply (6 V Nominal). External Capacitor 2 is connected between these pins. A 0.1 μF capacitor is recommended, but larger capacitors of up to 47 μF can be used. Internally Generated Negative Supply (−6 V Nominal). Transmitter (Driver) Outputs. These are RS-232 signal le ...

AD1974 数据手册DataSheet下载

... PLL is not being used, it is highly recommended that an independent crystal oscillator generate the master clock. In addition, it is especially important that the clock signal should not be passed through an FPGA, CPLD, DSP, or other large digital chip before being applied to the AD1974. In most cas ...

... PLL is not being used, it is highly recommended that an independent crystal oscillator generate the master clock. In addition, it is especially important that the clock signal should not be passed through an FPGA, CPLD, DSP, or other large digital chip before being applied to the AD1974. In most cas ...

MAX1181 Dual 10-Bit, 80Msps, 3V, Low-Power ADC General Description

... input amplifiers. The converters may also be operated with single-ended inputs. In addition to low operating power, the MAX1181 features a 2.8mA sleep mode, as well as a 1µA power-down mode to conserve power during idle periods. An internal 2.048V precision bandgap reference sets the full-scale rang ...

... input amplifiers. The converters may also be operated with single-ended inputs. In addition to low operating power, the MAX1181 features a 2.8mA sleep mode, as well as a 1µA power-down mode to conserve power during idle periods. An internal 2.048V precision bandgap reference sets the full-scale rang ...

Inputs Currents for High-Resolution ADCs

... Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant ...

... Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant ...

realization of ternary-logic based shift up, shift down using mosfet

... Volume 4, Issue 4, July-August, 2013, pp. 240-247 © IAEME: www.iaeme.com/ijecet.asp Journal Impact Factor (2013): 5.8896 (Calculated by GISI) ...

... Volume 4, Issue 4, July-August, 2013, pp. 240-247 © IAEME: www.iaeme.com/ijecet.asp Journal Impact Factor (2013): 5.8896 (Calculated by GISI) ...

MAX19527 Evaluation Kit Evaluates: General Description Features

... 5) Connect the output of the signal bandpass filters to the IN_ SMA connectors. It is recommended that a 3dB or 6dB attenuation pad be used to reduce reflections and distortion from the bandpass filter. ...

... 5) Connect the output of the signal bandpass filters to the IN_ SMA connectors. It is recommended that a 3dB or 6dB attenuation pad be used to reduce reflections and distortion from the bandpass filter. ...

23-delay line

... • The amplitude and duration Tp of the output pulse is controlled by the monostable circuits . • Hence,a monostable circuit can be used as pulse delay device as well as pulse reshaping device. ...

... • The amplitude and duration Tp of the output pulse is controlled by the monostable circuits . • Hence,a monostable circuit can be used as pulse delay device as well as pulse reshaping device. ...

MAX5441–MAX5444 +3V/+5V, Serial-Input, Voltage-Output, 16-Bit DACs General Description

... MAX5442/MAX5444 to code 32768 when VDD is first applied. This ensures that unwanted DAC output voltages will not occur immediately following a system power-up, such as after a loss of power. ...

... MAX5442/MAX5444 to code 32768 when VDD is first applied. This ensures that unwanted DAC output voltages will not occur immediately following a system power-up, such as after a loss of power. ...

MAX3982 SFP Copper-Cable Preemphasis Driver General Description Features

... Figure 1. Illustration of Tx Preemphasis in dB ...

... Figure 1. Illustration of Tx Preemphasis in dB ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.