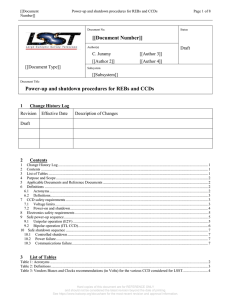

LCA-XXX-CCD-REB

... with the recommended sequence. Conversely, powering down should be separated into powering down of the CCD, followed by the Electronics Board. In particular, this allows to power down the CCD temporarily (i.e., in a lab setting, when it is exposed to ambient light), while leaving the electronics rea ...

... with the recommended sequence. Conversely, powering down should be separated into powering down of the CCD, followed by the Electronics Board. In particular, this allows to power down the CCD temporarily (i.e., in a lab setting, when it is exposed to ambient light), while leaving the electronics rea ...

Chapter 6

... DPTL is static, because the output defining nodes are always connected to either VDD or GND via low-resistance path (good for noise) Design is very modular, which makes designing a library of gates simple. More complex gates can be built by cascading the modules. Some routing overhead due to c ...

... DPTL is static, because the output defining nodes are always connected to either VDD or GND via low-resistance path (good for noise) Design is very modular, which makes designing a library of gates simple. More complex gates can be built by cascading the modules. Some routing overhead due to c ...

Boolean Algebra and Logic Gates

... ◦ Even the output, which is either logic `1’ or `0’, is represented by distinct voltage levels. ◦ There are three fundamental logical operations from which all other Boolean functions, no matter how complex, can be derived. ◦ These operations are implemented by three basic gates: AND, OR, and NOT. ◦ ...

... ◦ Even the output, which is either logic `1’ or `0’, is represented by distinct voltage levels. ◦ There are three fundamental logical operations from which all other Boolean functions, no matter how complex, can be derived. ◦ These operations are implemented by three basic gates: AND, OR, and NOT. ◦ ...

General Specifications UT75A Digital Indicating Controller

... 0.00 to 999.59 (hour.minute or minute. second) 0 to 999, CONT (limitless number of times) Can be set the upper-side wait zone and the lower zone for program setpoint. ...

... 0.00 to 999.59 (hour.minute or minute. second) 0 to 999, CONT (limitless number of times) Can be set the upper-side wait zone and the lower zone for program setpoint. ...

DATA SHEET PCF8575C Remote 16-bit I/O expander for I

... The 16 ports (see Fig.3) are entirely independent and can be used either as input or output ports. Input data is transferred from the ports to the microcontroller in the READ mode (see Fig.6). Output data is transmitted to the ports in the WRITE mode (see Fig.5). This quasi-bidirectional I/O can be ...

... The 16 ports (see Fig.3) are entirely independent and can be used either as input or output ports. Input data is transferred from the ports to the microcontroller in the READ mode (see Fig.6). Output data is transmitted to the ports in the WRITE mode (see Fig.5). This quasi-bidirectional I/O can be ...

doc - Ignitech

... HARDWARE Pick up system. Ignition can have maximal four channels. Ignition can be programmed for many pickup systems. Most of them can be choose directly from list in program RACING3.EXE others can be set by special procedure (also by program RACING3.EXE). Supply voltage +12 V. Supply voltage must b ...

... HARDWARE Pick up system. Ignition can have maximal four channels. Ignition can be programmed for many pickup systems. Most of them can be choose directly from list in program RACING3.EXE others can be set by special procedure (also by program RACING3.EXE). Supply voltage +12 V. Supply voltage must b ...

LT5568-2 - GSM/EDGE Optimized, High Linearity Direct Quadrature Modulator.

... using differential baseband I and Q signals. It supports GSM, EDGE, CDMA, CDMA2000 and other systems that operate in the 850MHz to 965MHz band. It may be configured as an image reject upconverting mixer, by applying 90° phase-shifted signals to the I and Q inputs. The I/Q baseband inputs consist of v ...

... using differential baseband I and Q signals. It supports GSM, EDGE, CDMA, CDMA2000 and other systems that operate in the 850MHz to 965MHz band. It may be configured as an image reject upconverting mixer, by applying 90° phase-shifted signals to the I and Q inputs. The I/Q baseband inputs consist of v ...

High Voltage, Precision Difference Amplifier AD8209

... resistor network attenuates the common-mode signal by a ratio of 1/14. The A1 amplifier inputs are held within the power supply range, even as Pin 1 and Pin 8 exceed the supply or fall below the common (ground). A reference voltage of 350 mV biases the attenuator above ground, allowing Amplifier A1 ...

... resistor network attenuates the common-mode signal by a ratio of 1/14. The A1 amplifier inputs are held within the power supply range, even as Pin 1 and Pin 8 exceed the supply or fall below the common (ground). A reference voltage of 350 mV biases the attenuator above ground, allowing Amplifier A1 ...

MAX3460–MAX3464 +5V, Fail-Safe, 20Mbps, Profibus RS-485/ RS-422 Transceivers General Description

... The MAX3460–MAX3464 are high-speed differential bus transceivers for RS-485 and RS-422 communications. They are designed to meet TIA/EIA-422-B, TIA/EIA-485-A, V.11, and X.27 standards. The transceiver complies with the Profibus specification providing +2.1V output level with a 54Ω load, 20Mbps data ...

... The MAX3460–MAX3464 are high-speed differential bus transceivers for RS-485 and RS-422 communications. They are designed to meet TIA/EIA-422-B, TIA/EIA-485-A, V.11, and X.27 standards. The transceiver complies with the Profibus specification providing +2.1V output level with a 54Ω load, 20Mbps data ...

DS4M125/DS4M133/DS4M200 3.3V Margining Clock Oscillator with LVPECL/LVDS Output General Description

... clock oscillator. The circuit can generate the following frequencies and their ±5% frequency deviations: 125MHz, 133.33MHz, and 200MHz. The DS4M125/ DS4M133/DS4M200 employ a low-jitter PLL to generate the frequencies. The typical phase jitter is less than 0.9ps RMS from 12kHz to 20MHz. Frequency mar ...

... clock oscillator. The circuit can generate the following frequencies and their ±5% frequency deviations: 125MHz, 133.33MHz, and 200MHz. The DS4M125/ DS4M133/DS4M200 employ a low-jitter PLL to generate the frequencies. The typical phase jitter is less than 0.9ps RMS from 12kHz to 20MHz. Frequency mar ...

AD637 数据手册DataSheet 下载

... true rms of any input signal. An averaging error, the magnitude of which is dependent on the value of the averaging capacitor, is present at low frequencies. For example, if the filter capacitor, CAV, is 4 μF, the error is 0.1% at 10 Hz and increases to 1% at 3 Hz. To measure ac signals, the AD637 c ...

... true rms of any input signal. An averaging error, the magnitude of which is dependent on the value of the averaging capacitor, is present at low frequencies. For example, if the filter capacitor, CAV, is 4 μF, the error is 0.1% at 10 Hz and increases to 1% at 3 Hz. To measure ac signals, the AD637 c ...

On-Chip Techniques for Electromagnetic Interference (EMI)

... other [2]. As microprocessor speeds increase, reducing Electromagnetic Interference becomes an essential part of design considerations. This radiation, mainly produced by fundamental and low-order harmonics, unfortunately coincides and interferes with other signals. The energy concentrated at the di ...

... other [2]. As microprocessor speeds increase, reducing Electromagnetic Interference becomes an essential part of design considerations. This radiation, mainly produced by fundamental and low-order harmonics, unfortunately coincides and interferes with other signals. The energy concentrated at the di ...

LT1019 - Precision Reference

... approximately 2.1mV/°C. Room temperature voltage is therefore approximately (295°K)(2.1mV/°C) = 620mV. This voltage varies with process parameters and should not be used to measure absolute temperature, but rather relative temperature changes. Previous bandgap references have been very sensitive to ...

... approximately 2.1mV/°C. Room temperature voltage is therefore approximately (295°K)(2.1mV/°C) = 620mV. This voltage varies with process parameters and should not be used to measure absolute temperature, but rather relative temperature changes. Previous bandgap references have been very sensitive to ...

LTC1392 - Micropower Temperature, Power Supply and Differential

... MSB-First/LSB-First (MSBF) The output data of the LTC1392 is programmed for MSB-first or LSB-first sequence using the MSBF bit. When the MSBF bit is a logical one, data will appear on the DOUT line in MSB-first format. Logical zeros will be filled in indefinitely following the last data bit to accom ...

... MSB-First/LSB-First (MSBF) The output data of the LTC1392 is programmed for MSB-first or LSB-first sequence using the MSBF bit. When the MSBF bit is a logical one, data will appear on the DOUT line in MSB-first format. Logical zeros will be filled in indefinitely following the last data bit to accom ...

MXL1543B +5V Multiprotocol, 3Tx/3Rx, Software- Selectable Clock/Data Transceivers General Description

... V.28 (RS-232), V.10/V.11 (RS-449/V.36, EIA-530, EIA530A, X.21), and V.35 protocols. The MXL1543B transceivers carry the high-speed clock and data signals while the MXL1544/MAX3175 carry the control signals. The MXL1543B can be terminated by the MXL1344A software-selectable resistor termination netwo ...

... V.28 (RS-232), V.10/V.11 (RS-449/V.36, EIA-530, EIA530A, X.21), and V.35 protocols. The MXL1543B transceivers carry the high-speed clock and data signals while the MXL1544/MAX3175 carry the control signals. The MXL1543B can be terminated by the MXL1344A software-selectable resistor termination netwo ...

How Oscilloscope Probes Affect Your Measurement

... edges and tighter margins, so the designer has to make the effort to model, run simulations, and validate the design. When you spend that much time and effort in the design process, you don’t want to second-guess the measurement system or spend additional time troubleshooting due to measurement inac ...

... edges and tighter margins, so the designer has to make the effort to model, run simulations, and validate the design. When you spend that much time and effort in the design process, you don’t want to second-guess the measurement system or spend additional time troubleshooting due to measurement inac ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.