3 V/5 V, 2 MSPS, 8-Bit, 8-Channel ADC AD7829-1 FEATURES

... data onto the data bus. The signal is internally gated with the CS signal. Both RD and CS must be logic low to enable the data bus. Channel Address Inputs. The address of the next multiplexer channel must be present on these inputs when the RD signal goes low. Data Output Lines. They are normally he ...

... data onto the data bus. The signal is internally gated with the CS signal. Both RD and CS must be logic low to enable the data bus. Channel Address Inputs. The address of the next multiplexer channel must be present on these inputs when the RD signal goes low. Data Output Lines. They are normally he ...

PremiSys - IDenticard

... o Sixteen general-purpose input points that can be used with supervision and can fulfill any input-point function: door-input points, request-to-exit points, motion-sensor inputs, etc. o Two dedicated input points for monitoring power loss to the board and enclosure tampering o Two relays configurab ...

... o Sixteen general-purpose input points that can be used with supervision and can fulfill any input-point function: door-input points, request-to-exit points, motion-sensor inputs, etc. o Two dedicated input points for monitoring power loss to the board and enclosure tampering o Two relays configurab ...

YR80.242 - PULS Power Supply

... The redundancy module has two input channels which are completely independent from each other. Each control circuit, auxiliary voltage source, or other circuitry in the module are designed separately for each input. The dual input redundancy module can be considered as two single redundancy modules ...

... The redundancy module has two input channels which are completely independent from each other. Each control circuit, auxiliary voltage source, or other circuitry in the module are designed separately for each input. The dual input redundancy module can be considered as two single redundancy modules ...

MAX1191 Ultra-Low-Power, 7.5Msps, Dual 8-Bit ADC General Description Features

... power-down modes to conserve power during idle periods. Excellent dynamic performance, ultra-low power, and small size make the MAX1191 ideal for applications in imaging, instrumentation, and digital communications. An internal 1.024V precision bandgap reference sets the full-scale range of the ADC ...

... power-down modes to conserve power during idle periods. Excellent dynamic performance, ultra-low power, and small size make the MAX1191 ideal for applications in imaging, instrumentation, and digital communications. An internal 1.024V precision bandgap reference sets the full-scale range of the ADC ...

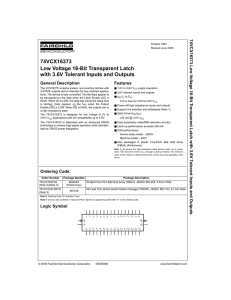

74VCX16373 Low Voltage 16-Bit Transparent Latch with 3.6V Tolerant Inputs and Outputs 7

... The 74VCX16373 contains sixteen edge D-type latches with 3-STATE outputs. The device is byte controlled with each byte functioning identically, but independent of the other. Control pins can be shorted together to obtain full 16-bit operation. The following description applies to each byte. When th ...

... The 74VCX16373 contains sixteen edge D-type latches with 3-STATE outputs. The device is byte controlled with each byte functioning identically, but independent of the other. Control pins can be shorted together to obtain full 16-bit operation. The following description applies to each byte. When th ...

Built-In System Protection for Industrial Drives

... TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI ...

... TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI ...

A 7.2 GSa/s, 14 bit or 12 GSa/s, 12 bit Signal Generator on a Chip in

... differential input clock is received on 25 Ω lines and terminated on-chip. This impedance allows use of a clock balun with 50 Ω differential output impedance. The nominal input clock power is +7 dBm to keep the thermal noise floor below the noise floor needed for the goal of −160 dBc/Hz for the broa ...

... differential input clock is received on 25 Ω lines and terminated on-chip. This impedance allows use of a clock balun with 50 Ω differential output impedance. The nominal input clock power is +7 dBm to keep the thermal noise floor below the noise floor needed for the goal of −160 dBc/Hz for the broa ...

Fairchild’s Process Enhancements Eliminate the CMOS SCR Latch-Up Problem In 74HC Logic

... overall SCR loop gain greater than one, and hence enable the SCR to trigger. The actual equations to show quantitatively how the resistors effect the SCR’s behavior could be derived, but it is sufficient to notice that as R1 and R2 become smaller the SCR becomes harder to turn on. IC designers utili ...

... overall SCR loop gain greater than one, and hence enable the SCR to trigger. The actual equations to show quantitatively how the resistors effect the SCR’s behavior could be derived, but it is sufficient to notice that as R1 and R2 become smaller the SCR becomes harder to turn on. IC designers utili ...

74LVXC3245 8-Bit Dual Supply Configurable Voltage Interface Transceiver with 3-STATE Outputs 7

... port. The VCCB pin accepts a 3V-to-5V supply level. The B Port is configured to track the VCCB supply level respectively. A 5V level on the VCC pin will configure the I/O pins at a 5V level and a 3V VCC will configure the I/O pins at a 3V level. The A Port should interface with a 3V host system and ...

... port. The VCCB pin accepts a 3V-to-5V supply level. The B Port is configured to track the VCCB supply level respectively. A 5V level on the VCC pin will configure the I/O pins at a 5V level and a 3V VCC will configure the I/O pins at a 3V level. The A Port should interface with a 3V host system and ...

DS90C241 5-35MHz DC-Balanced 24-Bit FPD

... Meets AEC-Q100 compliance Power supply range 3.3V ± 10% 48-pin TQFP package ...

... Meets AEC-Q100 compliance Power supply range 3.3V ± 10% 48-pin TQFP package ...

Chapter 18 - La Sierra University

... Op amp circuits with negative feedback The inverting amplifier is a basic configuration in which the noninverting input is grounded (sometimes through a resistor to balance the bias inputs). Again, the difference between Vin and Vf is very small due to feedback; this implies that the inverting input ...

... Op amp circuits with negative feedback The inverting amplifier is a basic configuration in which the noninverting input is grounded (sometimes through a resistor to balance the bias inputs). Again, the difference between Vin and Vf is very small due to feedback; this implies that the inverting input ...

MAX5812 12-Bit Low-Power, 2-Wire, Serial Voltage-Output DAC General Description

... and a serial clock line (SCL). The MAX5812 is SMBus compatible within the range of VDD = 2.7V to 3.6V. SDA and SCL facilitate bidirectional communication between the MAX5812 and the master at rates up to 400kHz. Figure 1 shows the 2-wire interface timing diagram. The MAX5812 is a transmit/receive sl ...

... and a serial clock line (SCL). The MAX5812 is SMBus compatible within the range of VDD = 2.7V to 3.6V. SDA and SCL facilitate bidirectional communication between the MAX5812 and the master at rates up to 400kHz. Figure 1 shows the 2-wire interface timing diagram. The MAX5812 is a transmit/receive sl ...

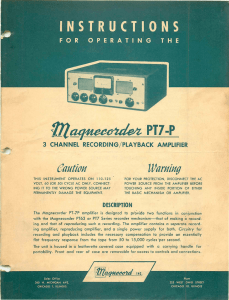

eautioll Warllillg - technicalaudio.com

... Having set up the PTA 3 , amplifier with the basic recorder unit as indicated above, a number of steps should be followed. 1. To make a recording, a suitable input must be connected to the recording amplifier. This may be done by use of anyone, or all, of the bridging or microphone inputs. The micro ...

... Having set up the PTA 3 , amplifier with the basic recorder unit as indicated above, a number of steps should be followed. 1. To make a recording, a suitable input must be connected to the recording amplifier. This may be done by use of anyone, or all, of the bridging or microphone inputs. The micro ...

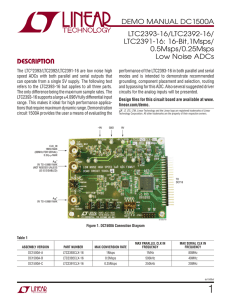

Manual - Linear Technology

... source, along with a sinusoidal generator at a frequency of 20kHz. The input signal level is approximately –1dBfs. The input is filtered with a 20kHz single pole RC filter shown in Figure 5. The FFT shown in the data sheet is a 16384-point FFT. A typical FFT obtained with DC1500A is shown in Figure 6. ...

... source, along with a sinusoidal generator at a frequency of 20kHz. The input signal level is approximately –1dBfs. The input is filtered with a 20kHz single pole RC filter shown in Figure 5. The FFT shown in the data sheet is a 16384-point FFT. A typical FFT obtained with DC1500A is shown in Figure 6. ...

SN54AHCT123A, SN74AHCT123A (Rev. G)

... high-level-active (B) input. Pulse duration can be reduced by taking CLR low. CLR input can be used to override A or B inputs. The input/output timing diagram illustrates pulse control by retriggering the inputs and early clearing. The variance in output pulse duration from device to device typicall ...

... high-level-active (B) input. Pulse duration can be reduced by taking CLR low. CLR input can be used to override A or B inputs. The input/output timing diagram illustrates pulse control by retriggering the inputs and early clearing. The variance in output pulse duration from device to device typicall ...

AD9259 数据手册DataSheet下载

... The AD9259 is a quad, 14-bit, 50 MSPS analog-to-digital converter (ADC) with an on-chip sample-and-hold circuit designed for low cost, low power, small size, and ease of use. The product operates at a conversion rate of up to 50 MSPS and is optimized for outstanding dynamic performance and low power ...

... The AD9259 is a quad, 14-bit, 50 MSPS analog-to-digital converter (ADC) with an on-chip sample-and-hold circuit designed for low cost, low power, small size, and ease of use. The product operates at a conversion rate of up to 50 MSPS and is optimized for outstanding dynamic performance and low power ...

MXL1543 +5V Multiprotocol, 3Tx/3Rx, Software- Selectable Clock/Data Transceivers General Description

... The MXL1543 is a three-driver/three-receiver multiprotocol transceiver that operates from a +5V single supply. The MXL1543, along with the MXL1544/MAX3175 and the MXL1344A, form a complete software-selectable data terminal equipment (DTE) or data communication equipment (DCE) interface port that sup ...

... The MXL1543 is a three-driver/three-receiver multiprotocol transceiver that operates from a +5V single supply. The MXL1543, along with the MXL1544/MAX3175 and the MXL1344A, form a complete software-selectable data terminal equipment (DTE) or data communication equipment (DCE) interface port that sup ...

W65C21S6TPG-14 [ w65c21s ]

... The active low Interrupt Request lines (IRQAB and IRQBB) act to interrupt the microprocessor either directly or through external interrupt priority circuitry. These lines are open drain and are capable of sinking 3.2 milliamps from an external source. This permits all interrupt request lines to be t ...

... The active low Interrupt Request lines (IRQAB and IRQBB) act to interrupt the microprocessor either directly or through external interrupt priority circuitry. These lines are open drain and are capable of sinking 3.2 milliamps from an external source. This permits all interrupt request lines to be t ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.

![W65C21S6TPG-14 [ w65c21s ]](http://s1.studyres.com/store/data/007889516_2-74103b76aafb3d292c61274e0bf5d9c7-300x300.png)