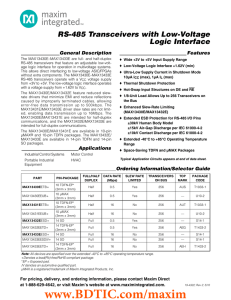

RS-485 Transceivers with Low-Voltage Logic Interface General Description Features

... Storage Temperature Range .............................-65°C to +150°C Lead Temperature (soldering, 10s) .................................+300°C Soldering Temperature (reflow) .......................................+260°C ...

... Storage Temperature Range .............................-65°C to +150°C Lead Temperature (soldering, 10s) .................................+300°C Soldering Temperature (reflow) .......................................+260°C ...

LM111JAN Voltage Comparator (Rev. B)

... When a high-speed comparator such as the LM111 is used with fast input signals and low source impedances, the output response will normally be fast and stable, assuming that the power supplies have been bypassed (with 0.1 μF disc capacitors), and that the output signal is routed well away from the i ...

... When a high-speed comparator such as the LM111 is used with fast input signals and low source impedances, the output response will normally be fast and stable, assuming that the power supplies have been bypassed (with 0.1 μF disc capacitors), and that the output signal is routed well away from the i ...

STM6522

... reset push-button closures do not cause system resets as the extended Smart Reset™ delay setup periods are implemented. Once the valid Smart Reset™ input levels and setup delay are met, the device generates an output reset pulse for a fixed timeout period (tREC). The typical application hookup shows ...

... reset push-button closures do not cause system resets as the extended Smart Reset™ delay setup periods are implemented. Once the valid Smart Reset™ input levels and setup delay are met, the device generates an output reset pulse for a fixed timeout period (tREC). The typical application hookup shows ...

Chapter 2 LITERATURE REVIEW 2. Chapter Overview This chapter

... motors. Both type of motors offer similar opportunities for precise positioning, but they differ in a number of ways. Servomotors require analogue feedback control systems of some type. Typically, this involves a potentiometer to provide feedback about the rotor position, and some mix of circuitry t ...

... motors. Both type of motors offer similar opportunities for precise positioning, but they differ in a number of ways. Servomotors require analogue feedback control systems of some type. Typically, this involves a potentiometer to provide feedback about the rotor position, and some mix of circuitry t ...

LT5524

... Note 1: Absolute Maximum Ratings are those values beyond which the life of the device may be impaired. Note 2: All voltage values are with respect to ground. Note 3: Default state for open PGA inputs. Note 4: VCC1 and VCC2 (Pins 2 and 19) are internally connected. Note 5: External VOSUP is adjusted ...

... Note 1: Absolute Maximum Ratings are those values beyond which the life of the device may be impaired. Note 2: All voltage values are with respect to ground. Note 3: Default state for open PGA inputs. Note 4: VCC1 and VCC2 (Pins 2 and 19) are internally connected. Note 5: External VOSUP is adjusted ...

ADM485E 数据手册DataSheet 下载

... data transceivers with ±15 kV ESD protection suitable for halfduplex communication on multipoint bus transmission lines. They are designed for balanced data transmission and comply with Telecommunication Industry Association/Electronics Industries Association (TIA/EIA) standards RS-485 and RS-422. T ...

... data transceivers with ±15 kV ESD protection suitable for halfduplex communication on multipoint bus transmission lines. They are designed for balanced data transmission and comply with Telecommunication Industry Association/Electronics Industries Association (TIA/EIA) standards RS-485 and RS-422. T ...

DU-45MV 50/100/200mV DC Full Scale 4 1/2 Digit with 0.56” LEDs

... This meter is supplied with plug-in type screw terminal connectors. The power supply pins (14 & 15) have a unique plug and socket outline to prevent cross connection. (see DU Connectors) ...

... This meter is supplied with plug-in type screw terminal connectors. The power supply pins (14 & 15) have a unique plug and socket outline to prevent cross connection. (see DU Connectors) ...

idt74cbtlv16292 - Integrated Device Technology

... 1. The propagation delay is the calculated RC time constant of the typical on-state resistance of the switch and the specified load capacitance when driven by an ideal voltage source (zero output impedance). 2. The condition to measure this propagation delay is by observing the change of voltage on ...

... 1. The propagation delay is the calculated RC time constant of the typical on-state resistance of the switch and the specified load capacitance when driven by an ideal voltage source (zero output impedance). 2. The condition to measure this propagation delay is by observing the change of voltage on ...

Features • - megaslides.es

... operation. The seven following bits are used for the register address and the eight last ones are the write data. For both address and data, the most significant bit is the first one. In case of a read operation, SPI_DOUT provides the contents of the read register, MSB first. The transfer is enabled ...

... operation. The seven following bits are used for the register address and the eight last ones are the write data. For both address and data, the most significant bit is the first one. In case of a read operation, SPI_DOUT provides the contents of the read register, MSB first. The transfer is enabled ...

Embedded Systems - Ulster University

... Bit 13 SIDL only relevant in idle mode Bit 10-8 FORM<2:0> 000 = 16 bit Data out – bottom 10 bits are the reading Bit 7-5 SSRC<2:0> 000 = clearing SAMP bit ends sampling and starts conversion Bit 4 CLRASAM 0 = normal, buffer get overwritten by next conversion sequence Bit 2 ASAM 1 = sampling begins a ...

... Bit 13 SIDL only relevant in idle mode Bit 10-8 FORM<2:0> 000 = 16 bit Data out – bottom 10 bits are the reading Bit 7-5 SSRC<2:0> 000 = clearing SAMP bit ends sampling and starts conversion Bit 4 CLRASAM 0 = normal, buffer get overwritten by next conversion sequence Bit 2 ASAM 1 = sampling begins a ...

EC0323 COMMUNICATION LAB II LABORATORY MANUAL SEMESTER V

... An important feature of pulse-amplitude modulation is a conservation of time. That is, for a given message signal, transmission of the associated PAM wave engages the communication channel for only a fraction of the sampling interval on a periodic basis. Hence, some of the time interval between adja ...

... An important feature of pulse-amplitude modulation is a conservation of time. That is, for a given message signal, transmission of the associated PAM wave engages the communication channel for only a fraction of the sampling interval on a periodic basis. Hence, some of the time interval between adja ...

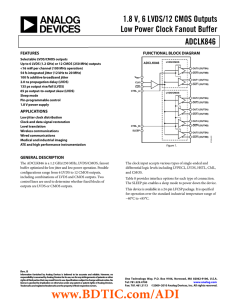

1.8 V, 6 LVDS/12 CMOS Outputs Low Power Clock Fanout Buffer ADCLK846

... Each channel bank is pin programmable for either LVDS or CMOS levels. This allows the selection of multiple logic configurations ranging from 6 LVDS to 12 CMOS outputs, along with other combinations using both types of logic. ...

... Each channel bank is pin programmable for either LVDS or CMOS levels. This allows the selection of multiple logic configurations ranging from 6 LVDS to 12 CMOS outputs, along with other combinations using both types of logic. ...

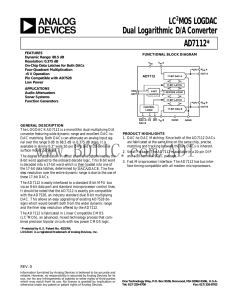

AD7112 数据手册DataSheet 下载

... alongside an analog signal track. Establish a single point analog ground (star ground) separate from the logic system ground. Place this ground as close as possible to the AD7112. Connect all analog grounds to this star ground, and also connect the AD7112 DGND to this ground. Do not connect any othe ...

... alongside an analog signal track. Establish a single point analog ground (star ground) separate from the logic system ground. Place this ground as close as possible to the AD7112. Connect all analog grounds to this star ground, and also connect the AD7112 DGND to this ground. Do not connect any othe ...

OPA353 OPA2353 OPA4353 High-Speed, Single-Supply, Rail-to-Rail

... OPA353 series extends 100mV beyond the supply rails. This is achieved with a complementary input stage—an N-channel input differential pair in parallel with a P-channel differential pair (see Figure 2). The N-channel pair is active for input voltages close to the positive rail, typically (V+) – 1.8V ...

... OPA353 series extends 100mV beyond the supply rails. This is achieved with a complementary input stage—an N-channel input differential pair in parallel with a P-channel differential pair (see Figure 2). The N-channel pair is active for input voltages close to the positive rail, typically (V+) – 1.8V ...

3.3 V Hex inverter

... 1. Stresses beyond those listed may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not implied. Exposure to absolute-maximum-rated condition ...

... 1. Stresses beyond those listed may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not implied. Exposure to absolute-maximum-rated condition ...

AD7843

... ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to ...

... ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to ...

ECN33550 FP (PDF format, 406kBytes)

... (1) Hitachi Power Semiconductor Device, Ltd. warrants performance of its power semiconductor products (hereinafter called “products”) to the specifications applicable at the time of sale in accordance with this specification document. Testing and other quality control techniques are utilized to the ...

... (1) Hitachi Power Semiconductor Device, Ltd. warrants performance of its power semiconductor products (hereinafter called “products”) to the specifications applicable at the time of sale in accordance with this specification document. Testing and other quality control techniques are utilized to the ...

ADC128S102QML-SP Radiation Hardened 8

... When the input voltage at any pin exceeds the power supplies (that is, VIN less than AGND or VIN greater than VA or VD), the current at that pin should be limited to 10 mA. The 20 mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an inpu ...

... When the input voltage at any pin exceeds the power supplies (that is, VIN less than AGND or VIN greater than VA or VD), the current at that pin should be limited to 10 mA. The 20 mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an inpu ...

Tap Tempo LFO datasheet

... If the WAVE DISTORT CV input is not required, it can be tied to a fixed voltage. For a square wave output, this should be 2.5V. This can be produced by a pair of 10K resistors wired as a potential divider between 0V and +5V. If the LEVEL CV input is not required, it can be disabled by tying the inpu ...

... If the WAVE DISTORT CV input is not required, it can be tied to a fixed voltage. For a square wave output, this should be 2.5V. This can be produced by a pair of 10K resistors wired as a potential divider between 0V and +5V. If the LEVEL CV input is not required, it can be disabled by tying the inpu ...

CD54ACT20 数据资料 dataSheet 下载

... B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control. C. All input pulses are supplied by generators ...

... B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control. C. All input pulses are supplied by generators ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.