Institutionen för systemteknik

... home systems and tracking systems. As the application of WSN grows by leaps and bounds, there is an increasing demand in placing a larger number of sensors and controllers to meet the requirements. The increased number of sensors necessitates flexibility in the functioning of nodes. Nodes in wireles ...

... home systems and tracking systems. As the application of WSN grows by leaps and bounds, there is an increasing demand in placing a larger number of sensors and controllers to meet the requirements. The increased number of sensors necessitates flexibility in the functioning of nodes. Nodes in wireles ...

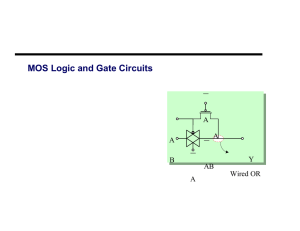

DYNAMIC LOGIC

... Non-ratioed - sizing of the devices does not affect the logic levels Faster switching speeds » reduced load capacitance due to lower input capacitance (Cin) » reduced load capacitance due to smaller output loading (Cout) » no Isc, so all the current provided by PDN goes into discharging CL ...

... Non-ratioed - sizing of the devices does not affect the logic levels Faster switching speeds » reduced load capacitance due to lower input capacitance (Cin) » reduced load capacitance due to smaller output loading (Cout) » no Isc, so all the current provided by PDN goes into discharging CL ...

XAPP231

... XAPP230, "The LVDS I/O Standard" for a discussion of transmission lines and terminations used in LVDS. The multi-drop Virtex-E LVDS line driver adheres to all the standard ANSI/TIA/ EIA-644 LVDS Interface Standard DC input levels as specified in Table 2. The output common-mode voltage typically aver ...

... XAPP230, "The LVDS I/O Standard" for a discussion of transmission lines and terminations used in LVDS. The multi-drop Virtex-E LVDS line driver adheres to all the standard ANSI/TIA/ EIA-644 LVDS Interface Standard DC input levels as specified in Table 2. The output common-mode voltage typically aver ...

CS 2204 Fall 2005

... • If outputs are used during the glitch time, erroneous results will occur A glitch for a circuit happens only if the a specific input combination is applied first and then another specific input combination is applied • For all other input combination pairs, it does not happen • For the 2-to-1 MU ...

... • If outputs are used during the glitch time, erroneous results will occur A glitch for a circuit happens only if the a specific input combination is applied first and then another specific input combination is applied • For all other input combination pairs, it does not happen • For the 2-to-1 MU ...

TEM - glast lat

... • Maxim part screening must be carefully done to assure that the testing provides valid verification reliability. Documented methods by Maxim are for static burn-in only (diffusion based issues) and do not represent the actual operational case planned for GLAST. In that the GLAST application is actu ...

... • Maxim part screening must be carefully done to assure that the testing provides valid verification reliability. Documented methods by Maxim are for static burn-in only (diffusion based issues) and do not represent the actual operational case planned for GLAST. In that the GLAST application is actu ...

SmartFusion cSoC: DC Fan Control Using PWM

... the voltage is increased. The advantage of this method is that voltage will always be applied to the fan. Thus, at any given time the tachometer (tacho) signal can be present and measured. This is not possible in the pulse width modulator (PWM) control technique. The disadvantages of this method are ...

... the voltage is increased. The advantage of this method is that voltage will always be applied to the fan. Thus, at any given time the tachometer (tacho) signal can be present and measured. This is not possible in the pulse width modulator (PWM) control technique. The disadvantages of this method are ...

How to Select Little Logic (Rev. A)

... SN74LVCxG Little Logic Devices SN74LVC1G/2G/3G Little Logic components are designed with no clamp diodes to VCC on either inputs or outputs, making the interface voltage higher than applied VCC. This design allows the down translation from 5 V to a desired lower switch level, which refers to supply ...

... SN74LVCxG Little Logic Devices SN74LVC1G/2G/3G Little Logic components are designed with no clamp diodes to VCC on either inputs or outputs, making the interface voltage higher than applied VCC. This design allows the down translation from 5 V to a desired lower switch level, which refers to supply ...

IOSR Journal of VLSI and Signal Processing (IOSR-JVSP)

... comparable to the binary circuits. Proposed here a quaternary lookup table (LUT) structure, and compared with binary LUTs for performance optimization. The circuit is designed with standard CMOS processes, employing single voltage supply designed using voltage-mode structures. Presented in this work ...

... comparable to the binary circuits. Proposed here a quaternary lookup table (LUT) structure, and compared with binary LUTs for performance optimization. The circuit is designed with standard CMOS processes, employing single voltage supply designed using voltage-mode structures. Presented in this work ...

Power Methodology Guide

... This power estimation and analysis methodology guide covers in a single document all power effects you may encounter while designing your FPGA logic and integrating it onto your system. It presents the electrical and physical factors, internal or external to the FPGA, which affect power. It then pro ...

... This power estimation and analysis methodology guide covers in a single document all power effects you may encounter while designing your FPGA logic and integrating it onto your system. It presents the electrical and physical factors, internal or external to the FPGA, which affect power. It then pro ...

Field-programmable gate array

A field-programmable gate array (FPGA) is an integrated circuit designed to be configured by a customer or a designer after manufacturing – hence ""field-programmable"". The FPGA configuration is generally specified using a hardware description language (HDL), similar to that used for an application-specific integrated circuit (ASIC). (Circuit diagrams were previously used to specify the configuration, as they were for ASICs, but this is increasingly rare.)FPGAs contain an array of programmable logic blocks, and a hierarchy of reconfigurable interconnects that allow the blocks to be ""wired together"", like many logic gates that can be inter-wired in different configurations. Logic blocks can be configured to perform complex combinational functions, or merely simple logic gates like AND and XOR. In most FPGAs, logic blocks also include memory elements, which may be simple flip-flops or more complete blocks of memory.