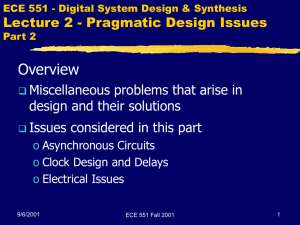

Lecture_2_f01_p2

... inputs can cause bizarre latch and flip-flop behavior: o Hanging for a time at a threshold level o Produce a damped oscillation ...

... inputs can cause bizarre latch and flip-flop behavior: o Hanging for a time at a threshold level o Produce a damped oscillation ...

Basic Digital Circuits

... In a digital system there are only two stable states, logic 1 and 0 (or HIGH and LOW, TRUE and FALSE, etc.) In a popular logic family called TTL (Transistor-Transistor Logic), the low logic level is assigned to 0V and the high logic level is assigned to 5V (see Section 3.10 of Wakerly’s Digital Desi ...

... In a digital system there are only two stable states, logic 1 and 0 (or HIGH and LOW, TRUE and FALSE, etc.) In a popular logic family called TTL (Transistor-Transistor Logic), the low logic level is assigned to 0V and the high logic level is assigned to 5V (see Section 3.10 of Wakerly’s Digital Desi ...

CPLD I/O User Guide

... The CoolRunner XPLA3 has a half latch feature on the I/Os. The half latch is essentially a pull-up that turns on only when the I/O pin voltage is in the linear region (not a 0, not a 1). So, when the voltage at the pin is in the trip-point region or higher, the half latch is enabled. The idea is tha ...

... The CoolRunner XPLA3 has a half latch feature on the I/Os. The half latch is essentially a pull-up that turns on only when the I/O pin voltage is in the linear region (not a 0, not a 1). So, when the voltage at the pin is in the trip-point region or higher, the half latch is enabled. The idea is tha ...

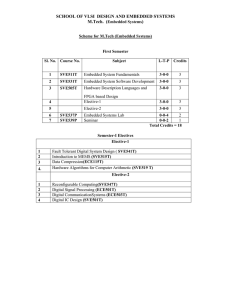

SCHOOL OF VLSI DESIGN AND EMBEDDED SYSTEMS

... Verilog constructs, synthesis design flow- RTL to gates, translation, un-optimized intermediate representations, logic optimization, technology mapping and optimization, technology library, design constraints, optimized gate level description. ...

... Verilog constructs, synthesis design flow- RTL to gates, translation, un-optimized intermediate representations, logic optimization, technology mapping and optimization, technology library, design constraints, optimized gate level description. ...

Design of 8-bit Ripple Carry Adder Using Constant Delay

... pull-down network (PDN) are conducting current simultaneously. If PDN is off, then the output quickly rises to logic “1.” In this case, FTL’s critical path is always a single pMOS transistor. Despite its performance advantage, FTL suffers from reduced noise margin, excess direct path current, and no ...

... pull-down network (PDN) are conducting current simultaneously. If PDN is off, then the output quickly rises to logic “1.” In this case, FTL’s critical path is always a single pMOS transistor. Despite its performance advantage, FTL suffers from reduced noise margin, excess direct path current, and no ...

UXN6M9M Datasheet 9 GHz Divide-by

... aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the worl ...

... aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the worl ...

CPLD Course Draft - System Safety Society

... Anti-fuse (fuse technology also exists) ▪ One-time programmable device ▪ An anti-fuse is a high impedance contact (Open State) until it has a relatively high voltage applied to it which turns it into a low-impedance ...

... Anti-fuse (fuse technology also exists) ▪ One-time programmable device ▪ An anti-fuse is a high impedance contact (Open State) until it has a relatively high voltage applied to it which turns it into a low-impedance ...

DOC - Picosecond Timing Project

... routed individually to the four time stretcher chips. The Acquire Clocks will be at a frequency 16 times that of the Master Clock (for Master Clock = 62.5MHz, Acquire Clock = 1.0GHz). A fifth output, the Reference Clock, will be created that is at a frequency four times that of the Master Clock (for ...

... routed individually to the four time stretcher chips. The Acquire Clocks will be at a frequency 16 times that of the Master Clock (for Master Clock = 62.5MHz, Acquire Clock = 1.0GHz). A fifth output, the Reference Clock, will be created that is at a frequency four times that of the Master Clock (for ...

1 - Concordia University

... Cascading dynamic gates of the type described will result in malfunction of the circuit. Consider two simple inverters connected in series, as shown in Figure 8. The problem is that during precharge all outputs are being precharged to 1. The PDN of the second gate is thus in a conducting state at th ...

... Cascading dynamic gates of the type described will result in malfunction of the circuit. Consider two simple inverters connected in series, as shown in Figure 8. The problem is that during precharge all outputs are being precharged to 1. The PDN of the second gate is thus in a conducting state at th ...

Field-programmable gate array

A field-programmable gate array (FPGA) is an integrated circuit designed to be configured by a customer or a designer after manufacturing – hence ""field-programmable"". The FPGA configuration is generally specified using a hardware description language (HDL), similar to that used for an application-specific integrated circuit (ASIC). (Circuit diagrams were previously used to specify the configuration, as they were for ASICs, but this is increasingly rare.)FPGAs contain an array of programmable logic blocks, and a hierarchy of reconfigurable interconnects that allow the blocks to be ""wired together"", like many logic gates that can be inter-wired in different configurations. Logic blocks can be configured to perform complex combinational functions, or merely simple logic gates like AND and XOR. In most FPGAs, logic blocks also include memory elements, which may be simple flip-flops or more complete blocks of memory.