TRU - JYU Trac Help

... that the FPGA can handle the data. The ADC is working with 40MHz, it can sample the incoming data every 25ns. After that it provides 12 bit digital signal from data. ...

... that the FPGA can handle the data. The ADC is working with 40MHz, it can sample the incoming data every 25ns. After that it provides 12 bit digital signal from data. ...

Digital Logic Design 1 Introduction Sum-of

... • Faulty power supply – ICs will not operate or will operate erratically. – May lose regulation due to an internal fault or because circuits are drawing too much current. – Always verify that power supplies are providing the specified range of voltages and are properly ...

... • Faulty power supply – ICs will not operate or will operate erratically. – May lose regulation due to an internal fault or because circuits are drawing too much current. – Always verify that power supplies are providing the specified range of voltages and are properly ...

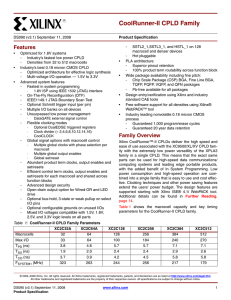

CoolRunner-II CPLD Family Data Sheet

... CPLD families use a sense amplifier approach to creating product terms, which always has a residual current component being drawn. This residual current can be several hundred milliamps, making them unusable in portable systems. CoolRunner-II CPLDs use standard CMOS methods to create the CPLD archit ...

... CPLD families use a sense amplifier approach to creating product terms, which always has a residual current component being drawn. This residual current can be several hundred milliamps, making them unusable in portable systems. CoolRunner-II CPLDs use standard CMOS methods to create the CPLD archit ...

AN10830 - NXP Semiconductors

... serialization/deserialization of the data at very high speeds. Moreover, they have extra features such as Phase Locked Loops (PLL) running at very high frequencies (> 1 GHz) and hard wired 8b/10b coding/decoding. In Xilinx terminology, these highly specialized macros are named GTP or GTX depending o ...

... serialization/deserialization of the data at very high speeds. Moreover, they have extra features such as Phase Locked Loops (PLL) running at very high frequencies (> 1 GHz) and hard wired 8b/10b coding/decoding. In Xilinx terminology, these highly specialized macros are named GTP or GTX depending o ...

NAND Gate is a Universal Gate

... equivalent implementation. Since two successive inverters on the same line will not have an overall effect on the logic as it is shown before. By associating one of the inverters with the output of the first level AND gate and the other with the input of the OR gate, it is clear that this implementa ...

... equivalent implementation. Since two successive inverters on the same line will not have an overall effect on the logic as it is shown before. By associating one of the inverters with the output of the first level AND gate and the other with the input of the OR gate, it is clear that this implementa ...

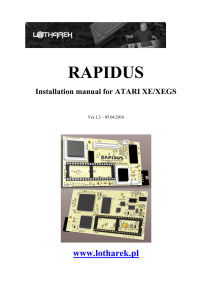

rapidus - Lotharek

... 12 years long project development. Rapidus project was started in 2004 by Michał Pasiecznik (Pasiu/SSG), and first public announcement was made in March of 2006 as F7 accelerator. Since that time, Rapidus project has been improved many times to reach present state. Device info: ...

... 12 years long project development. Rapidus project was started in 2004 by Michał Pasiecznik (Pasiu/SSG), and first public announcement was made in March of 2006 as F7 accelerator. Since that time, Rapidus project has been improved many times to reach present state. Device info: ...

Question Bank

... A) Hard ware description language B) very high speed IC HDL C) highest HDL D) None 12. Which one is not a HDL in the following ...

... A) Hard ware description language B) very high speed IC HDL C) highest HDL D) None 12. Which one is not a HDL in the following ...

CoolRunner-II Automotive CPLD Product Family

... The PLA is different — and better. First, any product term can be attached to any OR gate inside the FB macrocell(s). Second, any logic function can have as many p-terms as needed attached to it within the FB, to an upper limit of 56. Third, product terms can be re-used at multiple macrocell OR func ...

... The PLA is different — and better. First, any product term can be attached to any OR gate inside the FB macrocell(s). Second, any logic function can have as many p-terms as needed attached to it within the FB, to an upper limit of 56. Third, product terms can be re-used at multiple macrocell OR func ...

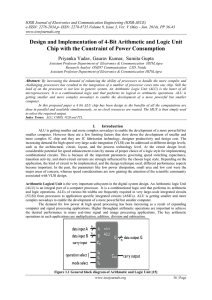

IOSR Journal of Electronics and Communication Engineering (IOSR-JECE)

... challenging processors has resulted in the integration of a number of processor cores into one chip. Still the load of on the processor is not less in generic system. An Arithmetic Logic Unit (ALU) is the heart of all microprocessors. It is a combinational logic unit that performs its logical or ari ...

... challenging processors has resulted in the integration of a number of processor cores into one chip. Still the load of on the processor is not less in generic system. An Arithmetic Logic Unit (ALU) is the heart of all microprocessors. It is a combinational logic unit that performs its logical or ari ...

DS709

... At least one input clock is required; any design has at least a CLK_IN1 or a CLK_IN1_P/CLK_IN1_N port. A secondary input clock is supported for Virtex-6 FPGAs only. 2. Dynamic reconfiguration ports are available for Virtex-6 FPGA MMCM or Spartan-6 FPGA DCM_CLKGEN primitives. 3. Dynamic phase shift p ...

... At least one input clock is required; any design has at least a CLK_IN1 or a CLK_IN1_P/CLK_IN1_N port. A secondary input clock is supported for Virtex-6 FPGAs only. 2. Dynamic reconfiguration ports are available for Virtex-6 FPGA MMCM or Spartan-6 FPGA DCM_CLKGEN primitives. 3. Dynamic phase shift p ...

The AND Operation - KFUPM Faculty List

... The functions are known as Boolean functions while the binary signals are represented by Boolean variables. To be able to design a digital circuit, we must learn how to derive the Boolean function implemented by this circuit. Systems manipulating Binary Logic Signals are commonly referred to a ...

... The functions are known as Boolean functions while the binary signals are represented by Boolean variables. To be able to design a digital circuit, we must learn how to derive the Boolean function implemented by this circuit. Systems manipulating Binary Logic Signals are commonly referred to a ...

Low Power, Noise-Free Divided By 4/5 Counter Using Domino Logic

... reduction on divided-by-4/5 counter. The delay is reduced by domino logic. Dynamic domino logic circuits are widely used in advanced digital Very Large Scale Integration (VLSI) circuits because it is uncomplicated to implement and low cost. Domino logic is a CMOS based approximation of the dynamic l ...

... reduction on divided-by-4/5 counter. The delay is reduced by domino logic. Dynamic domino logic circuits are widely used in advanced digital Very Large Scale Integration (VLSI) circuits because it is uncomplicated to implement and low cost. Domino logic is a CMOS based approximation of the dynamic l ...

Field-programmable gate array

A field-programmable gate array (FPGA) is an integrated circuit designed to be configured by a customer or a designer after manufacturing – hence ""field-programmable"". The FPGA configuration is generally specified using a hardware description language (HDL), similar to that used for an application-specific integrated circuit (ASIC). (Circuit diagrams were previously used to specify the configuration, as they were for ASICs, but this is increasingly rare.)FPGAs contain an array of programmable logic blocks, and a hierarchy of reconfigurable interconnects that allow the blocks to be ""wired together"", like many logic gates that can be inter-wired in different configurations. Logic blocks can be configured to perform complex combinational functions, or merely simple logic gates like AND and XOR. In most FPGAs, logic blocks also include memory elements, which may be simple flip-flops or more complete blocks of memory.