Characteristics of Logic Gates

... Propagation Delay in a Circuit In a given circuit, each gate has a delay The circuit has a propagation delay between inputs and outputs The propagation delay is computed along the critical path To compute the propagation delay, start at the inputs: 1. Delay at each gate output = Maximum inp ...

... Propagation Delay in a Circuit In a given circuit, each gate has a delay The circuit has a propagation delay between inputs and outputs The propagation delay is computed along the critical path To compute the propagation delay, start at the inputs: 1. Delay at each gate output = Maximum inp ...

CPLD Basics

... The symbol window contains many of the basic logic symbols needed for a basic logic design. The short-hand used to describe the symbols should be clear enough. To see what a symbol looks like before using it in a design, single-click on it. To select, click “OK” ...

... The symbol window contains many of the basic logic symbols needed for a basic logic design. The short-hand used to describe the symbols should be clear enough. To see what a symbol looks like before using it in a design, single-click on it. To select, click “OK” ...

Networks on Chip

... Caveat: gaining access to low-level FPGA functions may not be supported by development software. ...

... Caveat: gaining access to low-level FPGA functions may not be supported by development software. ...

Digital Electronics

... Be able to obtain and extract information from the manufacturer datasheets for components commonly used in digital electronics. Know how to identify commonly used electronic components given their part number or schematic symbol. Be able to identify various integrated circuit (IC) package styles. Kn ...

... Be able to obtain and extract information from the manufacturer datasheets for components commonly used in digital electronics. Know how to identify commonly used electronic components given their part number or schematic symbol. Be able to identify various integrated circuit (IC) package styles. Kn ...

3-input NAND gate

... – Justifiable only for dense, fast chips with high sales volume • Standard cell - blocks have been design ahead of time or as part of previous designs – Intermediate cost – Less density and speed compared to full custom • Gate array - regular patterns of gate transistors that can be used in many des ...

... – Justifiable only for dense, fast chips with high sales volume • Standard cell - blocks have been design ahead of time or as part of previous designs – Intermediate cost – Less density and speed compared to full custom • Gate array - regular patterns of gate transistors that can be used in many des ...

Case Studies

... Companies can avoid costly field failures by proactively preventing failures in the factory. Investments in factory controls for comprehensive ESD protection can be based on standards such as ANSI/ESDA S20.20 or IEC 61340-5-1. These broadly accepted standards have been proven to be effective by many ...

... Companies can avoid costly field failures by proactively preventing failures in the factory. Investments in factory controls for comprehensive ESD protection can be based on standards such as ANSI/ESDA S20.20 or IEC 61340-5-1. These broadly accepted standards have been proven to be effective by many ...

Reduce Total System Cost in Portable Applications Using

... In portable applications, the functions listed above are often implemented using ASICs, ASSPs, and other discrete devices. However, all of these functions can be integrated into zero-power CPLDs. The latest zero-power CPLDs offer very high logic capability in ultra-small form-factor packages, making ...

... In portable applications, the functions listed above are often implemented using ASICs, ASSPs, and other discrete devices. However, all of these functions can be integrated into zero-power CPLDs. The latest zero-power CPLDs offer very high logic capability in ultra-small form-factor packages, making ...

Implementation of Digital Pulse Width Modulators using

... applications. This converters has low switching frequency compared with analog controllers. [2] In this method both synchronous and asynchronous blocks are used. Synchronous block is based on counter. In some applications SMPS circuits are used to supply power to the circuits and it has the followin ...

... applications. This converters has low switching frequency compared with analog controllers. [2] In this method both synchronous and asynchronous blocks are used. Synchronous block is based on counter. In some applications SMPS circuits are used to supply power to the circuits and it has the followin ...

Important parameters of the microcontroller

... •Based on modern 32 bit architecture •Cutting edge •Utilizes GNU Compiler to compile code either in C or assembly •Floating point capability allows for more advanced math to be carried out in subroutines •Very Low power requirements when loaded onto 90 nm FPGA •Free! You only need to purchase the FP ...

... •Based on modern 32 bit architecture •Cutting edge •Utilizes GNU Compiler to compile code either in C or assembly •Floating point capability allows for more advanced math to be carried out in subroutines •Very Low power requirements when loaded onto 90 nm FPGA •Free! You only need to purchase the FP ...

ECE 331 – Digital System Design

... Furthermore, voltage ranges, for logic 1 and logic 0, are specified for both the input and the output of a logic gate. They are defined in terms of four parameters ...

... Furthermore, voltage ranges, for logic 1 and logic 0, are specified for both the input and the output of a logic gate. They are defined in terms of four parameters ...

Logic Lab 1 . - Fordham University

... OR gates. The chips listed below are called small-scale-integrated (SSI) devices because the number of gates on one chip is small. The part numbers for TTL SSI chips all begin with either 54 for military-specification parts or 74 for normal parts. (The main difference is in the operating temperature ...

... OR gates. The chips listed below are called small-scale-integrated (SSI) devices because the number of gates on one chip is small. The part numbers for TTL SSI chips all begin with either 54 for military-specification parts or 74 for normal parts. (The main difference is in the operating temperature ...

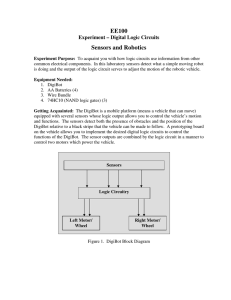

EE100 Sensors and Robotics

... when the wheels turn. First, test the function of the left motor by running a wire from VCC to the enable of the left motor, I. Then, connect a wire from VCC to the direction control of the left motor, J. Record the direction of rotation of the left wheel. Connect J to GND and again record the direc ...

... when the wheels turn. First, test the function of the left motor by running a wire from VCC to the enable of the left motor, I. Then, connect a wire from VCC to the direction control of the left motor, J. Record the direction of rotation of the left wheel. Connect J to GND and again record the direc ...

Field-programmable gate array

A field-programmable gate array (FPGA) is an integrated circuit designed to be configured by a customer or a designer after manufacturing – hence ""field-programmable"". The FPGA configuration is generally specified using a hardware description language (HDL), similar to that used for an application-specific integrated circuit (ASIC). (Circuit diagrams were previously used to specify the configuration, as they were for ASICs, but this is increasingly rare.)FPGAs contain an array of programmable logic blocks, and a hierarchy of reconfigurable interconnects that allow the blocks to be ""wired together"", like many logic gates that can be inter-wired in different configurations. Logic blocks can be configured to perform complex combinational functions, or merely simple logic gates like AND and XOR. In most FPGAs, logic blocks also include memory elements, which may be simple flip-flops or more complete blocks of memory.