COMPARISON BETWEEN TWO MODULATION TECHNIQUES FOR

... The modern FPGA (Field Programmable Gate Array) devices are not only configurable arrays of logic elements, as they were at their invention. They incorporate RAM (Random Access Memory) blocks, hardware multipliers (or even multiply-accumulate units), digital clock managers, making them target platfo ...

... The modern FPGA (Field Programmable Gate Array) devices are not only configurable arrays of logic elements, as they were at their invention. They incorporate RAM (Random Access Memory) blocks, hardware multipliers (or even multiply-accumulate units), digital clock managers, making them target platfo ...

IOSR Journal of Electronics and Communication Engineering (IOSRJECE)

... Data Acquisition system is an embedded system which has wide application in real time monitoring, communication, data transmission ,image data acquisition ,radar, telemetry, remote sensing etc[1]. The main process involved in data acquisition system is to convert analog signal to digital signal that ...

... Data Acquisition system is an embedded system which has wide application in real time monitoring, communication, data transmission ,image data acquisition ,radar, telemetry, remote sensing etc[1]. The main process involved in data acquisition system is to convert analog signal to digital signal that ...

The Design of High Speed FIR Filter using Implementation

... operation is converted to the shifting and adding operation when the DA algorithm is directly applied to realize FIR filter .Aiming at the problems of the best configuration in the coefficient of FIR filter, the storage resource and the calculating speed, the DA algorithm is optimized and improved i ...

... operation is converted to the shifting and adding operation when the DA algorithm is directly applied to realize FIR filter .Aiming at the problems of the best configuration in the coefficient of FIR filter, the storage resource and the calculating speed, the DA algorithm is optimized and improved i ...

Application Note - Peregrine Semiconductor

... 1 mA limit during device ‘turn-on’ and device ‘turn-off’ but any current limitation on the supply source will result in an increase of the device ‘turn on/off’ time. This does not affect the VCTRL logic function. Conclusion This analysis has shown that the complimentary logic can be used successfull ...

... 1 mA limit during device ‘turn-on’ and device ‘turn-off’ but any current limitation on the supply source will result in an increase of the device ‘turn on/off’ time. This does not affect the VCTRL logic function. Conclusion This analysis has shown that the complimentary logic can be used successfull ...

Design_TWG_pres_SF_7

... that -- there's plenty of logic needs, and memory is more efficient when not encumbered by a logic process (and vice-versa). Our ASIC group sees a lot of SRAM, but it's never more than about half the chip, worst-case. All the new design wins we are getting indicates its the tightly integrated, fast ...

... that -- there's plenty of logic needs, and memory is more efficient when not encumbered by a logic process (and vice-versa). Our ASIC group sees a lot of SRAM, but it's never more than about half the chip, worst-case. All the new design wins we are getting indicates its the tightly integrated, fast ...

Design and Implementation of Signal Processing Systems: An

... – High complexity: • Increased transistor count: 10M transistors and higher • Shortened time-to-market delay: 6-12 months ...

... – High complexity: • Increased transistor count: 10M transistors and higher • Shortened time-to-market delay: 6-12 months ...

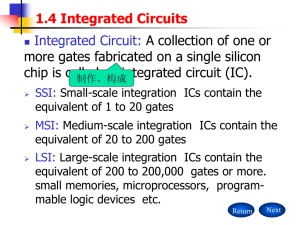

Chapter 3 - Computer Science | SIU

... – Noise Margin – the maximum external noise voltage superimposed on a normal input value that will not cause an undesirable change in the circuit output – Cost for a gate - a measure of the contribution by the gate to the cost of the integrated circuit – Propagation Delay – The time required for a c ...

... – Noise Margin – the maximum external noise voltage superimposed on a normal input value that will not cause an undesirable change in the circuit output – Cost for a gate - a measure of the contribution by the gate to the cost of the integrated circuit – Propagation Delay – The time required for a c ...

Design and Characterization of a QLUT in a Standard CMOS Process

... Abstract— Interconnect has become preponderant in many aspects of circuit design, namely delay, power and area. This effect is particularly true for FPGAs, where interconnect is often the most limiting factor. Quaternary logic offers a means to reduce interconnect since each circuit wire can, in pri ...

... Abstract— Interconnect has become preponderant in many aspects of circuit design, namely delay, power and area. This effect is particularly true for FPGAs, where interconnect is often the most limiting factor. Quaternary logic offers a means to reduce interconnect since each circuit wire can, in pri ...

A “short list” of embedded systems

... Full Custom • Best size, power, performance • Hand design – Horrible time-to-market/flexibility/NRE cost… – Reserve for the most important units in a processor ...

... Full Custom • Best size, power, performance • Hand design – Horrible time-to-market/flexibility/NRE cost… – Reserve for the most important units in a processor ...

What is Body effect ? The threshold voltage of a MOSFET is affected

... have a "clock", the term "perfect clock gating" is used to illustrate how various clock gating techniques are simply approximations of the data-dependent behavior exhibited by asynchronous circuitry, and that as the granularity on which you gate the clock of a synchronous circuit approaches zero, th ...

... have a "clock", the term "perfect clock gating" is used to illustrate how various clock gating techniques are simply approximations of the data-dependent behavior exhibited by asynchronous circuitry, and that as the granularity on which you gate the clock of a synchronous circuit approaches zero, th ...

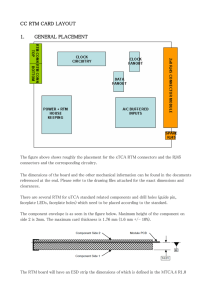

CC RTM CARD LAYOUT GENERAL PLACEMENT The figure above

... In general the ICs in the clocking circuitry should be placed close together. U4,U5,U8 and U11 are the first group and U14,U15,U16 are the second and U3,U10, and U6 are the third group. U12 should be placed close to the RJ45 connector block. The rules concerning the PLL ICs, U16 and U3 are as follow ...

... In general the ICs in the clocking circuitry should be placed close together. U4,U5,U8 and U11 are the first group and U14,U15,U16 are the second and U3,U10, and U6 are the third group. U12 should be placed close to the RJ45 connector block. The rules concerning the PLL ICs, U16 and U3 are as follow ...

ppt - RISE Group

... and is in progress. Piggy back FPGA board for implementing SHAKTI processor is under fabrication. Application program that is intended to work on MC68020 CPU card will be compiled and build with the RISC V toolchain.The same will be flashed in CPU board. Functionality and performance of the SHAKTI C ...

... and is in progress. Piggy back FPGA board for implementing SHAKTI processor is under fabrication. Application program that is intended to work on MC68020 CPU card will be compiled and build with the RISC V toolchain.The same will be flashed in CPU board. Functionality and performance of the SHAKTI C ...

Field-programmable gate array

A field-programmable gate array (FPGA) is an integrated circuit designed to be configured by a customer or a designer after manufacturing – hence ""field-programmable"". The FPGA configuration is generally specified using a hardware description language (HDL), similar to that used for an application-specific integrated circuit (ASIC). (Circuit diagrams were previously used to specify the configuration, as they were for ASICs, but this is increasingly rare.)FPGAs contain an array of programmable logic blocks, and a hierarchy of reconfigurable interconnects that allow the blocks to be ""wired together"", like many logic gates that can be inter-wired in different configurations. Logic blocks can be configured to perform complex combinational functions, or merely simple logic gates like AND and XOR. In most FPGAs, logic blocks also include memory elements, which may be simple flip-flops or more complete blocks of memory.