* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Characteristics of Logic Gates

Index of electronics articles wikipedia , lookup

Field-programmable gate array wikipedia , lookup

Flip-flop (electronics) wikipedia , lookup

Oscilloscope history wikipedia , lookup

Integrating ADC wikipedia , lookup

Surge protector wikipedia , lookup

Power electronics wikipedia , lookup

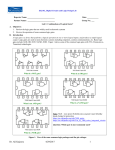

Analog-to-digital converter wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Operational amplifier wikipedia , lookup

Current mirror wikipedia , lookup

Valve RF amplifier wikipedia , lookup

Power MOSFET wikipedia , lookup

Voltage regulator wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Schmitt trigger wikipedia , lookup

Opto-isolator wikipedia , lookup

Transistor–transistor logic wikipedia , lookup

Characteristics of Logic Gates COE 202 Digital Logic Design Dr. Muhamed Mudawar King Fahd University of Petroleum and Minerals Presentation Outline Voltage Levels and Noise Margins Timing Diagrams Gate Delay and Circuit Delay Fan-In and Fan-Out Characteristics of Logic Gates COE 202 – Digital Logic Design © Muhamed Mudawar – slide 2 Voltage Levels Logic 1 is a range of voltage values NOT just a single voltage value Logic 0 is also a range of voltages Not just zero volt The voltage range between logic 0 and 1 is undefined Digital signals are not allowed to use voltage values in the undefined range Characteristics of Logic Gates COE 202 – Digital Logic Design Logic 1 Voltage Range Undefined Voltage Range Logic 0 Voltage Range © Muhamed Mudawar – slide 3 Output Voltage Ranges The output voltage of a logic gate is represented by means of two distinct voltage ranges Output Logic 0 voltage range Vcc Output Logic 1 Voltage Range VOH Undefined Output Voltage Range 0 ≤ V ≤ VOL Output Logic 1 voltage range VOH ≤ V ≤ Vcc VOL Output Logic 0 Voltage Range Undefined output voltage range 0 VOL < V < VOH Characteristics of Logic Gates COE 202 – Digital Logic Design © Muhamed Mudawar – slide 4 Input Voltage Ranges The input voltage of a logic gate is also represented by means of two distinct voltage ranges Input Logic 0 voltage range Vcc Input Logic 1 Voltage Range VIH Undefined Input Voltage Range 0 ≤ V ≤ VIL Input Logic 1 voltage range VIL VIH ≤ V ≤ Vcc Input Logic 0 Voltage Range Undefined input voltage range 0 VIL < V < VIH Characteristics of Logic Gates COE 202 – Digital Logic Design © Muhamed Mudawar – slide 5 Noise Margins Gate 1 output signal noise input signal Gate 2 VIH must be lower than VOH to guard against noise in Input Logic 1 VIL must be higher than VOL to guard against noise in Input Logic 0 Vcc VOH Vcc Output Logic 1 Voltage Range NMH = VOH – VIH 0 Characteristics of Logic Gates VIH Undefined Input Voltage Range Undefined Output Voltage Range VOL Input Logic 1 Voltage Range NML = VIL – VOL Output Logic 0 Voltage Range VIL Input Logic 0 Voltage Range 0 COE 202 – Digital Logic Design © Muhamed Mudawar – slide 6 Timing Diagram Shows the logic values of signals in a circuit versus time Waveform: the shape of a signal over a period of time Example: timing diagram of an AND gate (with zero delay) x y z 0 1 0 1 1 1 1 0 0 0 0 0 1 0 0 1 1 1 0 1 x y z AND gate with zero delay 0 time Characteristics of Logic Gates COE 202 – Digital Logic Design © Muhamed Mudawar – slide 7 Gate Delay A change in the inputs of a gate causes a change in its outputs However, the change in the output signal is not instantaneous There is a small delay between an input signal change and an output signal change, called gate delay x y z 0 1 0 1 1 1 0 1 0 0 1 0 1 1 0 0 0 0 1 z Gate delay = 1 x y 0 time Characteristics of Logic Gates COE 202 – Digital Logic Design © Muhamed Mudawar – slide 8 Propagation Delay in a Circuit In a given circuit, each gate has a delay The circuit has a propagation delay between inputs and outputs The propagation delay is computed along the critical path To compute the propagation delay, start at the inputs: 1. Delay at each gate output = Maximum input delay + Gate delay 2. Propagation delay of a circuit = maximum delay at any output Characteristics of Logic Gates COE 202 – Digital Logic Design © Muhamed Mudawar – slide 9 Computing the Maximum Circuit Delay Consider the following circuit with 8 inputs and 2 outputs Delay of a 2-input AND gate = 2 ns Delay of a 3-input AND gate = 3 ns Delay of a 2-input OR gate = 2 ns Delay of a 3-input OR gate = 3 ns 2 ns 5 ns 𝑓 Compute the 3 ns Maximum 8 ns 𝑔 Circuit Delay 6 ns 3 ns Characteristics of Logic Gates COE 202 – Digital Logic Design © Muhamed Mudawar – slide 10 Rise-Time and Fall-Time In logic simulators, a waveform is drawn as an ideal wave The change from 0 to 1 (or from 1 to 0) is instantaneous In reality, a signal has a non-zero rise-time and fall-time Time taken to change from 10% to 90% of High voltage (and vice versa) Ideal Wave 90% Real Wave 50% 10% Rise Time Characteristics of Logic Gates Fall Time COE 202 – Digital Logic Design Rise Time © Muhamed Mudawar – slide 11 Fan-In The fan-in is the number of inputs to a gate Example: a 3-input AND gate has a Fan-in of 3 Logic gates with a large fan-in tend to be slow Increasing the Fan-in of a gate increases the gate delay For example, a 3-input AND gate has a higher delay than a 2-input AND gate made with the same technology Using logic gates with higher fan-in is useful when reducing the depth (number of levels) of a logic circuit Characteristics of Logic Gates COE 202 – Digital Logic Design © Muhamed Mudawar – slide 12 Fan-Out In digital circuits, it is common for the output of one gate (called driver gate) to be connect to the inputs of several load gates The fan-out of a gate is the number of gate inputs it can feed There is a limit on the maximum fan-out of a gate Driver Gate a limited amount of current. 1 Each input of a load gate consumes a certain amount of current. 2 Therefore, the driver gate can only Fan-Out= 2 Load Gates The output of a driver gate can supply feed a limited number of load gates. Characteristics of Logic Gates COE 202 – Digital Logic Design © Muhamed Mudawar – slide 13 Increasing the Fan-Out with a Buffer Gate Buffer Gate Buffer Gate Output 𝑓 = Input 𝑥 𝑥 𝑓=𝑥 Buffer provides drive capability Buffer Gate High current output 2 Increases the Fan-Out Buffer gate increases the propagation delay of a circuit Characteristics of Logic Gates Fan-Out = N COE 202 – Digital Logic Design Load Gates 1 Used to amplify an input signal N © Muhamed Mudawar – slide 14