RH118

... Note 1: The inputs are shunted with back-to-back Zeners for overvoltage protection. Excessive current will flow if a differential voltage greater than 5V is applied to the inputs. Note 2: For supply voltages less than ±15V, the maximum input voltage is equal to the supply voltage. Note 3: These spec ...

... Note 1: The inputs are shunted with back-to-back Zeners for overvoltage protection. Excessive current will flow if a differential voltage greater than 5V is applied to the inputs. Note 2: For supply voltages less than ±15V, the maximum input voltage is equal to the supply voltage. Note 3: These spec ...

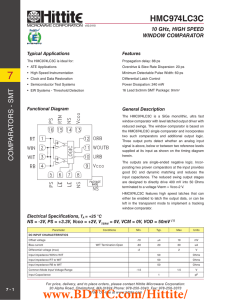

HMC974LC3C 数据资料DataSheet下载

... The HMC974LC3C is a SiGe monolithic, ultra fast window comparator with level latched output driver with reduced swings. The window comparator is based on the HMC674LC3C single comparator and incorporates two such comparators and additional output logic. Three output ports detect whether an analog in ...

... The HMC974LC3C is a SiGe monolithic, ultra fast window comparator with level latched output driver with reduced swings. The window comparator is based on the HMC674LC3C single comparator and incorporates two such comparators and additional output logic. Three output ports detect whether an analog in ...

A Self-Clocked ASIC Interface for MEMS Gyroscope with 1m°/s√Hz

... modulator, and performs the final output demodulation. The demodulation output is decimated using a programmable decimation filter. Two BPF’s centered at the gyro resonance frequency with 200Hz BW, filter out noise of both the drive and sense output signals, before multiplying them for demodulation. ...

... modulator, and performs the final output demodulation. The demodulation output is decimated using a programmable decimation filter. Two BPF’s centered at the gyro resonance frequency with 200Hz BW, filter out noise of both the drive and sense output signals, before multiplying them for demodulation. ...

How to get the best ADC accuracy in STM32 microcontrollers

... The differential linearity error (DLE) is the maximum deviation between the actual and ideal steps. Here ‘ideal’ does not refer to the ideal transfer curve but to the ADC resolution. The DLE is denoted by ED. It is represented in Figure 11. ED = Actual step width – 1 LSB Ideally, an analog input vol ...

... The differential linearity error (DLE) is the maximum deviation between the actual and ideal steps. Here ‘ideal’ does not refer to the ideal transfer curve but to the ADC resolution. The DLE is denoted by ED. It is represented in Figure 11. ED = Actual step width – 1 LSB Ideally, an analog input vol ...

Analog to Digital Conversion

... and how much of the muscle is covered by fatty tissue. Each of these issues will effect how we will have to go about designing the end system. For example, the contraction speed of a muscle group will undoubtedly have an effect on the coding aspect of our project. There are some segments of our desi ...

... and how much of the muscle is covered by fatty tissue. Each of these issues will effect how we will have to go about designing the end system. For example, the contraction speed of a muscle group will undoubtedly have an effect on the coding aspect of our project. There are some segments of our desi ...

AD7400A 数据手册DataSheet下载

... The AD7400A 1 is a second-order, Σ-Δ modulator that converts an analog input signal into a high speed, 1-bit data stream with on-chip digital isolation based on Analog Devices, Inc., iCoupler® technology. The AD7400A operates from a 5 V power supply and accepts a differential input signal of ±250 mV ...

... The AD7400A 1 is a second-order, Σ-Δ modulator that converts an analog input signal into a high speed, 1-bit data stream with on-chip digital isolation based on Analog Devices, Inc., iCoupler® technology. The AD7400A operates from a 5 V power supply and accepts a differential input signal of ±250 mV ...

UCC3895 CD Output Asymmetric Duty Cycle

... and conditions of sale supplied at the time of order acknowledgment. TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary ...

... and conditions of sale supplied at the time of order acknowledgment. TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary ...

A Low Cost High Precision Temperature Pressure Humidity

... The main requirement for the temperature sensor was high precision for a low cost (taking into consideration we are going to use ~ 1000 or more of such units for the final ICAL). Some of the probable sensors for this purpose were DS1825, AD592 and F2020-100-1/3B. Each had its advantage and disadvant ...

... The main requirement for the temperature sensor was high precision for a low cost (taking into consideration we are going to use ~ 1000 or more of such units for the final ICAL). Some of the probable sensors for this purpose were DS1825, AD592 and F2020-100-1/3B. Each had its advantage and disadvant ...

MAX110/MAX111 Low-Cost, 2-Channel, ±14-Bit Serial ADCs General Description ____________________________Features

... sigma-delta loop (Figure 1). The differential input voltage is internally connected to a precision voltage-tocurrent converter. The resulting current is integrated and applied to a comparator. The comparator output then drives an up/down counter and a 1-bit DAC. When the DAC output is fed back to th ...

... sigma-delta loop (Figure 1). The differential input voltage is internally connected to a precision voltage-tocurrent converter. The resulting current is integrated and applied to a comparator. The comparator output then drives an up/down counter and a 1-bit DAC. When the DAC output is fed back to th ...

TLV1571 数据资料 dataSheet 下载

... All sampling, conversion, and data output in the device are started by a trigger. This could be the RD, WR, or CSTART signal depending on the mode of conversion and configuration. The rising edge of RD, WR, and CSTART signal are extremely important, since they are used to start the conversion. These ...

... All sampling, conversion, and data output in the device are started by a trigger. This could be the RD, WR, or CSTART signal depending on the mode of conversion and configuration. The rising edge of RD, WR, and CSTART signal are extremely important, since they are used to start the conversion. These ...

ACCEPT $10 ACCEPT $20

... -INHIBIT LINE terminals will allow the Bill Acceptor to accept banknotes, but the voltage within +1 and -24 VDC will fully prohibit the Bill Acceptor to accept banknotes. The OUTPUT PULSE and INHIBIT LINE signals are located on the 6 pin connector (power and isolated pulse interface) of the Bill Acc ...

... -INHIBIT LINE terminals will allow the Bill Acceptor to accept banknotes, but the voltage within +1 and -24 VDC will fully prohibit the Bill Acceptor to accept banknotes. The OUTPUT PULSE and INHIBIT LINE signals are located on the 6 pin connector (power and isolated pulse interface) of the Bill Acc ...

Analog-to-digital converter

An analog-to-digital converter (ADC, A/D, or A to D) is a device that converts a continuous physical quantity (usually voltage) to a digital number that represents the quantity's amplitude.The conversion involves quantization of the input, so it necessarily introduces a small amount of error. Furthermore, instead of continuously performing the conversion, an ADC does the conversion periodically, sampling the input. The result is a sequence of digital values that have been converted from a continuous-time and continuous-amplitude analog signal to a discrete-time and discrete-amplitude digital signal.An ADC is defined by its bandwidth (the range of frequencies it can measure) and its signal to noise ratio (how accurately it can measure a signal relative to the noise it introduces). The actual bandwidth of an ADC is characterized primarily by its sampling rate, and to a lesser extent by how it handles errors such as aliasing. The dynamic range of an ADC is influenced by many factors, including the resolution (the number of output levels it can quantize a signal to), linearity and accuracy (how well the quantization levels match the true analog signal) and jitter (small timing errors that introduce additional noise). The dynamic range of an ADC is often summarized in terms of its effective number of bits (ENOB), the number of bits of each measure it returns that are on average not noise. An ideal ADC has an ENOB equal to its resolution. ADCs are chosen to match the bandwidth and required signal to noise ratio of the signal to be quantized. If an ADC operates at a sampling rate greater than twice the bandwidth of the signal, then perfect reconstruction is possible given an ideal ADC and neglecting quantization error. The presence of quantization error limits the dynamic range of even an ideal ADC, however, if the dynamic range of the ADC exceeds that of the input signal, its effects may be neglected resulting in an essentially perfect digital representation of the input signal.An ADC may also provide an isolated measurement such as an electronic device that converts an input analog voltage or current to a digital number proportional to the magnitude of the voltage or current. However, some non-electronic or only partially electronic devices, such as rotary encoders, can also be considered ADCs. The digital output may use different coding schemes. Typically the digital output will be a two's complement binary number that is proportional to the input, but there are other possibilities. An encoder, for example, might output a Gray code.The inverse operation is performed by a digital-to-analog converter (DAC).