Sequential Circuit Design

... – Synthesis based, automated by EDA tools, RTL compilers, inserted into clock-tree – Clock enable signals manually defined by designer, inserted into clock-tree, FFs’ clock input – Data-Driven clock gating, inserted at FF-level ...

... – Synthesis based, automated by EDA tools, RTL compilers, inserted into clock-tree – Clock enable signals manually defined by designer, inserted into clock-tree, FFs’ clock input – Data-Driven clock gating, inserted at FF-level ...

IA-C

... Whenever the interrupt occurs, the computer suspends current activity, and executes an “interrupt service routine”. The interrupt service routine in this case might be a short program which acquires one frame of data, and stores it in memory. The computer can perform other operations in the foregrou ...

... Whenever the interrupt occurs, the computer suspends current activity, and executes an “interrupt service routine”. The interrupt service routine in this case might be a short program which acquires one frame of data, and stores it in memory. The computer can perform other operations in the foregrou ...

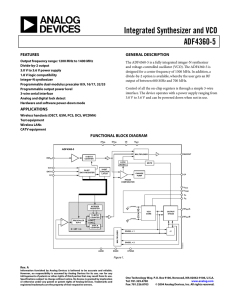

ADF4360-5 VCO-PLL - University of Toronto Physics

... VCO Output. The output level is programmable from −4.5 dBm to −13.5 dBm. See the Output Matching section for a description of the various output stages. VCO Complementary Output. The output level is programmable from −4.5 dBm to −13.5 dBm. See the Output Matching section for a description of the var ...

... VCO Output. The output level is programmable from −4.5 dBm to −13.5 dBm. See the Output Matching section for a description of the various output stages. VCO Complementary Output. The output level is programmable from −4.5 dBm to −13.5 dBm. See the Output Matching section for a description of the var ...

Clippers And Clampers

... and a capacitor. To keep a constant voltage on the capacitor over the period of the input, the RC time constant must be large. A design rule of thumb is to make the RC time constant at least five times the half-period of the input signal, which results in approximately an 18% error over a half-perio ...

... and a capacitor. To keep a constant voltage on the capacitor over the period of the input, the RC time constant must be large. A design rule of thumb is to make the RC time constant at least five times the half-period of the input signal, which results in approximately an 18% error over a half-perio ...

KA3842/3843

... specifically designed for Off-Line and DC-to-DC converter applications offering the designer a cost effective solution with minimal external components. These integrated circuits feature a trimmed oscillator for ...

... specifically designed for Off-Line and DC-to-DC converter applications offering the designer a cost effective solution with minimal external components. These integrated circuits feature a trimmed oscillator for ...

ADS823, ADS826: 10-Bit, 60MHz Sampling Analog-To

... range is set to 2Vp-p. In this configuration, the top and bottom references (REFT, REFB) provide an output voltage of +3.5V and +1.5V, respectively. Two resistors ( 2x 1.62kΩ) are used to create a common-mode voltage (VCM) of approximately +2.5V to bias the inputs of the driving amplifier A1. Using ...

... range is set to 2Vp-p. In this configuration, the top and bottom references (REFT, REFB) provide an output voltage of +3.5V and +1.5V, respectively. Two resistors ( 2x 1.62kΩ) are used to create a common-mode voltage (VCM) of approximately +2.5V to bias the inputs of the driving amplifier A1. Using ...

An Ultra-Low-Voltage Ultra-Low-Power OTA With Improved Gain

... compensation technique is the inconvenience of the right halfplane (RHP) zero. This RHP zero degrades the phase margin and leads to instability of operational amplifiers. Two different approaches of controlling the RHP zero are shown in Fig. 1 [10]. As observed in Fig. 1 (a), the nulling resistor co ...

... compensation technique is the inconvenience of the right halfplane (RHP) zero. This RHP zero degrades the phase margin and leads to instability of operational amplifiers. Two different approaches of controlling the RHP zero are shown in Fig. 1 [10]. As observed in Fig. 1 (a), the nulling resistor co ...

ADE7757A 数据手册DataSheet 下载

... to AGND with a 1 μF tantalum capacitor and a 100 nF ceramic capacitor. The internal reference cannot be used to drive an external load. Select Calibration Frequency. This logic input selects the frequency on the Calibration Output CF. Table 7 shows calibration frequency selections. Conversion Freque ...

... to AGND with a 1 μF tantalum capacitor and a 100 nF ceramic capacitor. The internal reference cannot be used to drive an external load. Select Calibration Frequency. This logic input selects the frequency on the Calibration Output CF. Table 7 shows calibration frequency selections. Conversion Freque ...

Lecture1

... The maximum Fan-out possible is the smallest value. The maximum Fan-out possible is an Integer number. If the Maximum Fan-out is not integer, should be use Integer number less than the actual value. ...

... The maximum Fan-out possible is the smallest value. The maximum Fan-out possible is an Integer number. If the Maximum Fan-out is not integer, should be use Integer number less than the actual value. ...

Document

... • We can look at a sound in terms of its pressure variations as a function of time OR • We can look at a sound in terms of its frequency spectrum This is equivalent to saying each segment is equivalent to a sum of sine waves. “Fourier decomposition” Some of the character or “timbre” of different sou ...

... • We can look at a sound in terms of its pressure variations as a function of time OR • We can look at a sound in terms of its frequency spectrum This is equivalent to saying each segment is equivalent to a sum of sine waves. “Fourier decomposition” Some of the character or “timbre” of different sou ...

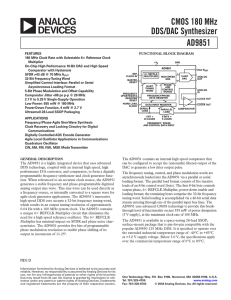

CMOS 180 MHz DDS/DAC Synthesizer AD9851

... APPLICATIONS Frequency/Phase-Agile Sine Wave Synthesis Clock Recovery and Locking Circuitry for Digital Communications Digitally Controlled ADC Encode Generator Agile Local Oscillator Applications in Communications Quadrature Oscillator CW, AM, FM, FSK, MSK Mode Transmitter GENERAL DESCRIPTION ...

... APPLICATIONS Frequency/Phase-Agile Sine Wave Synthesis Clock Recovery and Locking Circuitry for Digital Communications Digitally Controlled ADC Encode Generator Agile Local Oscillator Applications in Communications Quadrature Oscillator CW, AM, FM, FSK, MSK Mode Transmitter GENERAL DESCRIPTION ...

Fast Frequency Acquisition Phase-Frequency Detectors for GSa/s

... for three PFDs, starting the VCO at 375 MHz and locking at 800 MHz.The PLL [1] and PFD test circuits are fabricated in a 0.25-µm CMOS technology. The first and second circuits shows a 18.5% and 41.7% improvements in maximum locking frequency compared to NAND DFF PFD respectively. The measurement res ...

... for three PFDs, starting the VCO at 375 MHz and locking at 800 MHz.The PLL [1] and PFD test circuits are fabricated in a 0.25-µm CMOS technology. The first and second circuits shows a 18.5% and 41.7% improvements in maximum locking frequency compared to NAND DFF PFD respectively. The measurement res ...

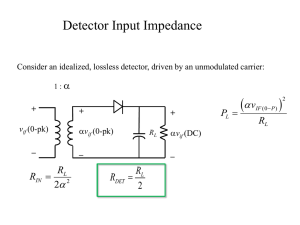

+ v if

... The previous example uses reasonable numbers, and the result, 15.7 dB, is not a respectable value for dynamic range. If the radio’s maximum range is 50 miles, then the IF will clip at ranges less than 1.5 miles, and this would be unacceptable. The solution is to provide a means for reducing the gain ...

... The previous example uses reasonable numbers, and the result, 15.7 dB, is not a respectable value for dynamic range. If the radio’s maximum range is 50 miles, then the IF will clip at ranges less than 1.5 miles, and this would be unacceptable. The solution is to provide a means for reducing the gain ...

ADE7768 数据手册DataSheet 下载

... Power Supply. This pin provides the supply voltage for the circuitry in the ADE7768. The supply voltage should be maintained at 5 V ± 5% for specified operation. This pin should be decoupled with a 10 μF capacitor in parallel with a 100 nF ceramic capacitor. Analog Inputs for Channel V2 (Voltage Cha ...

... Power Supply. This pin provides the supply voltage for the circuitry in the ADE7768. The supply voltage should be maintained at 5 V ± 5% for specified operation. This pin should be decoupled with a 10 μF capacitor in parallel with a 100 nF ceramic capacitor. Analog Inputs for Channel V2 (Voltage Cha ...

ADV7128 数据手册DataSheet 下载

... cable lengths. Cable lengths greater than 10 meters can attenuate and distort high frequency analog output pulses. The inclusion of output buffers will compensate for some cable distortion. Buffers with large full power bandwidths and gains between 2 and 4 will be required. These buffers will also n ...

... cable lengths. Cable lengths greater than 10 meters can attenuate and distort high frequency analog output pulses. The inclusion of output buffers will compensate for some cable distortion. Buffers with large full power bandwidths and gains between 2 and 4 will be required. These buffers will also n ...

Audio Frequency Amplifier Andradige Silva ENEE417 Introduction

... The simulations done with the speaker model better correlated with the actual data. As seen in figure 12 the amplifier worked with constant gain up to 50 kHz, which was sufficient for our project. The final circuit is installed inside an aluminum box along with the FM, PWM and optical receiver circu ...

... The simulations done with the speaker model better correlated with the actual data. As seen in figure 12 the amplifier worked with constant gain up to 50 kHz, which was sufficient for our project. The final circuit is installed inside an aluminum box along with the FM, PWM and optical receiver circu ...

3.reactance_and_impedance

... Explain the relationship between AC voltage and AC current in a resistor, capacitor and inductor. Explain why a capacitor causes a phase shift between current and voltage (ICE). Define capacitive reactance. Explain the relationship between capacitive reactance and frequency. Explain why an i ...

... Explain the relationship between AC voltage and AC current in a resistor, capacitor and inductor. Explain why a capacitor causes a phase shift between current and voltage (ICE). Define capacitive reactance. Explain the relationship between capacitive reactance and frequency. Explain why an i ...