AK1543 - Asahi Kasei Microdevices

... 1300MHz Delta-Sigma Fractional-N Frequency Synthesizer 1. Overview The AK1543 is a Delta-Sigma Fractional-N PLL (Phase Locked Loop) frequency synthesizer with a frequency switching function, covering a wide range of frequencies from 400 to 1300MHz. This product consists of an 18-bit Delta-Sigma modu ...

... 1300MHz Delta-Sigma Fractional-N Frequency Synthesizer 1. Overview The AK1543 is a Delta-Sigma Fractional-N PLL (Phase Locked Loop) frequency synthesizer with a frequency switching function, covering a wide range of frequencies from 400 to 1300MHz. This product consists of an 18-bit Delta-Sigma modu ...

analog multiplier

... The most significant advance in the ADL5391 is the use of a new multiplier core architecture, which differs markedly from the conventional form that has been in use since 1970. The conventional structure that employs a current mode, translinear core is fundamentally asymmetric with respect to the X ...

... The most significant advance in the ADL5391 is the use of a new multiplier core architecture, which differs markedly from the conventional form that has been in use since 1970. The conventional structure that employs a current mode, translinear core is fundamentally asymmetric with respect to the X ...

DATA SHEET For a complete data sheet, please also download:

... techniques where the DEMOUT voltage is one threshold voltage lower than the VCO input voltage, here the DEMOUT voltage equals that of the VCO input. If DEMOUT is used, a load resistor (RS) should be connected from DEMOUT to GND; if unused, DEMOUT should be left open. The VCO output (VCOOUT) can be c ...

... techniques where the DEMOUT voltage is one threshold voltage lower than the VCO input voltage, here the DEMOUT voltage equals that of the VCO input. If DEMOUT is used, a load resistor (RS) should be connected from DEMOUT to GND; if unused, DEMOUT should be left open. The VCO output (VCOOUT) can be c ...

ADF4360-3 数据手册DataSheet 下载

... Chip Enable. A logic low on this pin powers down the device and puts the charge pump into three-state mode. Taking the pin high powers up the device depending on the status of the power-down bits. Charge Pump Output. When enabled, this provides ± ICP to the external loop filter, which in turn drives ...

... Chip Enable. A logic low on this pin powers down the device and puts the charge pump into three-state mode. Taking the pin high powers up the device depending on the status of the power-down bits. Charge Pump Output. When enabled, this provides ± ICP to the external loop filter, which in turn drives ...

HMC725LC3C

... The HMC725LC3C is a XOR/XNOR gate function designed to support data transmission rates of up to 13 Gbps, and clock frequencies as high as 13 GHz. All input signals to the HMC725LC3C are terminated with 50 Ohms to ground on-chip, and maybe either AC or DC coupled. The differential outputs of the HMC7 ...

... The HMC725LC3C is a XOR/XNOR gate function designed to support data transmission rates of up to 13 Gbps, and clock frequencies as high as 13 GHz. All input signals to the HMC725LC3C are terminated with 50 Ohms to ground on-chip, and maybe either AC or DC coupled. The differential outputs of the HMC7 ...

Kondratenko_S.V.2

... 1. In the early stages of designing high-speed transceiver in serial channels it is advisable to take into account the effect of parasitic constructive elements in order to choose among alternative realizations of analog parts of the transmitter and receiver. 2. To evaluate the noise immunity of the ...

... 1. In the early stages of designing high-speed transceiver in serial channels it is advisable to take into account the effect of parasitic constructive elements in order to choose among alternative realizations of analog parts of the transmitter and receiver. 2. To evaluate the noise immunity of the ...

AD8023

... Pulling the voltage on any one of the Disable pins about 1.6 V up from the negative supply will put the corresponding amplifier into a disabled, powered down, state. In this condition, the amplifier’s quiescent current drops to about 1.3 mA, its output becomes a high impedance, and there is a high l ...

... Pulling the voltage on any one of the Disable pins about 1.6 V up from the negative supply will put the corresponding amplifier into a disabled, powered down, state. In this condition, the amplifier’s quiescent current drops to about 1.3 mA, its output becomes a high impedance, and there is a high l ...

... 31. The electric potential due to an electric dipole of length L at point distance r away from it will be doubled if the .a. )Length L of the dipole is doubled .b. ) r is doubled .c. ) r is halved d ) L is halved 32. When a particular mode is excited in a waveguide there appears an extra electric co ...

Experiment SIG1: Active Low-Pass Filter Design

... the GPR-3030. If you’re using the M10-380D-303-A power supply: i) make sure that you use only one part of the power supply i.e. either master or slave, and ii) select the “indep” button 2) Connect all the wires accordingly as per instructed, directly between the supply and the experiment board. 3) D ...

... the GPR-3030. If you’re using the M10-380D-303-A power supply: i) make sure that you use only one part of the power supply i.e. either master or slave, and ii) select the “indep” button 2) Connect all the wires accordingly as per instructed, directly between the supply and the experiment board. 3) D ...

Analog Devices Welcomes Hittite Microwave Corporation

... 4. PAD BURR LENGTH SHALL BE 0.15mm MAXIMUM. PAD BURR HEIGHT SHALL BE 0.05mm MAXIMUM. 5. PACKAGE WARP SHALL NOT EXCEED 0.05mm. ...

... 4. PAD BURR LENGTH SHALL BE 0.15mm MAXIMUM. PAD BURR HEIGHT SHALL BE 0.05mm MAXIMUM. 5. PACKAGE WARP SHALL NOT EXCEED 0.05mm. ...

RIAA Preamps Part 1

... but this approach was seldom if ever taken. So here is the dilemma: we do not want to exceed two gain stages and yet we want more gain. One solution has been to use at least one cascode stage in the mix. The cascode circuit has the very desirable attribute of realizing a gain in excess of the mu of ...

... but this approach was seldom if ever taken. So here is the dilemma: we do not want to exceed two gain stages and yet we want more gain. One solution has been to use at least one cascode stage in the mix. The cascode circuit has the very desirable attribute of realizing a gain in excess of the mu of ...

AN-873 APPLICATION NOTE

... In such a case, the accuracy of digital lock detect is compromised. In an unlocked state, if the unlocked frequency is close to the desired frequency, the phase error at the PFD drifts in and out of the 15 ns window, causing the DLD signal to pulse high and low. More seriously, sometimes if a voltag ...

... In such a case, the accuracy of digital lock detect is compromised. In an unlocked state, if the unlocked frequency is close to the desired frequency, the phase error at the PFD drifts in and out of the 15 ns window, causing the DLD signal to pulse high and low. More seriously, sometimes if a voltag ...

BUF634 250mA HIGH

... The –3dB bandwidth of the BUF634 is approximately 30MHz in the low quiescent current mode (1.5mA typical). To select this mode, leave the bandwidth control pin open (no connection). Bandwidth can be extended to approximately 180MHz by connecting the bandwidth control pin to V–. This increases ...

... The –3dB bandwidth of the BUF634 is approximately 30MHz in the low quiescent current mode (1.5mA typical). To select this mode, leave the bandwidth control pin open (no connection). Bandwidth can be extended to approximately 180MHz by connecting the bandwidth control pin to V–. This increases ...

LTC6905 - 17MHz to 170MHz Resistor Set SOT-23 Oscillator.

... using the minimum high level output voltage in the Electrical Characteristics. With a V+ equal to 5.5V and 4mA output current, the minimum high level output voltage is 5V and the lowest resistive load Pin 5 can drive is 1.25k (5V/4mA). With a V+ equal to 2.7V and 4mA output current, the minimum high ...

... using the minimum high level output voltage in the Electrical Characteristics. With a V+ equal to 5.5V and 4mA output current, the minimum high level output voltage is 5V and the lowest resistive load Pin 5 can drive is 1.25k (5V/4mA). With a V+ equal to 2.7V and 4mA output current, the minimum high ...

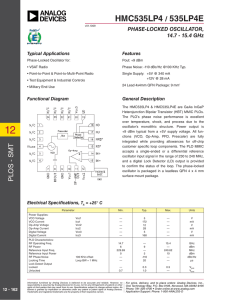

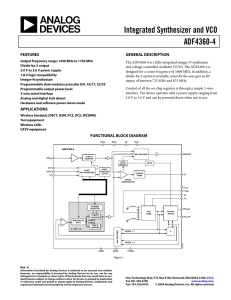

ADF4360-4 Integrated Synthesizer and VCO Data

... VCO Output. The output level is programmable from −4 dBm to −13 dBm. See the Output Matching section for a description of the various output stages. VCO Complementary Output. The output level is programmable from −4 dBm to −13 dBm. See the Output Matching section for a description of the various out ...

... VCO Output. The output level is programmable from −4 dBm to −13 dBm. See the Output Matching section for a description of the various output stages. VCO Complementary Output. The output level is programmable from −4 dBm to −13 dBm. See the Output Matching section for a description of the various out ...

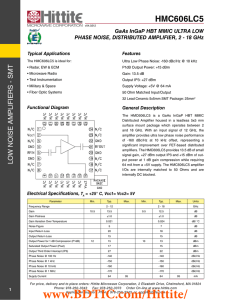

HMC606LC5 数据资料DataSheet下载

... Distributed Amplifier housed in a leadless 5x5 mm surface mount package which operates between 2 and 18 GHz. With an input signal of 12 GHz, the amplifier provides ultra low phase noise performance of -160 dBc/Hz at 10 kHz offset, representing a significant improvement over FET-based distributed amp ...

... Distributed Amplifier housed in a leadless 5x5 mm surface mount package which operates between 2 and 18 GHz. With an input signal of 12 GHz, the amplifier provides ultra low phase noise performance of -160 dBc/Hz at 10 kHz offset, representing a significant improvement over FET-based distributed amp ...

XA Artix-7 FPGAs Overview

... the CMT, which can completely eliminate the basic clock distribution delay. ...

... the CMT, which can completely eliminate the basic clock distribution delay. ...