Simulation: Offset Voltage and Offset Current

... The op-amp models in the LTspice library have their offset voltages and offset currents set to zero. Their bias currents are usually set to their typical databook value. One can refer to a particular op-amp’s datasheet to determine the range of its input offset current and input offset voltage. The ...

... The op-amp models in the LTspice library have their offset voltages and offset currents set to zero. Their bias currents are usually set to their typical databook value. One can refer to a particular op-amp’s datasheet to determine the range of its input offset current and input offset voltage. The ...

IDT2309 - Integrated Device Technology

... All outputs should be uniformly loaded in order to achieve Zero I/O Delay. Since the CLKOUT pin is the internal feedback for the PLL, its relative loading can affect and adjust the input/output delay. The Output Load Difference diagram illustrates the PLL's relative loading with respect to the other ...

... All outputs should be uniformly loaded in order to achieve Zero I/O Delay. Since the CLKOUT pin is the internal feedback for the PLL, its relative loading can affect and adjust the input/output delay. The Output Load Difference diagram illustrates the PLL's relative loading with respect to the other ...

lecture10aa

... 1. Some circuits are driven by a single-frequency sinusoidal source. Example: The electric power system at frequency of 60+/-0.1 Hz in U. S. Voltage is a sinusoidal function of time because it is produced by huge rotating generators powered by mechanical energy source such as steam (produced by heat ...

... 1. Some circuits are driven by a single-frequency sinusoidal source. Example: The electric power system at frequency of 60+/-0.1 Hz in U. S. Voltage is a sinusoidal function of time because it is produced by huge rotating generators powered by mechanical energy source such as steam (produced by heat ...

ece2201_lab4

... VOLTAGE CONTROLLED OSCILLATOR (VCO) L23. An important functional block in communication circuits is the voltage controlled oscillator, or VCO. This block is an oscillator for which the output frequency is controlled by a voltage. One simple type of VCO is the ring oscillator, shown in Fig. 3.8. The ...

... VOLTAGE CONTROLLED OSCILLATOR (VCO) L23. An important functional block in communication circuits is the voltage controlled oscillator, or VCO. This block is an oscillator for which the output frequency is controlled by a voltage. One simple type of VCO is the ring oscillator, shown in Fig. 3.8. The ...

ppt

... Many op amps are internally compensated. Internal frequency compensation capacitor prevents the op amp from oscillating by decreasing the op amp's gain as frequency increases. Otherwise there would be sufficient gain and phase shift at some high frequency where enough output signal could be fed back ...

... Many op amps are internally compensated. Internal frequency compensation capacitor prevents the op amp from oscillating by decreasing the op amp's gain as frequency increases. Otherwise there would be sufficient gain and phase shift at some high frequency where enough output signal could be fed back ...

J. Phinney and D.J. Perreault, “Filters with Active Tuning for Power Applications,” IEEE Transactions on Power Electronics , Vol. 18, No. 2, March 2003, pp. 636-647.

... To take advantage of high-Q resonant filters, one must ensure that the converter switching frequency remains aligned with the filter resonance across all component tolerances and operating conditions. Resonant excitation is equivalent to maintaining a resistive phase relationship (0 ) between resona ...

... To take advantage of high-Q resonant filters, one must ensure that the converter switching frequency remains aligned with the filter resonance across all component tolerances and operating conditions. Resonant excitation is equivalent to maintaining a resistive phase relationship (0 ) between resona ...

Lab3Questions

... output voltages will decrease, and vice versa. Vp must be appropriately within bound of the positive supply rail. o Provide a detailed discussion illustrating that you understand what is going on. We have a 5V input at VCC which is voltage divided to 2.5 V at the positive input terminal, Vp. This ...

... output voltages will decrease, and vice versa. Vp must be appropriately within bound of the positive supply rail. o Provide a detailed discussion illustrating that you understand what is going on. We have a 5V input at VCC which is voltage divided to 2.5 V at the positive input terminal, Vp. This ...

unit4sup - University of Kentucky College of Engineering

... signal and noise from the same source as the examples. Note that you do not know the SNR for this case. Since you know the PSD shapes you can try to assess the SNR by examining the PSDs or ACs of combined signal. Also assume that the SNR is between 25 and 0 dB and create a loop to increment through ...

... signal and noise from the same source as the examples. Note that you do not know the SNR for this case. Since you know the PSD shapes you can try to assess the SNR by examining the PSDs or ACs of combined signal. Also assume that the SNR is between 25 and 0 dB and create a loop to increment through ...

Working Paper on Digitizing Audio for the Nation

... are delineated below. The choice of appropriate digitization standards seems to be influenced by two distinct factors - the technological and the archival. Each of these factors poses a different set of questions and challenges to the project. When deciding on particular specifications of sampling r ...

... are delineated below. The choice of appropriate digitization standards seems to be influenced by two distinct factors - the technological and the archival. Each of these factors poses a different set of questions and challenges to the project. When deciding on particular specifications of sampling r ...

D-TEK Vehicle Loop Detector Instructions

... unless opening is protected by a secondary safety device such as the IRB-4X. 9. Fail Safe / Fail Secure- this feature is controlled by DIP switch 4 on the back of the detector. Normal factory setting is “Fail Safe” which allows the detector to hold the gate open in the event of a failure or loss of ...

... unless opening is protected by a secondary safety device such as the IRB-4X. 9. Fail Safe / Fail Secure- this feature is controlled by DIP switch 4 on the back of the detector. Normal factory setting is “Fail Safe” which allows the detector to hold the gate open in the event of a failure or loss of ...

Moving coil meters for DC measurements

... calculate resolution is 2^n. For example, a 12 bit ADC has a resolution of 2^12 = 4,096. Therefore, our best resolution is 1 part out of 4,096, or 0.0244% of the full scale. An ADC takes an analog signal and turns it into a binary number. Thus, each binary number from the ADC represents a certain vo ...

... calculate resolution is 2^n. For example, a 12 bit ADC has a resolution of 2^12 = 4,096. Therefore, our best resolution is 1 part out of 4,096, or 0.0244% of the full scale. An ADC takes an analog signal and turns it into a binary number. Thus, each binary number from the ADC represents a certain vo ...

Analog Component Development for 300°C Sensor Interface

... CrSiN resistors 2.5K ohms per square Delta-R, 25°C to 300°C -4% ...

... CrSiN resistors 2.5K ohms per square Delta-R, 25°C to 300°C -4% ...

Interface modules for SQlab III (Code 3511

... 2-channel input module for direct signals and ICP® sensors Input Input signal: analog signals or ICP® sensors Signal ranges: - 30 dB (31.6 mVrms) to +31 dB (100 Vpp) in 17 ranges Coupling: DC, AC or ICP® ICP® current: 4 mA constant current supply Input impedance: 1 MOhm Sampling frequency (fS ): 300 ...

... 2-channel input module for direct signals and ICP® sensors Input Input signal: analog signals or ICP® sensors Signal ranges: - 30 dB (31.6 mVrms) to +31 dB (100 Vpp) in 17 ranges Coupling: DC, AC or ICP® ICP® current: 4 mA constant current supply Input impedance: 1 MOhm Sampling frequency (fS ): 300 ...

DS1181L 20MHz to 134MHz Spread-Spectrum Clock Modulator for LCD Panels General Description

... The DS1181L is a spread-spectrum clock modulator IC that reduces EMI in high clock-frequency-based, digital electronic equipment. Using an integrated phase-locked loop (PLL), the DS1181L accepts an input clock signal in the range of 20MHz to 134MHz and delivers a spread-spectrum modulated output clo ...

... The DS1181L is a spread-spectrum clock modulator IC that reduces EMI in high clock-frequency-based, digital electronic equipment. Using an integrated phase-locked loop (PLL), the DS1181L accepts an input clock signal in the range of 20MHz to 134MHz and delivers a spread-spectrum modulated output clo ...

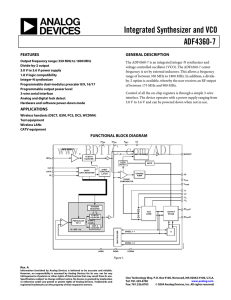

Integrated Synthesizer and VCO ADF4360-7 FEATURES

... VCO Output. The output level is programmable from −5 dBm to −14 dBm. See the Output Matching section for a description of the various output stages. VCO Complementary Output. The output level is programmable from −5 dBm to −14 dBm. See the Output Matching section for a description of the various out ...

... VCO Output. The output level is programmable from −5 dBm to −14 dBm. See the Output Matching section for a description of the various output stages. VCO Complementary Output. The output level is programmable from −5 dBm to −14 dBm. See the Output Matching section for a description of the various out ...