The Two-Stage Op-Amp Input Common

... where the output resistance of the cascode current source load, M8, is assumed to be much larger than the M7 output resistance, rop. we get an AOLDCofM2V/V. ...

... where the output resistance of the cascode current source load, M8, is assumed to be much larger than the M7 output resistance, rop. we get an AOLDCofM2V/V. ...

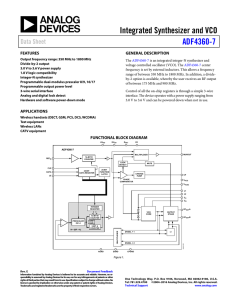

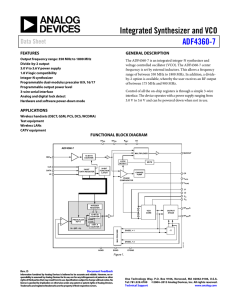

Integrated Synthesizer and VCO ADF4360-7

... VCO Output. The output level is programmable from −5 dBm to −14 dBm. See the Output Matching section for a description of the various output stages. VCO Complementary Output. The output level is programmable from −5 dBm to −14 dBm. See the Output Matching section for a description of the various out ...

... VCO Output. The output level is programmable from −5 dBm to −14 dBm. See the Output Matching section for a description of the various output stages. VCO Complementary Output. The output level is programmable from −5 dBm to −14 dBm. See the Output Matching section for a description of the various out ...

On-Chip Techniques for Electromagnetic Interference (EMI)

... injection of high frequency noise in power lines and wires acting as antennas that directly emit radiation. When these problems are created inside a chip it hampers the normal functionality of the chip. For example, EMI creates clock obstacle which results setup and hold time violation. In addition ...

... injection of high frequency noise in power lines and wires acting as antennas that directly emit radiation. When these problems are created inside a chip it hampers the normal functionality of the chip. For example, EMI creates clock obstacle which results setup and hold time violation. In addition ...

Digital Representation of Audio Information

... A) Plot the spectral magnitude of the Wiener filter for a signal plus noise process assuming a signal-to-noise ratio of -15 dB, 0 dB, and 15 dB. In words, describe how the SNR changes the spectral shape of the filter. Describe how this change makes sense for an optimal filter for this type. Hand in ...

... A) Plot the spectral magnitude of the Wiener filter for a signal plus noise process assuming a signal-to-noise ratio of -15 dB, 0 dB, and 15 dB. In words, describe how the SNR changes the spectral shape of the filter. Describe how this change makes sense for an optimal filter for this type. Hand in ...

... of +1 and -1. The gain switch is synchronised to set the gain to +1 exactly when the light is expected to be on, and to -1 when the light is expected to be off. Ideally, the output would then be a DC voltage corresponding to the amplitude of the light pulses. The low-pass filter rejects any other si ...

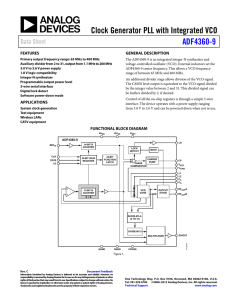

ADF4360-9 数据手册DataSheet 下载

... Control of all the on-chip registers is through a simple 3-wire interface. The device operates with a power supply ranging from 3.0 V to 3.6 V and can be powered down when not in use. ...

... Control of all the on-chip registers is through a simple 3-wire interface. The device operates with a power supply ranging from 3.0 V to 3.6 V and can be powered down when not in use. ...

Lecture 5

... The lay out of the circuit is very similar to that of the inverting amplifier or the integrator except that, in place of the feedback resistor R2 (of the inverter) or the capacitor C (of the integrator), we have a new component labelled D. In principle, and assuming the op amp to be ideal, in order ...

... The lay out of the circuit is very similar to that of the inverting amplifier or the integrator except that, in place of the feedback resistor R2 (of the inverter) or the capacitor C (of the integrator), we have a new component labelled D. In principle, and assuming the op amp to be ideal, in order ...

DM74LS74A Dual Positive-Edge-Triggered D Flip

... Preset, Clear and Complementary Outputs General Description This device contains two independent positive-edge-triggered D flip-flops with complementary outputs. The information on the D input is accepted by the flip-flops on the positive going edge of the clock pulse. The triggering occurs at a vol ...

... Preset, Clear and Complementary Outputs General Description This device contains two independent positive-edge-triggered D flip-flops with complementary outputs. The information on the D input is accepted by the flip-flops on the positive going edge of the clock pulse. The triggering occurs at a vol ...

Frequency response of feedback amplifiers

... • An ideal peak detector should produces a DC output waveform that is equal to the preceding peak value of the input signal • If the difference is positive, OpAmp produces current to charge ...

... • An ideal peak detector should produces a DC output waveform that is equal to the preceding peak value of the input signal • If the difference is positive, OpAmp produces current to charge ...

ADF4360-9 Clock Generator PLL with Integrated VCO (Rev. C)

... Control of all the on-chip registers is through a simple 3-wire interface. The device operates with a power supply ranging from 3.0 V to 3.6 V and can be powered down when not in use. ...

... Control of all the on-chip registers is through a simple 3-wire interface. The device operates with a power supply ranging from 3.0 V to 3.6 V and can be powered down when not in use. ...

digital seismic recorder specification standards

... signal path, produce time errors in the data which are recorded on tape. Reproduce (playback) filters and other time delays through the reproduce circuitry, do not introduce time errors in the recorded data, but the reproduce system does introduce time errors in signals displayed on camera monitor r ...

... signal path, produce time errors in the data which are recorded on tape. Reproduce (playback) filters and other time delays through the reproduce circuitry, do not introduce time errors in the recorded data, but the reproduce system does introduce time errors in signals displayed on camera monitor r ...

Single-Ended vs Differential Output Voltage Swing

... terminal, TX+ or TX-. All of our test data is taken from a single-ended measurement on an oscilloscope. Differential Signals A differential signal represents the difference between two signals. In terms of a transceiver, these signals are TX+ and TX-. This is the industry standard method of quantify ...

... terminal, TX+ or TX-. All of our test data is taken from a single-ended measurement on an oscilloscope. Differential Signals A differential signal represents the difference between two signals. In terms of a transceiver, these signals are TX+ and TX-. This is the industry standard method of quantify ...

Low Pwr Freq Synth for RF Pers Comm 550MHz, LMX2316 1.2GHz

... a digital phase locked loop technique. When combined with a high quality reference oscillator and loop filter, the LMX2306/16/26 provide the feedback tuning voltage for a voltage controlled oscillator to generate a low phase noise local oscillator signal. Serial data is transferred into the LMX2306/ ...

... a digital phase locked loop technique. When combined with a high quality reference oscillator and loop filter, the LMX2306/16/26 provide the feedback tuning voltage for a voltage controlled oscillator to generate a low phase noise local oscillator signal. Serial data is transferred into the LMX2306/ ...

Integrated Synthesizer and VCO ADF4360-7 Data Sheet FEATURES

... VCO Output. The output level is programmable from −5 dBm to −14 dBm. See the Output Matching section for a description of the various output stages. VCO Complementary Output. The output level is programmable from −5 dBm to −14 dBm. See the Output Matching section for a description of the various out ...

... VCO Output. The output level is programmable from −5 dBm to −14 dBm. See the Output Matching section for a description of the various output stages. VCO Complementary Output. The output level is programmable from −5 dBm to −14 dBm. See the Output Matching section for a description of the various out ...

AD827 High Speed, Low Power Dual Op Amp Data Sheet (REV. C)

... supplies 2 V p-p into a 100 Ω load while operating from ± 5 V supplies. The overall bandwidth of the circuit is approximately 7 MHz with 0.5 dB of peaking. Each half of the AD827 serves as an I/V converter and converts the output current of one of the two multipliers in the AD539 into an output volt ...

... supplies 2 V p-p into a 100 Ω load while operating from ± 5 V supplies. The overall bandwidth of the circuit is approximately 7 MHz with 0.5 dB of peaking. Each half of the AD827 serves as an I/V converter and converts the output current of one of the two multipliers in the AD539 into an output volt ...

eecs.tufts.edu - Tufts University

... unlikely. The only way to block magnetic field interference is with mu-metal, which is prohibitively expensive and fastidious. In the event of magnetic field induced noise, we would simply move the device away from the source of noise. Architecture: This device will identify paramagnetic substances ...

... unlikely. The only way to block magnetic field interference is with mu-metal, which is prohibitively expensive and fastidious. In the event of magnetic field induced noise, we would simply move the device away from the source of noise. Architecture: This device will identify paramagnetic substances ...

Lab6

... The 555 IC is unique in that it simply, cheaply, and accurately serves as a free-running astable multivibrator, square-wave generator, or signal source, as well as being useful as a pulse generator and serving as a solution to many special problems. It can be used with any power supply in the range ...

... The 555 IC is unique in that it simply, cheaply, and accurately serves as a free-running astable multivibrator, square-wave generator, or signal source, as well as being useful as a pulse generator and serving as a solution to many special problems. It can be used with any power supply in the range ...

Circuit Timing

... Maximum: longest possible delay Typical: under near-ideal condition Minimum: smallest. Many manufactures don’t specify this values in most moderate-speed logic families (74LS,74S TTL). Set to zero or 1/4~1/3 of typical delay if not specified. ...

... Maximum: longest possible delay Typical: under near-ideal condition Minimum: smallest. Many manufactures don’t specify this values in most moderate-speed logic families (74LS,74S TTL). Set to zero or 1/4~1/3 of typical delay if not specified. ...