SGA1263Z 数据资料DataSheet下载

... infringement of patents, or other rights of third parties, resulting from its use. No license is granted by implication or otherwise under any patent or patent rights of RFMD. RFMD reserves the right to change component circuitry, recommended application circuitry and specifications at any time with ...

... infringement of patents, or other rights of third parties, resulting from its use. No license is granted by implication or otherwise under any patent or patent rights of RFMD. RFMD reserves the right to change component circuitry, recommended application circuitry and specifications at any time with ...

07LAB5_rev - University of Guelph Physics

... the advantages of high input impedance at the two inputs and the large common mode rejection of the difference amplifier. ...

... the advantages of high input impedance at the two inputs and the large common mode rejection of the difference amplifier. ...

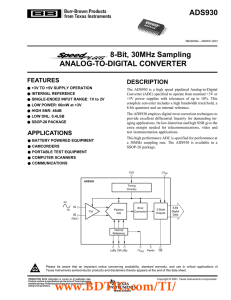

ADS930 数据资料 dataSheet 下载

... The pipelined quantizer architecture has 7 stages with each stage containing a two-bit quantizer and a two bit Digitalto-Analog Converter (DAC), as shown in Figure 2. Each two-bit quantizer stage converts on the edge of the subclock, which is the same frequency of the externally applied clock. The ...

... The pipelined quantizer architecture has 7 stages with each stage containing a two-bit quantizer and a two bit Digitalto-Analog Converter (DAC), as shown in Figure 2. Each two-bit quantizer stage converts on the edge of the subclock, which is the same frequency of the externally applied clock. The ...

MAX7033 315MHz/433MHz ASK Superheterodyne Receiver with AGC Lock General Description

... frequency range. The receiver has an RF input signal range of -114dBm to 0dBm. With few external components and a low-current power-down mode, it is ideal for cost-sensitive and power-sensitive applications typical in the automotive and consumer markets. The MAX7033 consists of a low-noise amplifier ...

... frequency range. The receiver has an RF input signal range of -114dBm to 0dBm. With few external components and a low-current power-down mode, it is ideal for cost-sensitive and power-sensitive applications typical in the automotive and consumer markets. The MAX7033 consists of a low-noise amplifier ...

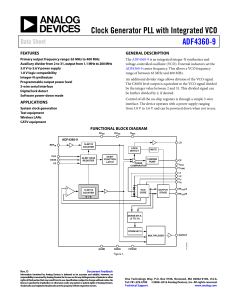

ADF4360-9 - Analog Devices

... Control of all the on-chip registers is through a simple 3-wire interface. The device operates with a power supply ranging from 3.0 V to 3.6 V and can be powered down when not in use. ...

... Control of all the on-chip registers is through a simple 3-wire interface. The device operates with a power supply ranging from 3.0 V to 3.6 V and can be powered down when not in use. ...

Introduction - Simple Media Networks, Inc

... the pads for the capacitors (prefix C) can accommodate 0603, 0805, and 1206-sized capacitors. The first capacitor in the EQ stages (C24 and C25) has a pad that can fit 2220 and through-hole parts if a high-pass filter with a very low cutoff is desired. A test point has been placed at the output of t ...

... the pads for the capacitors (prefix C) can accommodate 0603, 0805, and 1206-sized capacitors. The first capacitor in the EQ stages (C24 and C25) has a pad that can fit 2220 and through-hole parts if a high-pass filter with a very low cutoff is desired. A test point has been placed at the output of t ...

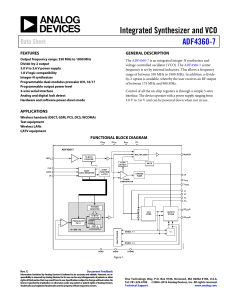

ADF4360-7 - Analog Devices

... VCO Output. The output level is programmable from −5 dBm to −14 dBm. See the Output Matching section for a description of the various output stages. VCO Complementary Output. The output level is programmable from −5 dBm to −14 dBm. See the Output Matching section for a description of the various out ...

... VCO Output. The output level is programmable from −5 dBm to −14 dBm. See the Output Matching section for a description of the various output stages. VCO Complementary Output. The output level is programmable from −5 dBm to −14 dBm. See the Output Matching section for a description of the various out ...

DS4M125/DS4M133/DS4M200 3.3V Margining Clock Oscillator with LVPECL/LVDS Output General Description

... The DS4M125/DS4M133/DS4M200 are available with either an LVPECL or LVDS output. The output can be disabled by pulling the OE pin low. When disabled, both OUTP and OUTN levels of the LVPECL driver go to the LVPECL bias voltage, while the output of the LVDS driver is a logical one. The OE input is an ...

... The DS4M125/DS4M133/DS4M200 are available with either an LVPECL or LVDS output. The output can be disabled by pulling the OE pin low. When disabled, both OUTP and OUTN levels of the LVPECL driver go to the LVPECL bias voltage, while the output of the LVDS driver is a logical one. The OE input is an ...

ADS831 数据资料 dataSheet 下载

... The ADS831 is a pipeline, CMOS Analog-to-Digital (A/D) converter that operates from a single +5V power supply. This converter provides excellent performance with a single-ended input and can be operated with a differential input for added spurious performance. This high performance converter include ...

... The ADS831 is a pipeline, CMOS Analog-to-Digital (A/D) converter that operates from a single +5V power supply. This converter provides excellent performance with a single-ended input and can be operated with a differential input for added spurious performance. This high performance converter include ...

II - CERN Accelerator School

... The presence of the beam phase loop enlarge the Robinson 1st stability limits since also a region with z < 0 (z > 0 for h < 0 ) becomes accessible. This is because the strong loop damping of the coherent motion overrides the Robinson antidamping. The Robinson 2nd limit is unaffected since it is a ...

... The presence of the beam phase loop enlarge the Robinson 1st stability limits since also a region with z < 0 (z > 0 for h < 0 ) becomes accessible. This is because the strong loop damping of the coherent motion overrides the Robinson antidamping. The Robinson 2nd limit is unaffected since it is a ...

ppt - K.f.u.p.m. OCW

... The circuit amplifies the difference between the voltages at its inverting (-) and noninverting (+) inputs. ...

... The circuit amplifies the difference between the voltages at its inverting (-) and noninverting (+) inputs. ...

Input Magic—Differential Signals Allow Input Swing to Exceed Supply Voltage

... input range bigger to get better signal-to-noise ratio (larger signals provide higher SNR), and making the input range smaller to ease the drive requirements. Over the years we’ve seen ADCs with 5-V supplies and 4-V p-p input ranges, and 3-V supplies with 2-V p-p input ranges, but these didn’t raise ...

... input range bigger to get better signal-to-noise ratio (larger signals provide higher SNR), and making the input range smaller to ease the drive requirements. Over the years we’ve seen ADCs with 5-V supplies and 4-V p-p input ranges, and 3-V supplies with 2-V p-p input ranges, but these didn’t raise ...

ICS9DB202.pdf

... While the information presented herein has been checked for both accuracy and reliability, Integrated Device Technology, Incorporated (IDT) assumes no responsibility for either its use or for infringement of any patents or other rights of third parties, which would result from its use. No other circ ...

... While the information presented herein has been checked for both accuracy and reliability, Integrated Device Technology, Incorporated (IDT) assumes no responsibility for either its use or for infringement of any patents or other rights of third parties, which would result from its use. No other circ ...

Integer-N/Fractional-N PLL Synthesizer ADF4155

... Charge Pump Output. When enabled, this output provides ±ICP to the external loop filter. The output of the loop filter is connected to the VTUNE pin of the external VCO. Charge Pump Ground. This output is the ground return pin for the CPOUT pin. Analog Power Supply. This pin ranges from 3.135 V to 3 ...

... Charge Pump Output. When enabled, this output provides ±ICP to the external loop filter. The output of the loop filter is connected to the VTUNE pin of the external VCO. Charge Pump Ground. This output is the ground return pin for the CPOUT pin. Analog Power Supply. This pin ranges from 3.135 V to 3 ...

Pure Sinusoidal PWM Signal Generation Technique

... signal with phase shift. The both signal are then synchronized by the logic circuit to generate positive and negative cycles. The two cycles are produced which then further transferred to the amplifier circuit. The amplifier circuit will amplify the signals. Gate drive circuit is granting PWM signal ...

... signal with phase shift. The both signal are then synchronized by the logic circuit to generate positive and negative cycles. The two cycles are produced which then further transferred to the amplifier circuit. The amplifier circuit will amplify the signals. Gate drive circuit is granting PWM signal ...

DC characteristics Input offset voltage

... Input offset current The difference between the bias currents at the input terminals of the op- amp is called as input offset current. The input terminals conduct a small value of dc current to bias the input transistors. Since the input transistors cannot be made identical, there exists a differenc ...

... Input offset current The difference between the bias currents at the input terminals of the op- amp is called as input offset current. The input terminals conduct a small value of dc current to bias the input transistors. Since the input transistors cannot be made identical, there exists a differenc ...