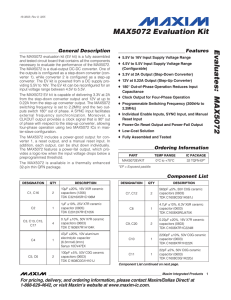

MAX12529 Dual, 96Msps, 12-Bit, IF/Baseband ADC General Description Features

... an externally applied reference and allows the reference to be shared between the two ADCs. The reference structure allows the full-scale analog input range to be adjusted from ±0.35V to ±1.15V. The MAX12529 provides a common-mode reference to simplify design and reduce external component count in d ...

... an externally applied reference and allows the reference to be shared between the two ADCs. The reference structure allows the full-scale analog input range to be adjusted from ±0.35V to ±1.15V. The MAX12529 provides a common-mode reference to simplify design and reduce external component count in d ...

A 30GHz Impulse Radiator with On-Chip Antennas for High-

... VCOs employ a symmetric topology. However, due to the symmetric topology of the VCO core, when modulated by a digital trigger signal, the starting phase of the impulse is random because the differential component of the noise at the VCO core sets the starting phase of the oscillation. Unlike symmetr ...

... VCOs employ a symmetric topology. However, due to the symmetric topology of the VCO core, when modulated by a digital trigger signal, the starting phase of the impulse is random because the differential component of the noise at the VCO core sets the starting phase of the oscillation. Unlike symmetr ...

Design of Arithmetic Circuits Using Resonant Tunneling Diodes and

... comparison function of a threshold gate because the sign of the modulation current is equivalent to the sign of the weighted sum. The logic state high (low) corresponds to a positive (negative) sign of the modulation current. Thus, after the bias voltage has produced a bistable output and a short re ...

... comparison function of a threshold gate because the sign of the modulation current is equivalent to the sign of the weighted sum. The logic state high (low) corresponds to a positive (negative) sign of the modulation current. Thus, after the bias voltage has produced a bistable output and a short re ...

CH7022 CH7022 SDTV/EDTV/HDTV Encoder

... this pin and XO. However, an external CMOS clock can drive the XI/FIN input. Crystal Output A parallel resonance 27MHz crystal (±20 ppm) should be attached between this pin and XI/FIN. However, if an external CMOS clock is attached to the XI/FIN input, XO should be left open. Pixel Clock Output ...

... this pin and XO. However, an external CMOS clock can drive the XI/FIN input. Crystal Output A parallel resonance 27MHz crystal (±20 ppm) should be attached between this pin and XI/FIN. However, if an external CMOS clock is attached to the XI/FIN input, XO should be left open. Pixel Clock Output ...

ECE 601 - Digital System Design & Synthesis Lecture 1

... By using direct set and direct reset inputs on the flip-flops (typically need only one or the other) Suppose that a FF is to be initialized to 1 and there are only library cells with with direct reset. What can you do? D Q D ...

... By using direct set and direct reset inputs on the flip-flops (typically need only one or the other) Suppose that a FF is to be initialized to 1 and there are only library cells with with direct reset. What can you do? D Q D ...

ADS1253 数据资料 dataSheet 下载

... When multiplexing inputs, it is possible to achieve sample rates close to 4kHz. This is due to the fact that it requires five internal conversion cycles for the data to fully settle, the data also must be read before the channel is changed. The DRDY signal indicates a valid result after the five cyc ...

... When multiplexing inputs, it is possible to achieve sample rates close to 4kHz. This is due to the fact that it requires five internal conversion cycles for the data to fully settle, the data also must be read before the channel is changed. The DRDY signal indicates a valid result after the five cyc ...

Features Description Functional Description XCR22LV10: 3V Zero

... XCR22LV10: 3V Zero Power, TotalCMOS, Universal PLD Output Type The signal from the OR array can be fed directly to the output pin (combinatorial function) or latched in the D-type flip-flop (registered function). The D-type flip-flop latches data on the rising edge of the clock and is controlled by ...

... XCR22LV10: 3V Zero Power, TotalCMOS, Universal PLD Output Type The signal from the OR array can be fed directly to the output pin (combinatorial function) or latched in the D-type flip-flop (registered function). The D-type flip-flop latches data on the rising edge of the clock and is controlled by ...

Xilinx XCR22LV10: 3V Zero Power, TotalCMOS, Universal PLD

... XCR22LV10: 3V Zero Power, TotalCMOS, Universal PLD Output Type The signal from the OR array can be fed directly to the output pin (combinatorial function) or latched in the D-type flip-flop (registered function). The D-type flip-flop latches data on the rising edge of the clock and is controlled by ...

... XCR22LV10: 3V Zero Power, TotalCMOS, Universal PLD Output Type The signal from the OR array can be fed directly to the output pin (combinatorial function) or latched in the D-type flip-flop (registered function). The D-type flip-flop latches data on the rising edge of the clock and is controlled by ...

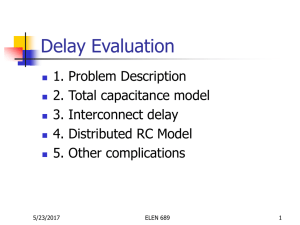

Mesh Currents - Texas A&M University

... Basic assumption: there exist an input ramp and Ceff, such that the driving point waveforms are the same Match I and Ie on average ...

... Basic assumption: there exist an input ramp and Ceff, such that the driving point waveforms are the same Match I and Ie on average ...

AD7485 数据手册DataSheet下载

... The ratio is dependent on the number of quantization levels in the digitization process; the more levels, the smaller the quantization noise. The theoretical signal to (noise + distortion) ratio for an ideal N-bit converter with a sine wave input is given by: ...

... The ratio is dependent on the number of quantization levels in the digitization process; the more levels, the smaller the quantization noise. The theoretical signal to (noise + distortion) ratio for an ideal N-bit converter with a sine wave input is given by: ...

MAX1185 Dual 10-Bit, 20Msps, 3V, Low-Power ADC with General Description

... The MAX1185 is a 3V, dual 10-bit analog-to-digital converter (ADC) featuring fully-differential wideband trackand-hold (T/H) inputs, driving two pipelined, nine-stage ADCs. The MAX1185 is optimized for low-power, high dynamic performance applications in imaging, instrumentation, and digital communic ...

... The MAX1185 is a 3V, dual 10-bit analog-to-digital converter (ADC) featuring fully-differential wideband trackand-hold (T/H) inputs, driving two pipelined, nine-stage ADCs. The MAX1185 is optimized for low-power, high dynamic performance applications in imaging, instrumentation, and digital communic ...

Paper Title (use style: paper title)

... the frequency dependence of the amplitude stability that agrees with the measured values. This model gave an indirect estimate of the single cycle relative phase stability of the resonator. The estimated value was much smaller than the directly measured one. This discrepancy needs further investigat ...

... the frequency dependence of the amplitude stability that agrees with the measured values. This model gave an indirect estimate of the single cycle relative phase stability of the resonator. The estimated value was much smaller than the directly measured one. This discrepancy needs further investigat ...

Time-to-digital converter

In electronic instrumentation and signal processing, a time to digital converter (abbreviated TDC) is a device for recognizing events and providing a digital representation of the time they occurred. For example, a TDC might output the time of arrival for each incoming pulse. Some applications wish to measure the time interval between two events rather than some notion of an absolute time.In electronics time-to-digital converters (TDCs) or time digitizers are devices commonly used to measure a time interval and convert it into digital (binary) output. In some cases interpolating TDCs are also called time counters (TCs).TDCs are used in many different applications, where the time interval between two signal pulses (start and stop pulse) should be determined. Measurement is started and stopped, when either the rising or the falling edge of a signal pulse crosses a set threshold. These requirements are fulfilled in many physical experiments, like time-of-flight and lifetime measurements in atomic and high energy physics, experiments that involve laser ranging and electronic research involving the testing of integrated circuits and high-speed data transfer.