Performance Optimization of Critical Nets Through

... effective coupling capacitance is reduced through the Miller effect) while the resistance of the wire increases. The decrease in effective capacitance on the line must overcompensate for the increase in resistance due to the splitting of the wire for this approach to be practical. Henceforth, the wi ...

... effective coupling capacitance is reduced through the Miller effect) while the resistance of the wire increases. The decrease in effective capacitance on the line must overcompensate for the increase in resistance due to the splitting of the wire for this approach to be practical. Henceforth, the wi ...

TWR-KM34Z75M Tower Module User`s Guide

... Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. Freescale reserves the ...

... Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. Freescale reserves the ...

MC10H645 (4) VIEW - Ropla Elektronik Sp. z oo

... Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any ...

... Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any ...

AD7653 数据手册DataSheet下载

... When SER/PAR is LOW, these outputs are used as Bit 2 and Bit 3 of the parallel port data output bus. When SER/PAR is HIGH, EXT/INT is LOW, and RDC/SDIN is LOW (serial master read after convert), these inputs, part of the serial port, are used to slow down, if desired, the internal serial clock that ...

... When SER/PAR is LOW, these outputs are used as Bit 2 and Bit 3 of the parallel port data output bus. When SER/PAR is HIGH, EXT/INT is LOW, and RDC/SDIN is LOW (serial master read after convert), these inputs, part of the serial port, are used to slow down, if desired, the internal serial clock that ...

"The design of sigma-delta modulation analog-to-digital converters,"

... tor output is eliminated with a digital decimation filter those elements. Descriptions of these elements are held in that also resamples the signal at the Nyquist rate, 2 B . The a generic form so that they can be mapped to a large power S , of the noise at the output of the filter is the sum variet ...

... tor output is eliminated with a digital decimation filter those elements. Descriptions of these elements are held in that also resamples the signal at the Nyquist rate, 2 B . The a generic form so that they can be mapped to a large power S , of the noise at the output of the filter is the sum variet ...

ENGR 210 Lab 6

... This part of the lab MUST be done in the lab using the real laboratory equipment. The following exercises are intended to guide you through the basic functions of the oscilloscope. try out other functions and experiments with the different settings. 1. Select, display, measure and listen to a sinuso ...

... This part of the lab MUST be done in the lab using the real laboratory equipment. The following exercises are intended to guide you through the basic functions of the oscilloscope. try out other functions and experiments with the different settings. 1. Select, display, measure and listen to a sinuso ...

AD7655 数据手册DataSheet下载

... The AD7655 is a low cost, simultaneous sampling, dualchannel, 16-bit, charge redistribution SAR, analog-to-digital converter that operates from a single 5 V power supply. It contains two low noise, wide bandwidth, track-and-hold amplifiers that allow simultaneous sampling, a high speed 16-bit sampli ...

... The AD7655 is a low cost, simultaneous sampling, dualchannel, 16-bit, charge redistribution SAR, analog-to-digital converter that operates from a single 5 V power supply. It contains two low noise, wide bandwidth, track-and-hold amplifiers that allow simultaneous sampling, a high speed 16-bit sampli ...

MAX1080/MAX1081 300ksps/400ksps, Single-Supply, Low-Power, 8-Channel, Serial 10-Bit ADCs with Internal Reference General Description

... Note 1: Tested at VDD1 = VDD2 = VDD(MIN), COM = GND, unipolar single-ended input mode. Note 2: Relative accuracy is the deviation of the analog value at any code from its theoretical value after the full-scale range has been calibrated. Note 3: Offset nulled. Note 4: Ground the “on” channel; sine wa ...

... Note 1: Tested at VDD1 = VDD2 = VDD(MIN), COM = GND, unipolar single-ended input mode. Note 2: Relative accuracy is the deviation of the analog value at any code from its theoretical value after the full-scale range has been calibrated. Note 3: Offset nulled. Note 4: Ground the “on” channel; sine wa ...

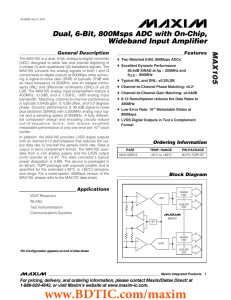

MAX105 Dual, 6-Bit, 800Msps ADC with On-Chip, Wideband Input Amplifier General Description

... The peak-to-peak input voltage required, causing a full-scale digitized output when using a trigonometric curve-fitting algorithm (e.g. FFT). Guaranteed by design and characterization. Common-mode rejection ratio is defined as the ratio of the change in the offset voltage to the change in the common ...

... The peak-to-peak input voltage required, causing a full-scale digitized output when using a trigonometric curve-fitting algorithm (e.g. FFT). Guaranteed by design and characterization. Common-mode rejection ratio is defined as the ratio of the change in the offset voltage to the change in the common ...

AD7663 数据手册DataSheet下载

... analog-to-digital converter that operates from a single 5 V power supply. It contains a high speed 16-bit sampling ADC, a resistor input scaler that allows various input ranges, an internal conversion clock, error correction circuits, and both serial and parallel system interface ports. The AD7663 i ...

... analog-to-digital converter that operates from a single 5 V power supply. It contains a high speed 16-bit sampling ADC, a resistor input scaler that allows various input ranges, an internal conversion clock, error correction circuits, and both serial and parallel system interface ports. The AD7663 i ...

PCM1794A 数据资料 dataSheet 下载

... The PCM1794A includes a power-on reset function. Figure 19 shows the operation of this function. With VDD > 2 V, the power-on reset function is enabled. The initialization sequence requires 1024 system clocks from the time VDD > 2 V. The PCM1794A also includes an external reset capability using the ...

... The PCM1794A includes a power-on reset function. Figure 19 shows the operation of this function. With VDD > 2 V, the power-on reset function is enabled. The initialization sequence requires 1024 system clocks from the time VDD > 2 V. The PCM1794A also includes an external reset capability using the ...

No Slide Title

... input bits and the reference voltage value. 1 bit DAC is designed to reproduce 2 (21) levels while an 8 bit DAC is designed for 256 (28) levels. Increasing the number of bits results in a finer resolution ...

... input bits and the reference voltage value. 1 bit DAC is designed to reproduce 2 (21) levels while an 8 bit DAC is designed for 256 (28) levels. Increasing the number of bits results in a finer resolution ...

Norbert H.L. Koster, Bettina J. Koster, Daniel Erni, and Adalbert Beyer

... of an oscillator circuit using JFETs as active devices typically depends significantly on the supply voltage. The main reason for this is the severe voltage dependence [4], [5] of the intrinsic transistor equivalent circuit elements, which represent the physical properties of the semiconductor subst ...

... of an oscillator circuit using JFETs as active devices typically depends significantly on the supply voltage. The main reason for this is the severe voltage dependence [4], [5] of the intrinsic transistor equivalent circuit elements, which represent the physical properties of the semiconductor subst ...

4-channel half-duplex m-lvds line transceivers

... receivers implement a failsafe by using an offset threshold. The xFSEN pins is used to select the Type-1 and Type-2 receiver for each of the channels. In addition, the driver rise and fall times are between 1 ns and 2 ns, complying with the M-LVDS standard to provide operation at 250 Mbps while also ...

... receivers implement a failsafe by using an offset threshold. The xFSEN pins is used to select the Type-1 and Type-2 receiver for each of the channels. In addition, the driver rise and fall times are between 1 ns and 2 ns, complying with the M-LVDS standard to provide operation at 250 Mbps while also ...

MATHSmanual2013.

... FALL controls determine how fast or slow the circuit will respond to signals applied to the Signal IN and Trigger IN. The range of times is larger than the typical Envelope or LFO. MATHS will create functions as slow as 25 minutes (Rise and Fall full CW and external control signals added to go into ...

... FALL controls determine how fast or slow the circuit will respond to signals applied to the Signal IN and Trigger IN. The range of times is larger than the typical Envelope or LFO. MATHS will create functions as slow as 25 minutes (Rise and Fall full CW and external control signals added to go into ...

AD421 - Analog Devices

... output value is pin selectable as either +3 V, +3.3 V or +5 V. 3. The AD421’s on-chip references can provide a precision reference voltage to other devices in the system. This reference voltage can be either +1.25 V or +2.5 V. 4. The AD421 is fully compatible with standard HART circuitry or other si ...

... output value is pin selectable as either +3 V, +3.3 V or +5 V. 3. The AD421’s on-chip references can provide a precision reference voltage to other devices in the system. This reference voltage can be either +1.25 V or +2.5 V. 4. The AD421 is fully compatible with standard HART circuitry or other si ...

AD421: Loop-Powered 4-20 mA DAC Data Sheet

... The range of loop voltages that can be used by the configuration shown in Figure 3 is determined by the FET breakdown and saturation voltages. The external FET parameters such as Vgs (off), IDSS and transconductance must be chosen so that the op amp output on the DRIVE pin can control the FET operat ...

... The range of loop voltages that can be used by the configuration shown in Figure 3 is determined by the FET breakdown and saturation voltages. The external FET parameters such as Vgs (off), IDSS and transconductance must be chosen so that the op amp output on the DRIVE pin can control the FET operat ...

Time-to-digital converter

In electronic instrumentation and signal processing, a time to digital converter (abbreviated TDC) is a device for recognizing events and providing a digital representation of the time they occurred. For example, a TDC might output the time of arrival for each incoming pulse. Some applications wish to measure the time interval between two events rather than some notion of an absolute time.In electronics time-to-digital converters (TDCs) or time digitizers are devices commonly used to measure a time interval and convert it into digital (binary) output. In some cases interpolating TDCs are also called time counters (TCs).TDCs are used in many different applications, where the time interval between two signal pulses (start and stop pulse) should be determined. Measurement is started and stopped, when either the rising or the falling edge of a signal pulse crosses a set threshold. These requirements are fulfilled in many physical experiments, like time-of-flight and lifetime measurements in atomic and high energy physics, experiments that involve laser ranging and electronic research involving the testing of integrated circuits and high-speed data transfer.