AD9709 数据手册DataSheet 下载

... independently using two external resistors, or IOUTFS for both DACs can be set by using a single external resistor. See the Gain Control Mode section for important date code information on this feature. The DACs utilize a segmented current source architecture combined with a proprietary switching te ...

... independently using two external resistors, or IOUTFS for both DACs can be set by using a single external resistor. See the Gain Control Mode section for important date code information on this feature. The DACs utilize a segmented current source architecture combined with a proprietary switching te ...

Electronic Computer-Aided Design

... case of letters in a SPICE netlist can be freely changed as the syntax is not case sensistive. Running SPICE on this netlist will produce the following output: --- AC Analysis --frequency: 60 Hz V(2): mag: 7.94876 ...

... case of letters in a SPICE netlist can be freely changed as the syntax is not case sensistive. Running SPICE on this netlist will produce the following output: --- AC Analysis --frequency: 60 Hz V(2): mag: 7.94876 ...

ds220_01.pdf

... operation, providing a mixed-mode operation not available in fixedarchitecture PAL devices. When registered output is selected, feedback from the register to the logic array bypasses the output buffer. When combinatorial output is selected, feedback comes from the I/O pin through the output buffer, ...

... operation, providing a mixed-mode operation not available in fixedarchitecture PAL devices. When registered output is selected, feedback from the register to the logic array bypasses the output buffer. When combinatorial output is selected, feedback comes from the I/O pin through the output buffer, ...

$doc.title

... • overall neatness and coherence in the structure of the report; • completion of all the required simulated and experimental steps; • inclusion of printouts, data tables, circuit and waveform sketches; • thoughtful and understandable responses to the guide questions; • adherence to the designated l ...

... • overall neatness and coherence in the structure of the report; • completion of all the required simulated and experimental steps; • inclusion of printouts, data tables, circuit and waveform sketches; • thoughtful and understandable responses to the guide questions; • adherence to the designated l ...

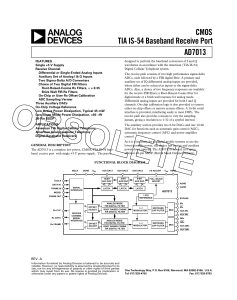

AD7013 CMOS TIA IS-54 Baseband Receive Port

... DxCLK Rising Edge to Last Falling Edge of RxCLK 3-State to Receive Channel Valid Receive Channel to 3-State Relinquish Time ...

... DxCLK Rising Edge to Last Falling Edge of RxCLK 3-State to Receive Channel Valid Receive Channel to 3-State Relinquish Time ...

MAX9317/MAX9317A/MAX9317B/MAX9317C Dual 1:5 Differential Clock Drivers with LVPECL Inputs and LVDS Outputs

... Note 1: Measurements are made with the device in thermal equilibrium. Note 2: Current into a pin is defined as positive. Current out of a pin is defined as negative. Note 3: DC parameters are production tested at +25°C. DC limits are guaranteed by design and characterization over the full operating ...

... Note 1: Measurements are made with the device in thermal equilibrium. Note 2: Current into a pin is defined as positive. Current out of a pin is defined as negative. Note 3: DC parameters are production tested at +25°C. DC limits are guaranteed by design and characterization over the full operating ...

AM3 AM2 Performance Tuning Guide

... HT Link Multiplier: This multiplier determines the clock speed of the HT Link. In the case of the AMD Phenom II X4 955BE CPU, the default value is x10 (10x200MHz = 2000MHz). In most cases a reboot is required for HT Link Multiplier value adjustment. The maximum value of HT Link Multiplier is x13 and ...

... HT Link Multiplier: This multiplier determines the clock speed of the HT Link. In the case of the AMD Phenom II X4 955BE CPU, the default value is x10 (10x200MHz = 2000MHz). In most cases a reboot is required for HT Link Multiplier value adjustment. The maximum value of HT Link Multiplier is x13 and ...

ADC081500 High Performance, Low Power, 8

... The ADC081500 is a low power, high performance CMOS analog-to-digital converter that digitizes signals to 8 bits resolution at sample rates up to 1.7 GSPS. Consuming a typical 1.2 W at 1.5 GSPS from a single 1.9 Volt supply, this device is ensured to have no missing codes over the full operating tem ...

... The ADC081500 is a low power, high performance CMOS analog-to-digital converter that digitizes signals to 8 bits resolution at sample rates up to 1.7 GSPS. Consuming a typical 1.2 W at 1.5 GSPS from a single 1.9 Volt supply, this device is ensured to have no missing codes over the full operating tem ...

DP8573A Real Time Clock (RTC)

... can the interrupt be generated externally. Each alarm compare bit in the Control Register will enable a specific byte for comparison to the clock. Disabling a compare byte is the same as setting its associated counter comparator to an ‘‘always equal’’ state. For example, to generate an interrupt at ...

... can the interrupt be generated externally. Each alarm compare bit in the Control Register will enable a specific byte for comparison to the clock. Disabling a compare byte is the same as setting its associated counter comparator to an ‘‘always equal’’ state. For example, to generate an interrupt at ...

BDTIC www.BDTIC.com/infineon Wireless Components ASK/FSK Transmitter 915 MHz

... divider chain is 128 in case of a 7.15 MHz crystal or 64 in case of a 14.3 MHz crystal and can be selected via CSEL (pin 16). The phase detector is a Type IV PD with charge pump. The passive loop filter is realized on chip. ...

... divider chain is 128 in case of a 7.15 MHz crystal or 64 in case of a 14.3 MHz crystal and can be selected via CSEL (pin 16). The phase detector is a Type IV PD with charge pump. The passive loop filter is realized on chip. ...

Why load capacitor is needed

... IC) parallel resonates with Cx1 and Cx2 in the feedback loop and provides approximately 180° phase shift. The amplified signals from the amplifier have 180° out-of-phase with its input signals. Loop gain greater than 1 and 0° (an integer multiple of 360°) phase shift are required to sustain oscillat ...

... IC) parallel resonates with Cx1 and Cx2 in the feedback loop and provides approximately 180° phase shift. The amplified signals from the amplifier have 180° out-of-phase with its input signals. Loop gain greater than 1 and 0° (an integer multiple of 360°) phase shift are required to sustain oscillat ...

ADS7813 数据资料 dataSheet 下载

... conversion period. Transitions on this digital input can easily couple into sensitive analog portions of the converter, adversely affecting the conversion results (see the Sensitivity to External Digital Signals section of this data sheet for more information). Ideally, the CONV input should go LOW ...

... conversion period. Transitions on this digital input can easily couple into sensitive analog portions of the converter, adversely affecting the conversion results (see the Sensitivity to External Digital Signals section of this data sheet for more information). Ideally, the CONV input should go LOW ...

jitter intro

... – In this section the period of the modulated clock decreases from the ideal. The net effect of the shorter periods results in a canceling out of the increased periods from the prior section. Note that the same number of clocks is completed after both sections. It is important to note that the sampl ...

... – In this section the period of the modulated clock decreases from the ideal. The net effect of the shorter periods results in a canceling out of the increased periods from the prior section. Note that the same number of clocks is completed after both sections. It is important to note that the sampl ...

Time-to-digital converter

In electronic instrumentation and signal processing, a time to digital converter (abbreviated TDC) is a device for recognizing events and providing a digital representation of the time they occurred. For example, a TDC might output the time of arrival for each incoming pulse. Some applications wish to measure the time interval between two events rather than some notion of an absolute time.In electronics time-to-digital converters (TDCs) or time digitizers are devices commonly used to measure a time interval and convert it into digital (binary) output. In some cases interpolating TDCs are also called time counters (TCs).TDCs are used in many different applications, where the time interval between two signal pulses (start and stop pulse) should be determined. Measurement is started and stopped, when either the rising or the falling edge of a signal pulse crosses a set threshold. These requirements are fulfilled in many physical experiments, like time-of-flight and lifetime measurements in atomic and high energy physics, experiments that involve laser ranging and electronic research involving the testing of integrated circuits and high-speed data transfer.