* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download document 8896755

Survey

Document related concepts

Transcript

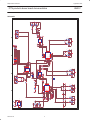

INTEGRATED CIRCUITS AN257 PTN products demo board documentation Kristina Avrionova 2001 Oct 08 Philips Semiconductors Application Note PTN products demo board documentation some loop involvement. PTN1111’s input signal could be either from the SMAs J6 and J8 or from PTN3322, as mentioned above. Where as the PTN 2111 could have its input signal from PTN1111–PTN3311 path or from PTN3322. PTN DEMO BOARD The PTN Demo Board utilizes the following products: PTN1111– a 1:10 PECL Clock distributing device, PTN3311– a PECL to LVDS translator, a PTN2111– a 1:10 LVDS Clock Distributing device, PTN3310– a LVDS to PECL translator, and PTN3322– a universal translator. For more information on the PTN products themselves, please, refer to their corresponding data sheets. Two of the PTN1111 outputs– !Q9 & Q9 and !Q7 & Q7, and two of the PTN2111 outputs– !Q8 & Q8 and !Q6 & Q6, are connected to SMAs, and they allow for any type of measurements on the clock devices, including skew between outputs. The purpose of the Demo Board is to show the simultaneous operation of all of the above devices, and it is the main mode of operation for the board. However, the board also allows for independent operation for some of the products. The input signal of PTN3311 must be provided by PTN1111. For the PTN3311 to be evaluated, resistors R27 and R28 should be soldered, and R23 and R24 should be dismounted. If simultaneous evaluation between PTN3311 and PTN2111 should be necessary, then PTN2111 must have its input from PTN3322. Please note that if all of the following four resistors R23, R24, R27, and R28 are on the board at the same time, there is just going to be double termination, so the quality of the signal might not be as desired and maximum performance is not guaranteed. In the main mode of operation, the PTN1111 gets its input signal from a pattern generator via the SMA J6 & SMA J8. One of the PTN1111 outputs goes into the receiver of PTN3311. The output of PTN3311 feds into one of the clock inputs of PTN2111 if and only if resistors R23 and R24 are assembled. Then, one of the outputs of PTN2111 is fed into the input of the PTN3310, and its outputs are connected to SMA J45 & J7, which could be fed into an oscilloscope. The original signal of this loop is PECL, and the final output signal is also PECL after it has been translated to and then again from LVDS. When the board is in the main mode of operation, PTN1111’s and PTN2111’s additional outputs could still be observed, and they will not affect the performance of the parts at all. In the following appendix, attached are: • Bill of materials • Schematic • Top layer layout and silk screen The PTN3322 could provide an input to either the PTN1111 or the PTN2111, as selected by the L/P pin of Switch 1. If the PTN3322 is to drive the PTN1111, resistors R13 and R14 must be soldered to the board, and then the PTN3322 becomes the default source of the main loop. The PTN1111’s clock select pin, Clk_Sel, on Switch 2 must be in open position. Alternatively, if the PTN3322 is to be a signaling source for the PTN2111, the Si pin of Switch 1 must be in an open position. SUPPORT For further information, please, check www.philipslogic.com/networking or e–mail to PTN–[email protected] The PTN3322 could be evaluated by itself. LDVS signal levels can be applied via SMA J3 and SMA J4, and then resistors R11 and R12 must be assembled, so PTN3322’s outputs are connected to SMA J1 and SMA J2 (R13 and R14 should be dismounted). If the PECL outputs should be evaluated, then the corresponding PECL terminations should be assembled, namely, resistors R7, R8, R9, and R10. If the LVDS outputs should be observed, then the former resistors should be removed, and only R6 should be assembled. To inquire about the availability of this board, please visit http://www.philipslogic.com/products/ptn/evalboards/rqstptn To learn about other PTN boards, please visit http://www.philipslogic.com/products/ptn/evalboards PTN1111 is the other PTN product that could be evaluated absolutely independently, while PTN2111 and PTN3311 do require 2001 Oct 08 AN257 2 Philips Semiconductors Application Note PTN products demo board documentation AN257 APPENDIX Bill of Materials Item Quantity Reference Part 1 2 BN2,BN1 Banana–Plug 2 2 C2,C1 Capacitor, 10 mF 3 18 C3,C4,C5,C6,C8,C10,C11, C14,C24,C25,C26,C27,C28,C29,C30,C31,C32,C33 Capacitor, 0.01 mF 4 13 C7,C9,C12,C13,C15,C16,C17, C18,C19,C20,C21,C22, C23 Capacitor, 0.1 mF 5 1 JP1 Header 2 6 18 J1,J2,J3,J4,J5,J6,J7,J8, J9, J10,J11,J12,J13,J14, J15,J16,J17,J18 SMA Connector 7 7 R1,R2,R3,R4,R5,R16,R17 Resistor, 10 kW 8 8 R6,R15,R20,R35,R40,R45, R46,R51 Resistor, 100 W 9 14 R7,R9,R18,R21,R25,R30, R31,R34,R36,R37,R42,R43, R48,R49 Resistor, 82.5 W 10 14 R8,R10,R19,R22,R26,R29, R32,R33,R38,R39,R41,R44, R47,R50 Resistor, 127 W 11 8 R11,R12,R13,R14,R23,R24, R27, R28 Resistor, 0 W 12 1 SW1 DIP Switch–5 13 1 SW2 DIP Switch–2 14 1 U1,TK71525SCL Voltage Regulator 15 1 U2, PTN3322 Universal Translator 16 1 U3, PTN3310 LVDS–PECL Translator 17 1 U4, PTN3311 PECL–LVDS Translator 18 1 U5, PTN1111 1:10 PECL Clock Distribution Device 19 1 U6, PTN2111 1:10 LVDS Clock Distribution Device 2001 Oct 08 3 A B C Vss Vss 1 4 SMA 4 SMA 10u C2 R37 4 4 Vout Vin 1 3 2 127 1 3 2 C24 1 J8 1 J6 TK71525SCL Gnd 3 3 3 U1 5 5 5 5 3 2 2 2 2 J13 5 0.01u R43 R38 Vdd2.5 5 Vss SMA 5 3 2 127 R29 R25 82.5 BN2 Vdd3.3 127 127 3 2 C25 J14 5 0.01u R44 R30 R26 82.5 82.5 5 SMA 82.5 Vdd3.3 R39 Vss 3 2 82.5 Vdd3.3 Vss 3 2 C26 R40 4 3 J15 5 PTN1111 5 Vss 3 2 82.5 SMA 127 R45 0.01u Vdd3.3 SW2 SW DIP–2 Vcc 2 3 Clk_sel Clk0 4 !Clk0 5 Vbb 6 Clk1 7 8 !Clk1 Vee 1 U5 1 2 3 2 C27 5 J16 0.01u R46 Q6 !Q6 Q5 !Q5 Q3 !Q3 Q4 !Q4 Clk_Sel R13 R12 5 SMA 127 24 23 22 21 20 19 18 17 Si R10 R9 5 Vss R27 R21 10k 10k 0 Ohm 4 4 R7 2 3 82.5 82.5 5 JP1 Vbb1111 100 SMA Vdd3.3 R6 0.01u C3 2 3 J1 Vss 5 C9 127 127 HEADER 2 Vbb2111 R28 C7 2 3 3 2 3 2 C28 4 1 2 3 5 0.01u 5 Vss 3 2 5 8 7 6 3 2 Vdd3.3 SMA 100 Voutp Voutn Vcc2 Vcc1 Vss R47 Gnd2 J17 Vss PTN3311 Gnd1 Vinp Vinn U4 0.1u 0.1u C5 SMA 0.1u 0.01u C4 2 3 J2 C10 0.1u R22 R8 4 4 0 Ohm 5 4 1 1 10u 82.5 R32 82.5 R33 127 R34 R35 0 Ohm 1 1 C1 C14 0.14 0 Ohm 2 4 1 D Vss C15 0.14 PTN3322 J18 5 0.01u C29 Vdd3.3 Vcc L/P 1V 1Z 2DE 2Z 2V Gnd U2 S1 2A 2B Gnd 1B 1A S0 1DE 5 SMA R23 0 Ohm 5 C16 0.14 R24 0 Ohm R36 R11 Vdd3.3 3 3 100 Vss 100 SW1 1 2 Vss C19 8 5 6 7 3 4 U6 6 Vss 9 8 7 5 10 2 3 4 1 SW DIP–5 100 R31 !Clk1 En Clk1 Clk0 !Clk0 Vbb Ck Si Vdd2.5 C13 0.1u PTN2111 3 2 0.1u 3 2 C20 5 J9 0.01u R41 5 Vss SMA 100 3 2 S1 17 19 18 20 22 21 23 24 3 2 C21 Vdd2.5 Q6 !Q6 Q5 !Q5 Q4 !Q4 Q3 !Q3 1DE 2DE L/P S0 5 J10 0.01u 5 SMA R1 R2 R3 R4 R5 10k 10k 10k 10k 10k 2 2 R16 Vdd3.3 3 2 Vss 100 3 2 C22 5 J11 0.01u R42 C11 5 Vss SMA 3 2 C12 Voutp Voutn 3 2 C23 0.1u Vcc2 Vcc1 Vinp Vinn Gnd2 PTN3310 Gnd1 100 0.1u 1 2 3 4 U3 5 J12 0.01u 8 7 6 5 5 5 SMA 5 4 4 tp C17 0.14 R19 0 Ohm Vdd3.3 R17 R14 2 3 J3 Vss 82.5 82.5 2 3 SMA 5 5 4 4 Banana–Plug C18 0.14 !Q0 Q1 Q9 !Q8 Vcco Q0 Vcco !Q9 9 !Q1 Q2 !Q2 Q8 !Q7 Q7 Vcco Vcco R20 0 Ohm 1 1 1 1 tp 127 1 1 1 1 1 1 Vcc Q0 Gnd !Q9 9 10 11 13 R18 R15 2 3 127 127 2 3 SMA J4 C8 C6 0.01u 0.01u 1 1 1 1 1 2 Banana–Plug 4 !Q1 Q2 Q8 !Q7 25 26 27 28 29 30 31 32 !Q2 Gnd Q7 Vcc 16 !Q0 Q1 Q9 !Q8 12 1 1 14 15 4 4 1 1 10 11 12 13 14 15 16 1 1 4 4 1 1 5 1 4 4 4 4 1 1 4 4 1 1 32 31 30 29 28 27 26 25 4 4 4 4 4 4 1 1 4 4 4 5 5 2 5 2 2 3 3 3 3 2001 Oct 08 4 4 4 SMA 4 J7 4 SMA J5 Vss A B C D Philips Semiconductors Application Note PTN products demo board documentation AN257 Schematic Philips Semiconductors Application Note PTN products demo board documentation Top Layer Layout and Silk Screen 2001 Oct 08 5 AN257 Philips Semiconductors Application Note PTN products demo board documentation AN257 Definitions Short-form specification — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook. Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 60134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability. Application information — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification. Disclaimers Life support — These products are not designed for use in life support appliances, devices or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application. Right to make changes — Philips Semiconductors reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified. Koninklijke Philips Electronics N.V. 2001 All rights reserved. Printed in U.S.A. Contact information For additional information please visit http://www.semiconductors.philips.com. Fax: +31 40 27 24825 Date of release: 10-01 For sales offices addresses send e-mail to: [email protected]. Document order number: 2001 Oct 08 6 9397 750 09055