TLC548 数据资料 dataSheet 下载

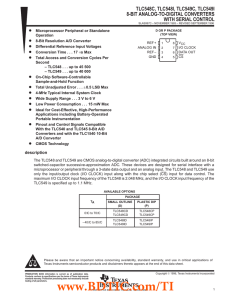

... and access speed, there are two control inputs: I/O CLOCK and chip select (CS). These control inputs and a TTL-compatible 3-state output facilitate serial communications with a microprocessor or minicomputer. A conversion can be completed in 17 µs or less, while complete input-conversion-output cycl ...

... and access speed, there are two control inputs: I/O CLOCK and chip select (CS). These control inputs and a TTL-compatible 3-state output facilitate serial communications with a microprocessor or minicomputer. A conversion can be completed in 17 µs or less, while complete input-conversion-output cycl ...

ICDesignMethodology(China)

... The micro electronics industry only stays well alive (continuous growth) because of this rapid progress. (performance doubles every ~2 years) – This rate of progress MUST be maintained to keep IC industry in good shape. – The life time of a technology generation is ~5 years Production is cheap in la ...

... The micro electronics industry only stays well alive (continuous growth) because of this rapid progress. (performance doubles every ~2 years) – This rate of progress MUST be maintained to keep IC industry in good shape. – The life time of a technology generation is ~5 years Production is cheap in la ...

Development OF PROTOTYPE Digital LLRF system at RRCAT

... RF processing is required to make the RF signal compatible with digital hardware. RF processing involves amplitude and phase control of RF signal using I/Q modulator, down conversion of RF signal to IF using mixers and generation of the synchronized clock and LO signal for sampling frequency and IF ...

... RF processing is required to make the RF signal compatible with digital hardware. RF processing involves amplitude and phase control of RF signal using I/Q modulator, down conversion of RF signal to IF using mixers and generation of the synchronized clock and LO signal for sampling frequency and IF ...

MOBILE CONTROLLED HOME APPLIANCES

... Crystal oscillator (3.579545MHz) IC 7474 D flip flop BC547 Transistor 6 V Relay ...

... Crystal oscillator (3.579545MHz) IC 7474 D flip flop BC547 Transistor 6 V Relay ...

UT54ACS169 - Aeroflex Microelectronic Solutions

... 1.Functional tests are conducted in accordance with MIL-STD-883 with the following input test conditions: VIH = VIH(min) + 20%, - 0%; VIL = VIL(max) + 0%, 50%, as specified herein, for TTL, CMOS, or Schmitt compatible inputs. Devices may be tested using any input voltage within the above specified r ...

... 1.Functional tests are conducted in accordance with MIL-STD-883 with the following input test conditions: VIH = VIH(min) + 20%, - 0%; VIL = VIL(max) + 0%, 50%, as specified herein, for TTL, CMOS, or Schmitt compatible inputs. Devices may be tested using any input voltage within the above specified r ...

Data Sheet

... inputs and outputs of the optocouplers. To obtain the maximum data transmission rate, both edges of the clock signal are being used to clock the data; if only one edge were used, the clock signal would need to be twice as fast. Propagation delay skew represents the uncertainty of where an edge might ...

... inputs and outputs of the optocouplers. To obtain the maximum data transmission rate, both edges of the clock signal are being used to clock the data; if only one edge were used, the clock signal would need to be twice as fast. Propagation delay skew represents the uncertainty of where an edge might ...

A high-frequency CMOS multi-modulus divider for PLL frequency

... extended to realize the ratioed DFF in Fig. 5(b). When CLK = 0, it is in Hold Mode. Since MN3 is off in this mode, node b is precharged to VDD through MP3. Thus, since both of MN4 and MP4 are off, the data is in node Q is held. The P-C2MOS stage functions as an pseudo-inverter now, and the data D is ...

... extended to realize the ratioed DFF in Fig. 5(b). When CLK = 0, it is in Hold Mode. Since MN3 is off in this mode, node b is precharged to VDD through MP3. Thus, since both of MN4 and MP4 are off, the data is in node Q is held. The P-C2MOS stage functions as an pseudo-inverter now, and the data D is ...

emt212_ch.4 oscillators

... frequency f1 which occurs when XL = XC. At this frequency, crystal offers a very low impedance to the ...

... frequency f1 which occurs when XL = XC. At this frequency, crystal offers a very low impedance to the ...

tema8 tema9 - WordPress.com

... ‘0’ to ‘1’, which set the R-S flip-flop to state ‘1’ on the complementary output. Then the key transistor switches to saturation state and the output level becomes low. From this moment starts the process of capacitor discharging through resistor RB and saturated key transistor to negative pole of p ...

... ‘0’ to ‘1’, which set the R-S flip-flop to state ‘1’ on the complementary output. Then the key transistor switches to saturation state and the output level becomes low. From this moment starts the process of capacitor discharging through resistor RB and saturated key transistor to negative pole of p ...

Defense-Grade Virtex-6Q Family Overview

... The Defense-Grade Virtex®-6Q family provides the most advanced features in the Aerospace & Defense FPGA market and represents the 3rd generation of secure silicon architecture products from Xilinx. Virtex-6Q FPGAs are the programmable silicon foundation for Targeted Design Platforms that deliver int ...

... The Defense-Grade Virtex®-6Q family provides the most advanced features in the Aerospace & Defense FPGA market and represents the 3rd generation of secure silicon architecture products from Xilinx. Virtex-6Q FPGAs are the programmable silicon foundation for Targeted Design Platforms that deliver int ...

lm3909

... used indicating the front and back indicators. To turn left move the switch to left. This will turn on the front left LED (D1) and back left LED (D3). To turn right move the switch to right .This will turn on the front right LED (D2) and back right LED (D4). By using the timing capacitor for voltage ...

... used indicating the front and back indicators. To turn left move the switch to left. This will turn on the front left LED (D1) and back left LED (D3). To turn right move the switch to right .This will turn on the front right LED (D2) and back right LED (D4). By using the timing capacitor for voltage ...

X01414271431

... In this paper describes design of three operational amplifier, transmission gate and capacitor banks to independently control , bandwidth, and the peak voltage gain steps for the dip frequency response. The equalizer located at the receiver removes the effects of ISI, CCI, burst noise interference a ...

... In this paper describes design of three operational amplifier, transmission gate and capacitor banks to independently control , bandwidth, and the peak voltage gain steps for the dip frequency response. The equalizer located at the receiver removes the effects of ISI, CCI, burst noise interference a ...

MAX1003 Low-Power, 90Msps, Dual 6-Bit ADC _______________General Description ____________________________Features

... The MAX1003 is a dual, 6-bit analog-to-digital converter (ADC) that combines high-speed, low-power operation with a user-selectable input range, an internal reference, and a clock oscillator. The dual parallel ADCs are designed to convert in-phase (I) and quadrature (Q) analog signals into two 6-bit ...

... The MAX1003 is a dual, 6-bit analog-to-digital converter (ADC) that combines high-speed, low-power operation with a user-selectable input range, an internal reference, and a clock oscillator. The dual parallel ADCs are designed to convert in-phase (I) and quadrature (Q) analog signals into two 6-bit ...

Improved sense-amplifier-based flip-flop

... corresponding to the failing clock frequency was calculated and entered into a set of equations describing the timing relationship between the flip-flop parameters and the signal delay. The clock frequency was changed in the 400–700 MHz range using an on-chip time-base generator. The clock frequency ...

... corresponding to the failing clock frequency was calculated and entered into a set of equations describing the timing relationship between the flip-flop parameters and the signal delay. The clock frequency was changed in the 400–700 MHz range using an on-chip time-base generator. The clock frequency ...

MAX144/MAX145 Full Data Sheet (PDF)

... capacitance of the ADC. Source impedances below 1k have no significant impact on the AC perfor- mance of the MAX144/MAX145. Higher source impedances can be used if a 0.01µF capacitor is connected to the individual analog inputs. Together with the input impedance, this capacitor forms an RC filter, ...

... capacitance of the ADC. Source impedances below 1k have no significant impact on the AC perfor- mance of the MAX144/MAX145. Higher source impedances can be used if a 0.01µF capacitor is connected to the individual analog inputs. Together with the input impedance, this capacitor forms an RC filter, ...

Time-to-digital converter

In electronic instrumentation and signal processing, a time to digital converter (abbreviated TDC) is a device for recognizing events and providing a digital representation of the time they occurred. For example, a TDC might output the time of arrival for each incoming pulse. Some applications wish to measure the time interval between two events rather than some notion of an absolute time.In electronics time-to-digital converters (TDCs) or time digitizers are devices commonly used to measure a time interval and convert it into digital (binary) output. In some cases interpolating TDCs are also called time counters (TCs).TDCs are used in many different applications, where the time interval between two signal pulses (start and stop pulse) should be determined. Measurement is started and stopped, when either the rising or the falling edge of a signal pulse crosses a set threshold. These requirements are fulfilled in many physical experiments, like time-of-flight and lifetime measurements in atomic and high energy physics, experiments that involve laser ranging and electronic research involving the testing of integrated circuits and high-speed data transfer.