Analog Devices Welcomes Hittite Microwave Corporation

... A/D Converter performance is obtained with LVDS or LVPECL clock with fast edges. CMOS and sine wave clock inputs will result in slightly degraded jitter performance. If the clock is generated by other circuitry, it should be re-timed with a low jitter master clock as the last operation before it is ...

... A/D Converter performance is obtained with LVDS or LVPECL clock with fast edges. CMOS and sine wave clock inputs will result in slightly degraded jitter performance. If the clock is generated by other circuitry, it should be re-timed with a low jitter master clock as the last operation before it is ...

RC Circuits

... a) The charging time will decrease because the rate of charge flowing to the plates will increase. b) The charging time will decrease because the rate of charge flowing to the plates will decrease. c) The charging time will not change because the charging time does not depend on the battery emf. d) ...

... a) The charging time will decrease because the rate of charge flowing to the plates will increase. b) The charging time will decrease because the rate of charge flowing to the plates will decrease. c) The charging time will not change because the charging time does not depend on the battery emf. d) ...

AD1862 (Rev. A) - Analog Devices

... The design of the AD1862 uses a combination of segmented decoder, R-2R topology and digital offset to produce low distortion at all signal amplitudes. The digital offset technique shifts the midscale output voltage (0 V) away from the MSB transition of the device. Therefore, small amplitude signals ...

... The design of the AD1862 uses a combination of segmented decoder, R-2R topology and digital offset to produce low distortion at all signal amplitudes. The digital offset technique shifts the midscale output voltage (0 V) away from the MSB transition of the device. Therefore, small amplitude signals ...

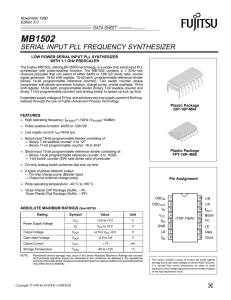

Product Datasheet

... Isoloop devices achieve their low power consumption from the manner by which they transmit data across the isolation barrier. By detecting the edge transitions of the input logic signal and converting these to narrow current pulses, a magnetic field is created around the GMR Wheatstone bridge. Depe ...

... Isoloop devices achieve their low power consumption from the manner by which they transmit data across the isolation barrier. By detecting the edge transitions of the input logic signal and converting these to narrow current pulses, a magnetic field is created around the GMR Wheatstone bridge. Depe ...

Method for measurement of the sensitivity of crystal resonators to

... amplifiers is used for this purpose. In practice, the reference signal level is set at about +10dBm, which results in a lower level in the measurement signal because of the attenuation of the crystal network, but this configuration still gives adequate phase detector gain. The resulting baseband vol ...

... amplifiers is used for this purpose. In practice, the reference signal level is set at about +10dBm, which results in a lower level in the measurement signal because of the attenuation of the crystal network, but this configuration still gives adequate phase detector gain. The resulting baseband vol ...

APPLICATION NOTE - TDA8768A/C2 - 12-BIT HIGH-SPEED A/D CONVERTER DEMONSTRATION BOARD

... The dynamic ADC analog signal VI and VIN are connected through a 1:1 RF wideband transformer and a 220nF AC coupling to the external generator by the IN SMA connector. This connector is adapted by a 50Ω microstrip line and is connected to a 100Ω resistor. This value is calculated to have 50Ω equival ...

... The dynamic ADC analog signal VI and VIN are connected through a 1:1 RF wideband transformer and a 220nF AC coupling to the external generator by the IN SMA connector. This connector is adapted by a 50Ω microstrip line and is connected to a 100Ω resistor. This value is calculated to have 50Ω equival ...

Overview of the Architecture, Circuit Design, and Physical

... Requires both true and complementary signals. Static implementation tends to hit speed wall earlier. Approach for design Implement ...

... Requires both true and complementary signals. Static implementation tends to hit speed wall earlier. Approach for design Implement ...

LECTURES 15 and 16

... • This type of ADC, however, does not employ a counter to provide the input to the DAC but employs a register instead. The DAC provides a reference variable voltage in steps. The control logic modifies the contents of the register bit by bit until the register data are the digital equivalent of the ...

... • This type of ADC, however, does not employ a counter to provide the input to the DAC but employs a register instead. The DAC provides a reference variable voltage in steps. The control logic modifies the contents of the register bit by bit until the register data are the digital equivalent of the ...

Enpirion EN5364QI 6A and EN5394QI 9A DCDC Converter

... Test Recommendations To guarantee measurement accuracy, the following precautions should be observed: 1. Make all input and output voltage measurements at the board using the test points provided. This will eliminate voltage drop across the line and load cables that can produce false readings. 2. Me ...

... Test Recommendations To guarantee measurement accuracy, the following precautions should be observed: 1. Make all input and output voltage measurements at the board using the test points provided. This will eliminate voltage drop across the line and load cables that can produce false readings. 2. Me ...

IC Crystal Oscillator Circuits

... For this 20MHz design this equates to 35o for the propagation delay and 67o for the working frequency. The remaining 72o is generated by Rlim + the inverting gates output ‘resistance’ and the PI network comprising C1, C2 and the Quartz Crystal. It is the additional phase shift through the inverting ...

... For this 20MHz design this equates to 35o for the propagation delay and 67o for the working frequency. The remaining 72o is generated by Rlim + the inverting gates output ‘resistance’ and the PI network comprising C1, C2 and the Quartz Crystal. It is the additional phase shift through the inverting ...

Optical Link Driver/Receiver for Silicon Trackers K.K. Gan The Ohio State University

... Use Bi-Phase Mark Encoding? ...

... Use Bi-Phase Mark Encoding? ...

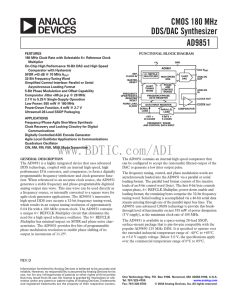

AD9851 数据手册DataSheet 下载

... The DAC’s external RSET connection—nominally a 3.92 k resistor to ground for 10 mA out. This sets the DAC full-scale output current available from IOUT and IOUTB. RSET = 39.93/IOUT. Voltage Output Negative. The comparator’s complementary CMOS logic level output. Voltage Output Positive. The compara ...

... The DAC’s external RSET connection—nominally a 3.92 k resistor to ground for 10 mA out. This sets the DAC full-scale output current available from IOUT and IOUTB. RSET = 39.93/IOUT. Voltage Output Negative. The comparator’s complementary CMOS logic level output. Voltage Output Positive. The compara ...

ELGProject - School of Electrical Engineering and Computer

... The bisection method for finding roots, which is alternatively called binary chopping, interval halving, or Bolzano’s method, is one type of incremental search method in which the interval is always divided in half. If a function changes sign over an interval, the function value at the midpoint is e ...

... The bisection method for finding roots, which is alternatively called binary chopping, interval halving, or Bolzano’s method, is one type of incremental search method in which the interval is always divided in half. If a function changes sign over an interval, the function value at the midpoint is e ...

ICS552-02 L S 2 I

... While the information presented herein has been checked for both accuracy and reliability, Integrated Circuit Systems (ICS) assumes no responsibility for either its use or for the infringement of any patents or other rights of third parties, which would result from its use. No other circuits, patent ...

... While the information presented herein has been checked for both accuracy and reliability, Integrated Circuit Systems (ICS) assumes no responsibility for either its use or for the infringement of any patents or other rights of third parties, which would result from its use. No other circuits, patent ...

ADS8322 数据资料 dataSheet 下载

... voltage difference between the +IN and –IN inputs is captured on the internal capacitor array. The voltage on the –IN input is limited between –0.1V and 0.5V, allowing the input to reject small signals which are common to both the +IN and –IN inputs. The +IN input has a range of –0.1V to +VA + 0.1V. ...

... voltage difference between the +IN and –IN inputs is captured on the internal capacitor array. The voltage on the –IN input is limited between –0.1V and 0.5V, allowing the input to reject small signals which are common to both the +IN and –IN inputs. The +IN input has a range of –0.1V to +VA + 0.1V. ...

Time-to-digital converter

In electronic instrumentation and signal processing, a time to digital converter (abbreviated TDC) is a device for recognizing events and providing a digital representation of the time they occurred. For example, a TDC might output the time of arrival for each incoming pulse. Some applications wish to measure the time interval between two events rather than some notion of an absolute time.In electronics time-to-digital converters (TDCs) or time digitizers are devices commonly used to measure a time interval and convert it into digital (binary) output. In some cases interpolating TDCs are also called time counters (TCs).TDCs are used in many different applications, where the time interval between two signal pulses (start and stop pulse) should be determined. Measurement is started and stopped, when either the rising or the falling edge of a signal pulse crosses a set threshold. These requirements are fulfilled in many physical experiments, like time-of-flight and lifetime measurements in atomic and high energy physics, experiments that involve laser ranging and electronic research involving the testing of integrated circuits and high-speed data transfer.