Hello, and welcome to this presentation of the STM32CubeMX Code

... The user interface is a great tool, it is a universal assistant for all STM32 microcontrollers. However it cannot tackle all the details of each product while providing a useful overview of the diversified STM32 portfolio. In case of doubt, please refer to the reference manual or datasheet for more ...

... The user interface is a great tool, it is a universal assistant for all STM32 microcontrollers. However it cannot tackle all the details of each product while providing a useful overview of the diversified STM32 portfolio. In case of doubt, please refer to the reference manual or datasheet for more ...

DRAM - KTU - Kompiuterių katedra

... • Clock is used to drive an internal finite state machine that pipelines incoming instructions • Pipelining means that the chip can accept a new instruction before it has finished processing the previous one. E.g. in a pipelined read, the requested data appears after a fixed number of clock pulses a ...

... • Clock is used to drive an internal finite state machine that pipelines incoming instructions • Pipelining means that the chip can accept a new instruction before it has finished processing the previous one. E.g. in a pipelined read, the requested data appears after a fixed number of clock pulses a ...

Design Review David Schlais – Robbie Wankewycz – Jamie Barber

... will go to an ADC before being sent to the FPGA. Although the signal from the PMTs (see 2.2.2) is also analog, it resembles a digital pulse, which can be used for the count/no-count detection needed without an ADC. The FPGA will be required to take data from the PMTs (which comes out as analog volta ...

... will go to an ADC before being sent to the FPGA. Although the signal from the PMTs (see 2.2.2) is also analog, it resembles a digital pulse, which can be used for the count/no-count detection needed without an ADC. The FPGA will be required to take data from the PMTs (which comes out as analog volta ...

sppcx7450-rev3Current 6-20-08b.pub

... ever exceeds the user-adjustable current set point, the driver truncates the output current pulse, electronically shorts the output to ground, and displays an error message on the front panel display. In addition, the PCX-7450 has a factory-set hardwarecontrolled current-limit and an independent, us ...

... ever exceeds the user-adjustable current set point, the driver truncates the output current pulse, electronically shorts the output to ground, and displays an error message on the front panel display. In addition, the PCX-7450 has a factory-set hardwarecontrolled current-limit and an independent, us ...

IOSR Journal of VLSI and Signal Processing (IOSR-JVSP)

... LC-QVCOs have two major blocks; a couple of same LC-VCOs and combination circuit, here the two blocks will affect the entire communication system output. To progress the phase noise in the formerly discussed LC-QVCOs, we are mainly concentrating on the combination circuit, experimenting a variety of ...

... LC-QVCOs have two major blocks; a couple of same LC-VCOs and combination circuit, here the two blocks will affect the entire communication system output. To progress the phase noise in the formerly discussed LC-QVCOs, we are mainly concentrating on the combination circuit, experimenting a variety of ...

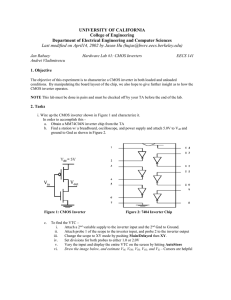

Using an I/O port pin as an A/D converter input

... implement an A/D converter function. Although not intended for precision A/D conversion applications, nevertheless the concept can be practically used for low resolution, low cost A/D function implementation. Arbitrarily examination of the discharge slope on an oscilloscope trace, although not measu ...

... implement an A/D converter function. Although not intended for precision A/D conversion applications, nevertheless the concept can be practically used for low resolution, low cost A/D function implementation. Arbitrarily examination of the discharge slope on an oscilloscope trace, although not measu ...

Calorimeter Electronics

... wide enough to insure that the ADC sampling can “catch” the peak. If we define the “peak” as the part of the signal waveform near peak, where the voltage difference should not exceeds 0.1%, the peak width is 126ns. Hence for the time constant of the shaping circuit of 1s, two or three ADC samples c ...

... wide enough to insure that the ADC sampling can “catch” the peak. If we define the “peak” as the part of the signal waveform near peak, where the voltage difference should not exceeds 0.1%, the peak width is 126ns. Hence for the time constant of the shaping circuit of 1s, two or three ADC samples c ...

A Shared-Well Dual-Supply-Voltage 64-bit ALU

... adder and in the loopback bus. A 3 mm2 test chip in 0.18- m 1.8-V five-metal with local interconnect CMOS technology that contains six ALUs and test circuitry operates at 1.16 GHz at the nominal supply. For target delay increase of 2.8% energy savings are 25.3% using dual supplies, while for 8.3% in ...

... adder and in the loopback bus. A 3 mm2 test chip in 0.18- m 1.8-V five-metal with local interconnect CMOS technology that contains six ALUs and test circuitry operates at 1.16 GHz at the nominal supply. For target delay increase of 2.8% energy savings are 25.3% using dual supplies, while for 8.3% in ...

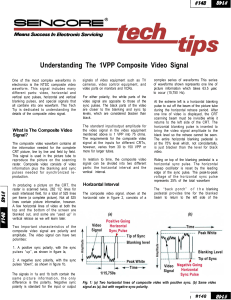

Understanding The 1VPP Composite Video Signal

... This signal is used in the picture tube to reproduce the picture on the scanning raster. Composite video consists of video information plus the blanking and sync pulses needed for synchronized reproduction. In producing a picture on the CRT, the raster is scanned twice, 262 1/2 lines for each interl ...

... This signal is used in the picture tube to reproduce the picture on the scanning raster. Composite video consists of video information plus the blanking and sync pulses needed for synchronized reproduction. In producing a picture on the CRT, the raster is scanned twice, 262 1/2 lines for each interl ...

10 GHz, Class-B, 0.5 V, 130 nm CMOS Cross

... can be easily recognised and analysed as such. The method has own limitations. As the arrangement of circuit parasitics has been also changed, their influence on resonant frequency of the oscillator may be affected [4]. However, if the parasitics are much smaller than the LC components, the resultin ...

... can be easily recognised and analysed as such. The method has own limitations. As the arrangement of circuit parasitics has been also changed, their influence on resonant frequency of the oscillator may be affected [4]. However, if the parasitics are much smaller than the LC components, the resultin ...

Understanding Signal Integrity

... is an ideal plane, as in most circuit-board applications, the relative amount of capacitive and inductive coupling is about the same for a given system, establishing the geometry for minimum crosstalk. When the return path consists of discrete leads in a package or discrete pins in a connector rathe ...

... is an ideal plane, as in most circuit-board applications, the relative amount of capacitive and inductive coupling is about the same for a given system, establishing the geometry for minimum crosstalk. When the return path consists of discrete leads in a package or discrete pins in a connector rathe ...

Microsoft PowerPoint

... • Differential non-linearity: Deviation of the difference between two consecutive codes from ideal 1 LSB. An absolute non-linearity of +/- ¼ LSB results in differential non-linearity of +/- ½ LSB. • What happens if non-linearity exceeds +/- ½ LSB ? ...

... • Differential non-linearity: Deviation of the difference between two consecutive codes from ideal 1 LSB. An absolute non-linearity of +/- ¼ LSB results in differential non-linearity of +/- ½ LSB. • What happens if non-linearity exceeds +/- ½ LSB ? ...

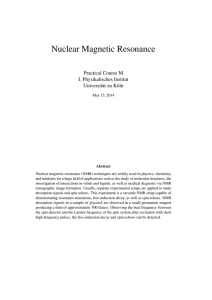

Nuclear magnetic resonance - I. Physikalisches Institut

... circuit during the pulse pauses, in which the signal is observed. This is realized by a switch consisting of two parallel connected diodes (see Fig. 5). The low-resistant generator output is adapted to the high-resistant (R > 1 kΩ) resonant circuit of the spin detector using a matching network. In t ...

... circuit during the pulse pauses, in which the signal is observed. This is realized by a switch consisting of two parallel connected diodes (see Fig. 5). The low-resistant generator output is adapted to the high-resistant (R > 1 kΩ) resonant circuit of the spin detector using a matching network. In t ...

Time-to-digital converter

In electronic instrumentation and signal processing, a time to digital converter (abbreviated TDC) is a device for recognizing events and providing a digital representation of the time they occurred. For example, a TDC might output the time of arrival for each incoming pulse. Some applications wish to measure the time interval between two events rather than some notion of an absolute time.In electronics time-to-digital converters (TDCs) or time digitizers are devices commonly used to measure a time interval and convert it into digital (binary) output. In some cases interpolating TDCs are also called time counters (TCs).TDCs are used in many different applications, where the time interval between two signal pulses (start and stop pulse) should be determined. Measurement is started and stopped, when either the rising or the falling edge of a signal pulse crosses a set threshold. These requirements are fulfilled in many physical experiments, like time-of-flight and lifetime measurements in atomic and high energy physics, experiments that involve laser ranging and electronic research involving the testing of integrated circuits and high-speed data transfer.