CN-0192

... buffer circuit shown in Figure 1 also provides gain to the AD2S1210 excitation output signal, as well as current drive capability. This circuit note describes the performance requirements and the recommended excitation buffer topology. A typical resolver has an input resistance in range of 100 Ω to ...

... buffer circuit shown in Figure 1 also provides gain to the AD2S1210 excitation output signal, as well as current drive capability. This circuit note describes the performance requirements and the recommended excitation buffer topology. A typical resolver has an input resistance in range of 100 Ω to ...

Introduction and Digital Images

... across L opposing the change. The inductor voltage initially is a negative voltage that is equal and opposite to the generator; then it exponentially increases. The induced voltage across L initially opposes the VS change in the source voltage. ...

... across L opposing the change. The inductor voltage initially is a negative voltage that is equal and opposite to the generator; then it exponentially increases. The induced voltage across L initially opposes the VS change in the source voltage. ...

NTUST-EE-2013S

... across L opposing the change. The inductor voltage initially is a negative voltage that is equal and opposite to the generator; then it exponentially increases. • The induced L voltage across L The output voltage initially opposes ...

... across L opposing the change. The inductor voltage initially is a negative voltage that is equal and opposite to the generator; then it exponentially increases. • The induced L voltage across L The output voltage initially opposes ...

ics844021-01i.pdf

... The aforementioned trademarks, HiPerClockS™ and FemtoClocks™ are a trademark of Integrated Circuit Systems, Inc. or its subsidiaries in the United States and/or other countries. While the information presented herein has been checked for both accuracy and reliability, Integrated Circuit Systems, Inc ...

... The aforementioned trademarks, HiPerClockS™ and FemtoClocks™ are a trademark of Integrated Circuit Systems, Inc. or its subsidiaries in the United States and/or other countries. While the information presented herein has been checked for both accuracy and reliability, Integrated Circuit Systems, Inc ...

Superconducting Technologies

... Demonstrated to 60 Gb/s through 2 solder bumps, 4 resistor, and 4 transmission lines on chip and MCM Timing errors produced BER floor above 30 Gb/s ...

... Demonstrated to 60 Gb/s through 2 solder bumps, 4 resistor, and 4 transmission lines on chip and MCM Timing errors produced BER floor above 30 Gb/s ...

Issues with CSC`s - Indico

... … if current limits for ALCT are OK, I will send to V. Sytnik to implement after this meeting… 28 Jan 2009 ...

... … if current limits for ALCT are OK, I will send to V. Sytnik to implement after this meeting… 28 Jan 2009 ...

GAAS: A Fully Integrated SiGe Low Phase Noise Push

... base terminal, the active device gets instable. In order to fulfill the oscillation condition at the desired frequency f 0 = 41 GHz a capacitive loading at the emitter terminal and either a capacitive loading or an inductive loading at the collector terminal needs to be connected. The two suboscillat ...

... base terminal, the active device gets instable. In order to fulfill the oscillation condition at the desired frequency f 0 = 41 GHz a capacitive loading at the emitter terminal and either a capacitive loading or an inductive loading at the collector terminal needs to be connected. The two suboscillat ...

EH24847850

... Global clock calibration for an SAR ADC interface Shveta Sharma Abstract— This paper presents the interface circuit which incorporates the technique of analog value to digital value conversion utilising a self clocking method. The architecture consists of the Globally Asynchronous and Locally Synchr ...

... Global clock calibration for an SAR ADC interface Shveta Sharma Abstract— This paper presents the interface circuit which incorporates the technique of analog value to digital value conversion utilising a self clocking method. The architecture consists of the Globally Asynchronous and Locally Synchr ...

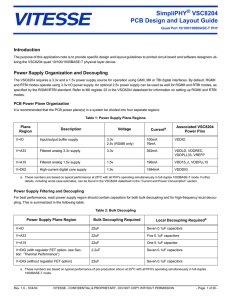

SimpliPHY VSC8204 PCB Design and Layout Guide ®

... delays for the RGMII interface without the need for PCB trace delays. These elements are enabled by writing a 1 to MII register 23, bit 8. Note that the delay for TX_CLK and RX_CLK cannot be individually enabled or disabled - they are either both enabled or both disabled. For this reason, the VSC820 ...

... delays for the RGMII interface without the need for PCB trace delays. These elements are enabled by writing a 1 to MII register 23, bit 8. Note that the delay for TX_CLK and RX_CLK cannot be individually enabled or disabled - they are either both enabled or both disabled. For this reason, the VSC820 ...

Bootstrapping a Phase Locked Loop for Better Performance

... electrical tuning of both oscillators bootstrapping their frequencies by the same amount. By bootstrapping both oscillators, the phase locked loop remains unaffected and the linear perturbance is removed. Non-linear frequency perturbations may also be compensated but the compensating signal will req ...

... electrical tuning of both oscillators bootstrapping their frequencies by the same amount. By bootstrapping both oscillators, the phase locked loop remains unaffected and the linear perturbance is removed. Non-linear frequency perturbations may also be compensated but the compensating signal will req ...

1. Safety Precautions

... objects or particles become trapped between the jaws. • Only perform measurements on conductors in which the current is flowing in only one direction. The device cannot correctly measure earth-shielded conductors or parallel conductors with current flowing in both directions. • To reduce errors, use ...

... objects or particles become trapped between the jaws. • Only perform measurements on conductors in which the current is flowing in only one direction. The device cannot correctly measure earth-shielded conductors or parallel conductors with current flowing in both directions. • To reduce errors, use ...

Low Pass Filter

... Low Pass Filter (programmable time constant) Correlated Double Sampling (programmable gain) On-Chip ADC (programmable 9 to 14 bits gray-code output) Charge ...

... Low Pass Filter (programmable time constant) Correlated Double Sampling (programmable gain) On-Chip ADC (programmable 9 to 14 bits gray-code output) Charge ...

Capacitor Start and Capacitor Start/Capacitor

... Motor hp ratings are typical. For an accurate selection procedure, measure start circuit current during a normal start or at locked rotor and select a SINPAC Switch with higher maximum current rating than that measured. 1. Be sure switch series matches motor type. 2. Be sure switch voltage rating ma ...

... Motor hp ratings are typical. For an accurate selection procedure, measure start circuit current during a normal start or at locked rotor and select a SINPAC Switch with higher maximum current rating than that measured. 1. Be sure switch series matches motor type. 2. Be sure switch voltage rating ma ...

Signal Types and Terminations

... Printed Circuit Board traces behave like transmission lines that can filter a clock signal, attenuating and distorting the clock signal as it moves along the length of the trace. Higher frequency clock signals are more susceptible to attenuation, distortion, and noise, however to improve jitter cloc ...

... Printed Circuit Board traces behave like transmission lines that can filter a clock signal, attenuating and distorting the clock signal as it moves along the length of the trace. Higher frequency clock signals are more susceptible to attenuation, distortion, and noise, however to improve jitter cloc ...

A Time-Based Energy-Efficient Analog-to-Digital Converter

... of precision. We describe a novel current-mode algorithm that also uses time to perform analog-to-digital conversion but requires 5 clock cycles to achieve bits of precision via a successive subranging technique. The algorithm requires one asynchronous comparator, two capacitors, one current source, ...

... of precision. We describe a novel current-mode algorithm that also uses time to perform analog-to-digital conversion but requires 5 clock cycles to achieve bits of precision via a successive subranging technique. The algorithm requires one asynchronous comparator, two capacitors, one current source, ...

Time-to-digital converter

In electronic instrumentation and signal processing, a time to digital converter (abbreviated TDC) is a device for recognizing events and providing a digital representation of the time they occurred. For example, a TDC might output the time of arrival for each incoming pulse. Some applications wish to measure the time interval between two events rather than some notion of an absolute time.In electronics time-to-digital converters (TDCs) or time digitizers are devices commonly used to measure a time interval and convert it into digital (binary) output. In some cases interpolating TDCs are also called time counters (TCs).TDCs are used in many different applications, where the time interval between two signal pulses (start and stop pulse) should be determined. Measurement is started and stopped, when either the rising or the falling edge of a signal pulse crosses a set threshold. These requirements are fulfilled in many physical experiments, like time-of-flight and lifetime measurements in atomic and high energy physics, experiments that involve laser ranging and electronic research involving the testing of integrated circuits and high-speed data transfer.