* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download Spike-based Winner-Take-All Computation in a Multi

Neuromuscular junction wikipedia , lookup

End-plate potential wikipedia , lookup

Artificial neural network wikipedia , lookup

Molecular neuroscience wikipedia , lookup

Neural oscillation wikipedia , lookup

Mirror neuron wikipedia , lookup

Metastability in the brain wikipedia , lookup

Optogenetics wikipedia , lookup

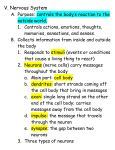

Development of the nervous system wikipedia , lookup

Holonomic brain theory wikipedia , lookup

Premovement neuronal activity wikipedia , lookup

Activity-dependent plasticity wikipedia , lookup

Neuroanatomy wikipedia , lookup

Neuropsychopharmacology wikipedia , lookup

Sparse distributed memory wikipedia , lookup

Caridoid escape reaction wikipedia , lookup

Stimulus (physiology) wikipedia , lookup

Catastrophic interference wikipedia , lookup

Single-unit recording wikipedia , lookup

Channelrhodopsin wikipedia , lookup

Neurotransmitter wikipedia , lookup

Feature detection (nervous system) wikipedia , lookup

Nonsynaptic plasticity wikipedia , lookup

Neural modeling fields wikipedia , lookup

Synaptogenesis wikipedia , lookup

Central pattern generator wikipedia , lookup

Pre-Bötzinger complex wikipedia , lookup

Recurrent neural network wikipedia , lookup

Convolutional neural network wikipedia , lookup

Chemical synapse wikipedia , lookup

Types of artificial neural networks wikipedia , lookup

Neural coding wikipedia , lookup

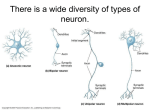

Biological neuron model wikipedia , lookup