Evaluation Board User Guide UG-176

... These evaluation boards allow users to program the ADuC7023 via the JTAG or the I2C interfaces. Users may also debug their source code through the JTAG interface. In this user guide, all references to the physical orientation of components on the boards are made with respect to a componentside view ...

... These evaluation boards allow users to program the ADuC7023 via the JTAG or the I2C interfaces. Users may also debug their source code through the JTAG interface. In this user guide, all references to the physical orientation of components on the boards are made with respect to a componentside view ...

DSD project

... MCLR to be high. After the time-out period, which is typically 18 ms, it will RESET the reset latch and thus end the on-chip RESET signal. A power-up example where MCLR is not tied to VDD is shown in Figure 5-3. VDD is allowed to rise and stabilize before bringing MCLR high. The chip will actually c ...

... MCLR to be high. After the time-out period, which is typically 18 ms, it will RESET the reset latch and thus end the on-chip RESET signal. A power-up example where MCLR is not tied to VDD is shown in Figure 5-3. VDD is allowed to rise and stabilize before bringing MCLR high. The chip will actually c ...

Configuration User Guides

... – The benefit of slave modes is that the bitstream can be stored pretty much anywhere in your hardware system – Control logic can allow for in-system delivery of FPGA design updates – Additional components will have to be purchased – Debugging your custom control circuitry can be challenging – Maste ...

... – The benefit of slave modes is that the bitstream can be stored pretty much anywhere in your hardware system – Control logic can allow for in-system delivery of FPGA design updates – Additional components will have to be purchased – Debugging your custom control circuitry can be challenging – Maste ...

a Engineer-to-Engineer Note EE-179

... they are programmed. During this time, some FPGAs and/or ASICs typically turn on an internal pull-up or pulldown resistor. These resistors are used to keep signals from floating to mid-scale before programming. It is important to make sure that the FPGA or ASIC which connects to Link Port 1, 2, or 3 ...

... they are programmed. During this time, some FPGAs and/or ASICs typically turn on an internal pull-up or pulldown resistor. These resistors are used to keep signals from floating to mid-scale before programming. It is important to make sure that the FPGA or ASIC which connects to Link Port 1, 2, or 3 ...

Unit 3

... The ID 28-00000478d75e is an example. You might also want to try different devices, like the similar DS18S20. The Raspberry Pi does not have any ADC (analogue to digital converter) pins in its GPIO, and so a digital temperature sensor should be used. DS18B20: relatively cheap, very easy to find, eas ...

... The ID 28-00000478d75e is an example. You might also want to try different devices, like the similar DS18S20. The Raspberry Pi does not have any ADC (analogue to digital converter) pins in its GPIO, and so a digital temperature sensor should be used. DS18B20: relatively cheap, very easy to find, eas ...

SPC560B4x/5x, SPC560C4x/5x, SPC560B54/6x, SPC560D30/40

... System reset and low power circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Noise filtering on reset signal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Reference reset circuit . . . . . . . . . . . . . ...

... System reset and low power circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Noise filtering on reset signal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Reference reset circuit . . . . . . . . . . . . . ...

Errata - Silicon Labs

... The conversion done (CD) PRS outputs from the DAC are tied to the interrupt flags. As long as the interrupt flag is set, no PRS output will be generated. When the first conversion done (CD) event occurs, the VDAC will set the interrupt flag and generate one PRS pulse. As long as the interrupt flag i ...

... The conversion done (CD) PRS outputs from the DAC are tied to the interrupt flags. As long as the interrupt flag is set, no PRS output will be generated. When the first conversion done (CD) event occurs, the VDAC will set the interrupt flag and generate one PRS pulse. As long as the interrupt flag i ...

Platform Cable USB II Data Sheet (DS593)

... embedded software and firmware when used with applications such as Xilinx's Embedded Development Kit and ChipScope Pro Analyzer. Platform Cable USB II is an upgrade to and replaces Platform Cable USB. Similar to its popular predecessor, Platform Cable USB II is intended for prototyping environments ...

... embedded software and firmware when used with applications such as Xilinx's Embedded Development Kit and ChipScope Pro Analyzer. Platform Cable USB II is an upgrade to and replaces Platform Cable USB. Similar to its popular predecessor, Platform Cable USB II is intended for prototyping environments ...

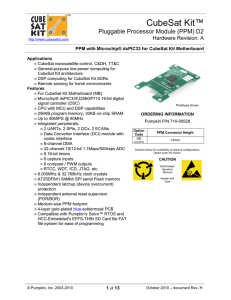

D2 - CubeSat Kit

... via the CubeSat Kit Bus connector. Those signals that are connected directly to the PPM connector and to the CubeSat Kit Bus connectors ...

... via the CubeSat Kit Bus connector. Those signals that are connected directly to the PPM connector and to the CubeSat Kit Bus connectors ...

femcontrol

... SG923-0010 Is an evaluation Kit used to simplify the rapid evaluation and software integration of the SG901-1091 Radio Module. The EVK allows for easy access to the SDIO interface via a standard SDIO hardware connector The SDIO connector is designed to plug into processor development boards for rapi ...

... SG923-0010 Is an evaluation Kit used to simplify the rapid evaluation and software integration of the SG901-1091 Radio Module. The EVK allows for easy access to the SDIO interface via a standard SDIO hardware connector The SDIO connector is designed to plug into processor development boards for rapi ...

USB-KW2X Hardware Reference Manual Document Number: USB-KW2XHWRM Rev. 0.1

... Freescale reserves the right to make changes without further notice to any products herein. Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of ...

... Freescale reserves the right to make changes without further notice to any products herein. Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of ...

- Digilent Inc.

... Figure 12 above shows the different options available for configuring the FPGA. An on-board "mode" jumper (JP1) selects between the two programming modes. The FPGA configuration data is stored in files called bitstreams that have the .bit file extension. The ISE or Vivado software from Xilinx can cr ...

... Figure 12 above shows the different options available for configuring the FPGA. An on-board "mode" jumper (JP1) selects between the two programming modes. The FPGA configuration data is stored in files called bitstreams that have the .bit file extension. The ISE or Vivado software from Xilinx can cr ...

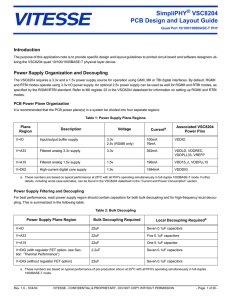

SimpliPHY VSC8204 PCB Design and Layout Guide ®

... The VSC8204 contains an internal delay element connected to each TX_CLK and RX_CLK pin, which can provide the necessary clock delays for the RGMII interface without the need for PCB trace delays. These elements are enabled by writing a 1 to MII register 23, bit 8. Note that the delay for TX_CLK and ...

... The VSC8204 contains an internal delay element connected to each TX_CLK and RX_CLK pin, which can provide the necessary clock delays for the RGMII interface without the need for PCB trace delays. These elements are enabled by writing a 1 to MII register 23, bit 8. Note that the delay for TX_CLK and ...

Flight Computer Carrier Board Capstone

... The MPC5200 provides the user an IEEE 1149.1 JTAG interface to facilitate board/system testing. It also provides a Common On-Chip Processor (COP) Interface, which shares the IEEE 1149.1 JTAG port. The COP Interface provides access to the MPC5200's imbedded Freescale MPC603e G2_LE processor. This int ...

... The MPC5200 provides the user an IEEE 1149.1 JTAG interface to facilitate board/system testing. It also provides a Common On-Chip Processor (COP) Interface, which shares the IEEE 1149.1 JTAG port. The COP Interface provides access to the MPC5200's imbedded Freescale MPC603e G2_LE processor. This int ...

user options

... The target MCU features an on-board USB On-the-Go (OTG) physical layer (Phy). The OTG Phy may be configured for either Host or Peripheral mode depending on the target application. The OTG protocol also allows mode switching under software control. Access to the OTG Phy is gained through the mini-AB ...

... The target MCU features an on-board USB On-the-Go (OTG) physical layer (Phy). The OTG Phy may be configured for either Host or Peripheral mode depending on the target application. The OTG protocol also allows mode switching under software control. Access to the OTG Phy is gained through the mini-AB ...

MAX V Schematic Review Worksheet

... Guidelines (PDF) version 1.0 and other referenced literature for this device family. The technical content is divided into focus areas such as FPGA power supplies, programming, and dual purpose I/O pins. Within each focus area, there is a table that contains the voltage or pin name for all of the de ...

... Guidelines (PDF) version 1.0 and other referenced literature for this device family. The technical content is divided into focus areas such as FPGA power supplies, programming, and dual purpose I/O pins. Within each focus area, there is a table that contains the voltage or pin name for all of the de ...

www.BDTIC.com/Freescale/ A Little 8-bit Goes a Long Way

... frequency range without the limitations of traditional emulators. Includes on-chip trigger and trace capability, effectively replacing expensive emulators with a cost-effective serial real-time emulation and debug cable. • Includes nine flexible triggers and buffer hardware to replace an emulator ...

... frequency range without the limitations of traditional emulators. Includes on-chip trigger and trace capability, effectively replacing expensive emulators with a cost-effective serial real-time emulation and debug cable. • Includes nine flexible triggers and buffer hardware to replace an emulator ...

Folie 1 - Indico

... The activating of blind phase is initiated by the combination CLK or StrClr at the negative edge StrGate that in normal operation does not occur. This signal sequence can be produced without influencing of SWITCHER outputs in any moment (cycle) The switching of segments one after another is realized ...

... The activating of blind phase is initiated by the combination CLK or StrClr at the negative edge StrGate that in normal operation does not occur. This signal sequence can be produced without influencing of SWITCHER outputs in any moment (cycle) The switching of segments one after another is realized ...

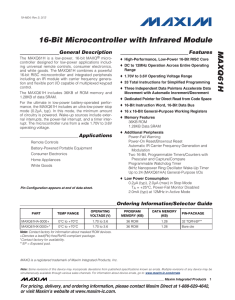

MAXQ61H 16-Bit Microcontroller with Infrared Module General Description Features

... Note 3: The power-fail reset and power-on-reset (POR) detectors operate in tandem to ensure that one or both signals are active at all times when VDD < VRST. Doing so ensures the device maintains the reset state until the minimum operating voltage is achieved. Note 4: Guaranteed by design and not pr ...

... Note 3: The power-fail reset and power-on-reset (POR) detectors operate in tandem to ensure that one or both signals are active at all times when VDD < VRST. Doing so ensures the device maintains the reset state until the minimum operating voltage is achieved. Note 4: Guaranteed by design and not pr ...

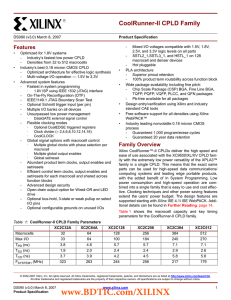

Features

... XC2C32 and XC2C64 devices are not banked, but the new XC2C32A and XC2C64A devices have two banks. The medium parts (128 and 256 macrocell) support two output banks. With two, the outputs will switch to one of two selected output voltage levels, unless both banks are set to the same voltage. The larg ...

... XC2C32 and XC2C64 devices are not banked, but the new XC2C32A and XC2C64A devices have two banks. The medium parts (128 and 256 macrocell) support two output banks. With two, the outputs will switch to one of two selected output voltage levels, unless both banks are set to the same voltage. The larg ...

AT91SAM7L128数据手册DataSheet 下载

... based on the 32-bit ARM7™ RISC processor and high-speed Flash memory. • AT91SAM7L128 features a 128 Kbyte high-speed Flash and a total of 6 Kbytes SRAM. • AT91SAM7L64 features a 64 Kbyte high-speed Flash and a total of 6 Kbytes SRAM. They also embed a large set of peripherals, including a Segment LC ...

... based on the 32-bit ARM7™ RISC processor and high-speed Flash memory. • AT91SAM7L128 features a 128 Kbyte high-speed Flash and a total of 6 Kbytes SRAM. • AT91SAM7L64 features a 64 Kbyte high-speed Flash and a total of 6 Kbytes SRAM. They also embed a large set of peripherals, including a Segment LC ...

Secure Authentication Starter Kit Evaluates: DS28E01/DS28CN01/DS2460 General Description Features

... 1-WireM and I2C-based SHA-1 slave ICs. Multiple options are supported for host SHA-1 computation development including fixed function processing with the Maxim DS2460, microcontroller(FC)-based with a Microchip PIC18F4550, and a Maxim-developed SHA-1 Verilog implementation (DSSHA1) used in conjuncti ...

... 1-WireM and I2C-based SHA-1 slave ICs. Multiple options are supported for host SHA-1 computation development including fixed function processing with the Maxim DS2460, microcontroller(FC)-based with a Microchip PIC18F4550, and a Maxim-developed SHA-1 Verilog implementation (DSSHA1) used in conjuncti ...

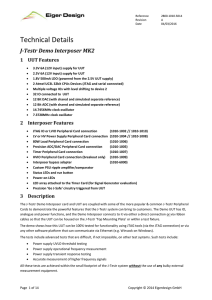

File - J

... Test code is provided for the XJTAG XJEASE software, and also for ATEASY, but other JTAG or test SW platforms (such as JTAG Technologies, Goepel, Labview, Python, etc.) can also be used. No other supplementary programs are usually ...

... Test code is provided for the XJTAG XJEASE software, and also for ATEASY, but other JTAG or test SW platforms (such as JTAG Technologies, Goepel, Labview, Python, etc.) can also be used. No other supplementary programs are usually ...

Reset Generation for TI DSP Processor WP

... Figure 2 - Reset generation for a TMS320 processor using ProcessorPM The ProcessorPM device is a low-cost, 6-supply voltage monitoring device with two digital inputs and five digital I/O pins. The logic to control the output pins is implemented in the on-chip 16-macrocell PLD. The ProcessorPM device ...

... Figure 2 - Reset generation for a TMS320 processor using ProcessorPM The ProcessorPM device is a low-cost, 6-supply voltage monitoring device with two digital inputs and five digital I/O pins. The logic to control the output pins is implemented in the on-chip 16-macrocell PLD. The ProcessorPM device ...