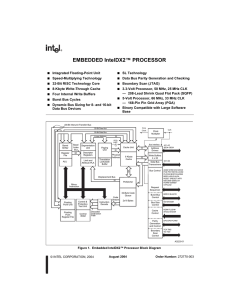

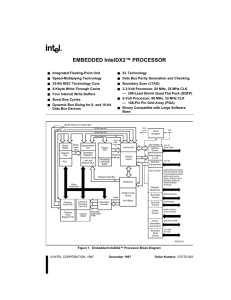

EMBEDDED IntelDX2™ PROCESSOR

... implementation conforms with the IEEE Standard Test Access Port and Boundary Scan Architecture. Intel’s SL technology provides these features: • Intel System Management Mode (SMM) — A unique Intel architecture operating mode provides a dedicated special purpose interrupt and address space that can b ...

... implementation conforms with the IEEE Standard Test Access Port and Boundary Scan Architecture. Intel’s SL technology provides these features: • Intel System Management Mode (SMM) — A unique Intel architecture operating mode provides a dedicated special purpose interrupt and address space that can b ...

EMBEDDED IntelDX2™ PROCESSOR

... stopped, causing the processor to enter the Auto HALT Power Down state (20–45 mA typical, depending on input clock frequency). ...

... stopped, causing the processor to enter the Auto HALT Power Down state (20–45 mA typical, depending on input clock frequency). ...

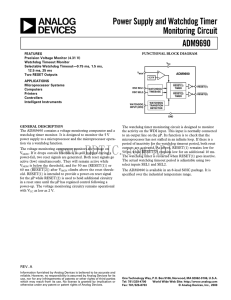

ADM9690 数据手册DataSheet 下载

... The watchdog timer circuit monitors the activity of the microprocessor in order to check that it is not stalled in an infinite loop. An output line on the processor may be used to toggle the Watchdog Input (WDI) line. If this line is not toggled within the selected timeout period, both RESET outputs ...

... The watchdog timer circuit monitors the activity of the microprocessor in order to check that it is not stalled in an infinite loop. An output line on the processor may be used to toggle the Watchdog Input (WDI) line. If this line is not toggled within the selected timeout period, both RESET outputs ...

AN 738: Intel® Arria® 10 Device Design Guidelines

... blocks. Larger densities and package pin counts offer more full-duplex LVDS channels for different signaling; ensure that your device density-package combination includes enough LVDS channels. Other factors can also affect the number of I/O pins required for a design, including simultaneous switchin ...

... blocks. Larger densities and package pin counts offer more full-duplex LVDS channels for different signaling; ensure that your device density-package combination includes enough LVDS channels. Other factors can also affect the number of I/O pins required for a design, including simultaneous switchin ...

MC56F8323MFBE - Freescale Semiconductor, Inc.

... synchronous pulse width control (0% to 100% modulation) is supported. The device is capable of controlling most motor types: ACIM (AC Induction Motors); both BDC and BLDC (Brush and Brushless DC motors); SRM and VRM (Switched and Variable Reluctance Motors); and stepper motors. The PWM incorporates ...

... synchronous pulse width control (0% to 100% modulation) is supported. The device is capable of controlling most motor types: ACIM (AC Induction Motors); both BDC and BLDC (Brush and Brushless DC motors); SRM and VRM (Switched and Variable Reluctance Motors); and stepper motors. The PWM incorporates ...

MC56F8323VFBE 数据手册 DataSheet 下载

... synchronous pulse width control (0% to 100% modulation) is supported. The device is capable of controlling most motor types: ACIM (AC Induction Motors); both BDC and BLDC (Brush and Brushless DC motors); SRM and VRM (Switched and Variable Reluctance Motors); and stepper motors. The PWM incorporates ...

... synchronous pulse width control (0% to 100% modulation) is supported. The device is capable of controlling most motor types: ACIM (AC Induction Motors); both BDC and BLDC (Brush and Brushless DC motors); SRM and VRM (Switched and Variable Reluctance Motors); and stepper motors. The PWM incorporates ...

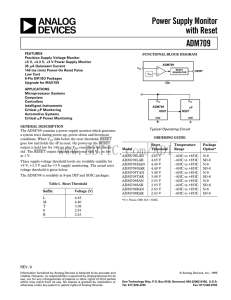

ADM709 数据手册DataSheet 下载

... operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum ratings for extended periods of time may affect device reliability. ...

... operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum ratings for extended periods of time may affect device reliability. ...

Using SPI Flash with 7 Series FPGAs Application Note

... UG470, 7 Series FPGAs Configuration User Guide for details. If the design requires multiple bitstreams, multiply the size of the bitstream accordingly. The Xilinx tools allow bitstream compression, however it is not recommended to rely on compression when determining SPI flash size because compressi ...

... UG470, 7 Series FPGAs Configuration User Guide for details. If the design requires multiple bitstreams, multiply the size of the bitstream accordingly. The Xilinx tools allow bitstream compression, however it is not recommended to rely on compression when determining SPI flash size because compressi ...

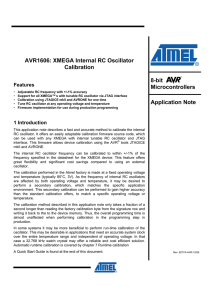

AVR1606: XMEGA Internal RC Oscillator Calibration

... The programmer can use 5120 C-cycles (cycles on the C-clock) as time-out period, as the calibration routine is guaranteed to be completed within this number of Ccycles. The calibration procedure runs through the following steps: 1. The programmer writes the calibration firmware into the device and p ...

... The programmer can use 5120 C-cycles (cycles on the C-clock) as time-out period, as the calibration routine is guaranteed to be completed within this number of Ccycles. The calibration procedure runs through the following steps: 1. The programmer writes the calibration firmware into the device and p ...

MC68HC705 microcontroller

... documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to: http://www.motorola.com/semiconductors/ The following revision history table summarizes changes contained in this document. For your ...

... documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to: http://www.motorola.com/semiconductors/ The following revision history table summarizes changes contained in this document. For your ...

MAX6340UK16-T中文资料

... perform a single function:?Capacitor-Adjustable Reset Timeout Periodthey assert a reset signal whenever the VCCsupply volt-age falls below its reset threshold. The reset output?Low Quiescent Current (1.6?A typ)remains asserted for the reset timeout period after V?Three RESET Output Options ...

... perform a single function:?Capacitor-Adjustable Reset Timeout Periodthey assert a reset signal whenever the VCCsupply volt-age falls below its reset threshold. The reset output?Low Quiescent Current (1.6?A typ)remains asserted for the reset timeout period after V?Three RESET Output Options ...

datasheet - GES Electronics

... power-on reset to the device internal circuitry on power up. An additional RESET# input and RSTOUT# output are provided to allow other devices to reset the FT232BL or the FT232BL to reset other devices respectively. During reset, RSTOUT# is driven low, otherwise it drives out at the 3.3V provided by ...

... power-on reset to the device internal circuitry on power up. An additional RESET# input and RSTOUT# output are provided to allow other devices to reset the FT232BL or the FT232BL to reset other devices respectively. During reset, RSTOUT# is driven low, otherwise it drives out at the 3.3V provided by ...

AN1790

... MR and VSS (ground), as shown in Figure 3. The Manual Reset has an internal 20 kΩ pull-up resistor and a debounce circuit, which solves the problem of any noise generated by switching the push-button. The timing diagram represented in Figure 4 shows how the Manual Reset input functions. When MR is d ...

... MR and VSS (ground), as shown in Figure 3. The Manual Reset has an internal 20 kΩ pull-up resistor and a debounce circuit, which solves the problem of any noise generated by switching the push-button. The timing diagram represented in Figure 4 shows how the Manual Reset input functions. When MR is d ...

UM0772

... Hardware layout: top view . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Hardware layout: bottom view . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 S-Touch™ resistive touchscreen demonstration (S ...

... Hardware layout: top view . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Hardware layout: bottom view . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 S-Touch™ resistive touchscreen demonstration (S ...

MAX3421E USB Peripheral/Host Controller with SPI Interface General Description

... DSP when it operates as a USB host. For point-to-point solutions, for example, a USB keyboard or mouse interfaced to an embedded system, the firmware that operates the MAX3421E can be simple since only a targeted device is supported. Internal level translators allow the SPI interface to run at a sys ...

... DSP when it operates as a USB host. For point-to-point solutions, for example, a USB keyboard or mouse interfaced to an embedded system, the firmware that operates the MAX3421E can be simple since only a targeted device is supported. Internal level translators allow the SPI interface to run at a sys ...

Low Power Consumption (cont.)

... When the voltage monitoring 1 interrupt/reset enable bit (LVD1RIE) is set to 1 (enabling generation of a reset or interrupt by the voltage detection circuit) and the voltage monitoring 1 circuit mode select bit (LVD1RI) is set to 1 (selecting generation of a reset in response to detection of a low v ...

... When the voltage monitoring 1 interrupt/reset enable bit (LVD1RIE) is set to 1 (enabling generation of a reset or interrupt by the voltage detection circuit) and the voltage monitoring 1 circuit mode select bit (LVD1RI) is set to 1 (selecting generation of a reset in response to detection of a low v ...

FT245BM Data Sheet

... on the FT245BM device. They have been replaced with the new SI / WU and PWREN# signals ...

... on the FT245BM device. They have been replaced with the new SI / WU and PWREN# signals ...

MAX 10 FPGA (10M0S, 144-EQFP) Evaluaion Kit User Guide

... The Quartus II Convert Programming File (CPF) GUI can be used to generate a .pof file that can use for internal configuration. You can directly program the MAX 10 device’s flash which included Configuration Flash Memory (CFM) and User Flash Memory (UFM) by using a download cable with the Quartus II ...

... The Quartus II Convert Programming File (CPF) GUI can be used to generate a .pof file that can use for internal configuration. You can directly program the MAX 10 device’s flash which included Configuration Flash Memory (CFM) and User Flash Memory (UFM) by using a download cable with the Quartus II ...

KX-TG4012LAT KX-TG4013LAT KX-TGA403LAT

... 2. Replace only with the same or equivalent type recommended by the manufacturer. 3. Dispose of used batteries according to the manufacturer’s Instructions. ...

... 2. Replace only with the same or equivalent type recommended by the manufacturer. 3. Dispose of used batteries according to the manufacturer’s Instructions. ...

AN3261

... with user-adjustable setup delays Introduction The Smart Reset™ family of devices consists of several products with a combination of features selected to best suit most typical applications. Their basic common feature is dualbutton reset with setup delay that requires both input reset buttons to be ...

... with user-adjustable setup delays Introduction The Smart Reset™ family of devices consists of several products with a combination of features selected to best suit most typical applications. Their basic common feature is dualbutton reset with setup delay that requires both input reset buttons to be ...

fr, mb91460, reset - Cypress Semiconductor

... Synchronous RST reset operation refers to the mode when the device does not go to the operation reset (RST) state after an operation reset (RST) request until all bus access has halted. In synchronous RST reset mode, the device does not go to the RST reset state when a RST reset request is received ...

... Synchronous RST reset operation refers to the mode when the device does not go to the operation reset (RST) state after an operation reset (RST) request until all bus access has halted. In synchronous RST reset mode, the device does not go to the RST reset state when a RST reset request is received ...

88AP510 Hardware Specifications

... • Included PEX_ISET as one of the PCIe signals that can be left unconnected.

• Deleted a portion of the VGA port description. It is not required to tie VGA_EXT_CLK to ground.

5. Added Table 36, Supported Clock Combinations, on page 70.

6. In the attached reset strapping Excel file in Section 7.5, ...

... • Included PEX

Calculating the Capacitor of the Reset Input

... the reset. Indeed, normally the input is considered to be low when its level reaches Vil1. But in reality the trigger is somewhere between Vih1 and Vil1. So, the worst case condition is considered at the Vih1 level. When the reset is released, the program execution starts and the ALE signal toggles ...

... the reset. Indeed, normally the input is considered to be low when its level reaches Vil1. But in reality the trigger is somewhere between Vih1 and Vil1. So, the worst case condition is considered at the Vih1 level. When the reset is released, the program execution starts and the ALE signal toggles ...