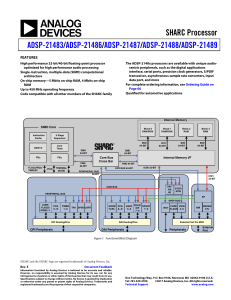

ADSP-2148x - Analog Devices

... The diagram on Page 1 shows the two clock domains that make up the ADSP-2148x processors. The core clock domain contains the following features: • Two processing elements (PEx, PEy), each of which comprises an ALU, multiplier, shifter, and data register file • Data address generators (DAG1, DAG2) • ...

... The diagram on Page 1 shows the two clock domains that make up the ADSP-2148x processors. The core clock domain contains the following features: • Two processing elements (PEx, PEy), each of which comprises an ALU, multiplier, shifter, and data register file • Data address generators (DAG1, DAG2) • ...

using the acom2 adapter with motorola microcontrollers in

... The monitor is designed to accept simple commands from a computer terminal or other communication device. Functions include reading and writing the computers memory plus other rudamentary functions such as uploading and running a test program. The 68HC08/908 family of microcontrollers include a moni ...

... The monitor is designed to accept simple commands from a computer terminal or other communication device. Functions include reading and writing the computers memory plus other rudamentary functions such as uploading and running a test program. The 68HC08/908 family of microcontrollers include a moni ...

CY7C63413C, CY7C63513C, CY7C63613C Low

... cause a DAC interrupt. The GPIO ports also have a level of masking to select which GPIO inputs can cause a GPIO interrupt. For additional flexibility, the input transition polarity that causes an interrupt is programmable for each pin of the DAC port. Input transition polarity can be programmed for ...

... cause a DAC interrupt. The GPIO ports also have a level of masking to select which GPIO inputs can cause a GPIO interrupt. For additional flexibility, the input transition polarity that causes an interrupt is programmable for each pin of the DAC port. Input transition polarity can be programmed for ...

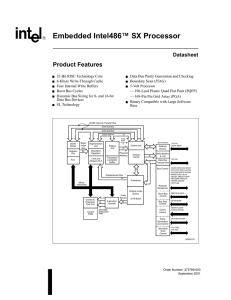

Embedded Intel486™ SX Processor

... code and data. Its data bus can operate in burst mode which provides up to 106-Mbyte-per-second transfers for cache-line fills and instruction prefetches. Intel’s SL technology is incorporated in the embedded Intel486 SX processor. Utilizing Intel’s System Management Mode (SMM), it enables designers ...

... code and data. Its data bus can operate in burst mode which provides up to 106-Mbyte-per-second transfers for cache-line fills and instruction prefetches. Intel’s SL technology is incorporated in the embedded Intel486 SX processor. Utilizing Intel’s System Management Mode (SMM), it enables designers ...

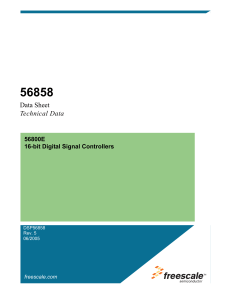

DSP56858.pdf

... The 56800E core is based on a Harvard-style architecture consisting of three execution units operating in parallel, allowing as many as six operations per instruction cycle. The microprocessor-style programming model and optimized instruction set allow straightforward generation of efficient, compac ...

... The 56800E core is based on a Harvard-style architecture consisting of three execution units operating in parallel, allowing as many as six operations per instruction cycle. The microprocessor-style programming model and optimized instruction set allow straightforward generation of efficient, compac ...

Manual - UNICORN

... In order to cope with the challenges of the heating issues and demand of much more diminutive embedded system in diverse application, ENDAT-3203M/3220M system board provides the ultimate solution by integrating with VIA’s technology low power consumption VIA C3 series CPU and VIA EDEN fanless ESP se ...

... In order to cope with the challenges of the heating issues and demand of much more diminutive embedded system in diverse application, ENDAT-3203M/3220M system board provides the ultimate solution by integrating with VIA’s technology low power consumption VIA C3 series CPU and VIA EDEN fanless ESP se ...

ScanTAP IsoPod User`s Manual

... NOTE: Use of the ScanTAP IsoPod does not guarantee that damage will not occur to hardware that is subjected to extreme conditions. Damage may still be possible under certain circumstances that are beyond the scope of what is generally accepted as “normal operation”. ...

... NOTE: Use of the ScanTAP IsoPod does not guarantee that damage will not occur to hardware that is subjected to extreme conditions. Damage may still be possible under certain circumstances that are beyond the scope of what is generally accepted as “normal operation”. ...

1322x Sensor Node - NXP Semiconductors

... hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document. Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee ...

... hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document. Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee ...

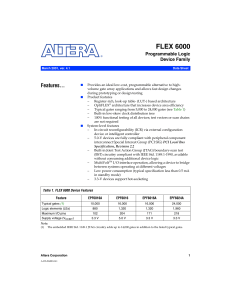

FLEX 6000 Programmable Logic Device Family Data Sheet

... a16450 universal asynchronous receiver/transmitter (UART) ...

... a16450 universal asynchronous receiver/transmitter (UART) ...

AT88Microbase Hardware User Guide

... When the JTAGEN fuse is disabled, the four TAP pins are normal port pins, and the TAP controller is in reset. When the JTAGEN fuse is enabled, the input TAP signals are internally pulled high. This enables the JTAG for boundary-scan and programming. The Atmel AT90USB1287 device is shipped with this ...

... When the JTAGEN fuse is disabled, the four TAP pins are normal port pins, and the TAP controller is in reset. When the JTAGEN fuse is enabled, the input TAP signals are internally pulled high. This enables the JTAG for boundary-scan and programming. The Atmel AT90USB1287 device is shipped with this ...

AVR1005: Getting started with XMEGA

... The AVR® product portfolio has been expanded with the XMEGA family. Many ask if this is a new architecture and are uncertain how their experience with megaAVR transfers to AVR XMEGA. This document briefly introduces the similarities and differences between the two AVR families, and provides an overv ...

... The AVR® product portfolio has been expanded with the XMEGA family. Many ask if this is a new architecture and are uncertain how their experience with megaAVR transfers to AVR XMEGA. This document briefly introduces the similarities and differences between the two AVR families, and provides an overv ...

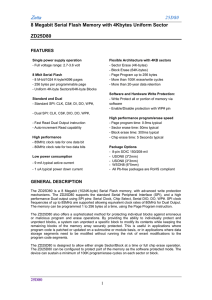

25D80 8 Megabit Serial Flash Memory with 4Kbytes Uniform Sector

... allows up to 256 bytes to be programmed at a time (changing bits from 1 to 0), provided that they lie in consecutive addresses on the same page of memory. Sector Erase, Block Erase and Chip Erase The Page Program (PP) instruction allows bits to be reset from 1 to 0. Before this can be applied, the b ...

... allows up to 256 bytes to be programmed at a time (changing bits from 1 to 0), provided that they lie in consecutive addresses on the same page of memory. Sector Erase, Block Erase and Chip Erase The Page Program (PP) instruction allows bits to be reset from 1 to 0. Before this can be applied, the b ...

USB3290 Small Footprint Hi-Speed USB 2.0 Device PHY with UTMI

... the USB3290 ideal for portable consumer electronics applications. ...

... the USB3290 ideal for portable consumer electronics applications. ...

AM335x Sitara™ Processors Silicon Revisions

... minus (DM) data signals to be swapped. This feature was added to simplify PCB layout. In some cases, the DP and DM data signals may need to cross over each other to connect to the respective USB connector pins. Crossing these signals on the PCB may cause signal integrity issues if not implemented pr ...

... minus (DM) data signals to be swapped. This feature was added to simplify PCB layout. In some cases, the DP and DM data signals may need to cross over each other to connect to the respective USB connector pins. Crossing these signals on the PCB may cause signal integrity issues if not implemented pr ...

430 Day 2006

... There are three methods of programming Flash; Out or in-system using JTAG, a Bootstrap Loader (BSL), or in-system using normal software. The bootstrap loader is a section of ROM code that resides on the device itself and allows communication using a common 9600-baud UART protocol. The sequence to se ...

... There are three methods of programming Flash; Out or in-system using JTAG, a Bootstrap Loader (BSL), or in-system using normal software. The bootstrap loader is a section of ROM code that resides on the device itself and allows communication using a common 9600-baud UART protocol. The sequence to se ...

Hardware Development Guide for i.MX 6QuadPlus, 6Quad

... products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP ...

... products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP ...

Table of Contents - Embedded Artists AB

... Due to the nature of the LPC4357 Developers Kit – an evaluation board not for integration into an endproduct – fast transient immunity tests and conducted radio-frequency immunity tests have not been executed. Externally connected cables are assumed to be less than 3 meters. The general expansion co ...

... Due to the nature of the LPC4357 Developers Kit – an evaluation board not for integration into an endproduct – fast transient immunity tests and conducted radio-frequency immunity tests have not been executed. Externally connected cables are assumed to be less than 3 meters. The general expansion co ...

Digilab XL Users Manual 1/14 Overview This document presents all

... All parallel port signals except pin 15 (SPP Error), pin 12 (SPP paper out), and pin 13 (SPP Select) are routed. Although the signal names reflect the Enhanced Parallel Port (EPP) mode, any protocol can be used for data transfer. Note that the full ECP protocol (including pin15) can be used if DB25 ...

... All parallel port signals except pin 15 (SPP Error), pin 12 (SPP paper out), and pin 13 (SPP Select) are routed. Although the signal names reflect the Enhanced Parallel Port (EPP) mode, any protocol can be used for data transfer. Note that the full ECP protocol (including pin15) can be used if DB25 ...

Emulation and Trace Headers Technical

... data. On a trace-capable device, the trace interface is one of the highest performance interfaces. Although only used during design, development, and debug, the trace interface must be implemented correctly for full functionality and performance. ...

... data. On a trace-capable device, the trace interface is one of the highest performance interfaces. Although only used during design, development, and debug, the trace interface must be implemented correctly for full functionality and performance. ...

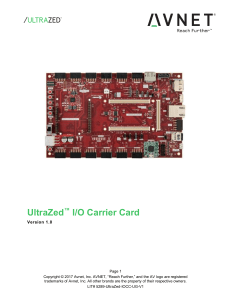

UltraZed I/O Carrier Card

... Input / Output Carrier Card. The SOM attaches to this carrier card (board) for user evaluation. The IOCC features proven high speed interfaces to the SOM as well as the necessary power, control and clocks required for the SOM to operate. ...

... Input / Output Carrier Card. The SOM attaches to this carrier card (board) for user evaluation. The IOCC features proven high speed interfaces to the SOM as well as the necessary power, control and clocks required for the SOM to operate. ...

LAPP IPMC Mezzanine LAPP Intelligent Platform Management Controller Mezzanine Version V1.5

... JTAG master, for motherboard firmware upgrade for example User configuration (with USR pin) through Ethernet Mezzanine firmware upgrade: As there is no standard for IPMC firmware upgrade, for the moment the Ethernet connection is the only way to upgrade the mezzanine firmware. ...

... JTAG master, for motherboard firmware upgrade for example User configuration (with USR pin) through Ethernet Mezzanine firmware upgrade: As there is no standard for IPMC firmware upgrade, for the moment the Ethernet connection is the only way to upgrade the mezzanine firmware. ...

Catalog Section

... circuit indicators to quickly and easily locate faulted sections of overhead systems. This faulted circuit indicator (FCI) is designed for use on overhead bare conductors. A long-life lithium battery provides power to indicate the faulted conditions using two highly visible LED indicators. The unit ...

... circuit indicators to quickly and easily locate faulted sections of overhead systems. This faulted circuit indicator (FCI) is designed for use on overhead bare conductors. A long-life lithium battery provides power to indicate the faulted conditions using two highly visible LED indicators. The unit ...

ChipKIT Pro MX7 Board Reference Manual Table of Contents

... The ChipKIT Pro MX7 is rated for external power from 3.6 to 5.5 volts DC. Using a voltage outside this range will damage the board and connected devices. For most purposes when using external power, a regulated 5V supply should be used. If the board is operated from an external supply with a voltage ...

... The ChipKIT Pro MX7 is rated for external power from 3.6 to 5.5 volts DC. Using a voltage outside this range will damage the board and connected devices. For most purposes when using external power, a regulated 5V supply should be used. If the board is operated from an external supply with a voltage ...

Test and Debug in Deep-Submicron Technologies

... to market. Debug of a chip requires analysis of both its internal and external behavior under known stimuli. Faulty behavior and possible design errors can be located by repeatedly performing this analysis and comparing responses obtained with a set of expected responses. These results can assist in ...

... to market. Debug of a chip requires analysis of both its internal and external behavior under known stimuli. Faulty behavior and possible design errors can be located by repeatedly performing this analysis and comparing responses obtained with a set of expected responses. These results can assist in ...