* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download R 1 - Lyle School of Engineering

Pulse-width modulation wikipedia , lookup

Power inverter wikipedia , lookup

Flip-flop (electronics) wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Buck converter wikipedia , lookup

Control system wikipedia , lookup

Power electronics wikipedia , lookup

Two-port network wikipedia , lookup

Semiconductor device wikipedia , lookup

Schmitt trigger wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Integrated circuit wikipedia , lookup

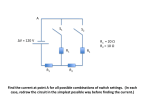

Digital Logic Circuits: A Brief Introduction (with Appendix p.25-33) EETS8304/TC715-N SMU/NTU Lecture Scheduled Feb. 3, 2004 Digital Logic Devices (print slides only, no notes pages) Page 1 ©1997-2004 R.Levine Digital Hardware • Exploits non-linear properties of electronic devices – Electro-mechanical relays, vacuum tubes were used in the past – Electronic, Dielectric and Magnetic devices were also used historically – Semiconductor electronic devices used primarily today due to high component density, rapid operation, and low cost of integrated circuits Page 2 ©1997-2004 R.Levine Semiconductor Devices – Diodes – Transistors • Junction • Field Effect (and Metal Oxide Silicon--MOS) – Advantages: • Small size – small, high-functionality in integrated circuit package • High reliability – failure mechanisms studied, understood, and avoided • Fast switching operation – but faster switching requires higher power! • Low power consumption vis-à-vis prior art – No heated filament, as in vacuum tubes • Low cost of major raw materials – Silicon is readily available everywhere, some dopant elements are scarce but are used in very small quantities Page 3 ©1997-2004 R.Levine Linear Electric Circuit vout = (R2•R3) •v1 + (R1•R3) •v2 R1•R2 + R2•R3 + R1•R3 R1 v1 R2 v2 R3 vout vout = (2) •v1 + (2) •v2 4 + 2 +2 Page 4 ©1997-2004 R.Levine Non-linear Electric Circuit Analysis using piece-wise linear model of diode, illustrated on voltage-current graph vout Ideal voltmeter reading: 0 volts vout v1 Ideal, vout=v1 10 V 9.37 V 10 V Actual reading: -10µA•10k= -0.1 V, due to non-zero reverse current in diode. Page 5 ©1997-2004 R.Levine v1 One Stage Electronic Amplifiers • Various different graphic symbols are used to represent the amplifier “ground return circuit” for +5 V power supply is customarily omitted on drawings. vout 6 Cutoff region 4 approximately linear amplification region of operation. Note negative slope. vout 2 vin -2 Page 6 ©1997-2004 R.Levine -1 0 Vin =0.2 V is -2 “edge” of cutoff -4 1 2 vin Saturation region Vin =0.9 V is “edge” of saturation Amplifier Distinctions I • Applications which use the approximately linear region: – Hi-fidelity audio amplifiers – Radio frequency amplifiers (some types) – Analog amplifiers in telephone transmission • First used in early 20th century with vacuum tubes • Linear region is not quite as linear as is needed for a chain of numerous amplifier stages – Cumulative distortion (“flattening” of the peaks of the waveform) occurred in long distance analog telephone conversations • Negative feedback (invented by H.S. Black of Bell Laboratories, ca. 1927) improves linearity, reduces internal noise generation Page 7 ©1997-2004 R.Levine Amplifier Distinctions II • Non-linear applications intentionally use primarily the cutoff and saturation regions – Minimal power dissipated in these regions • power (watts) is product of voltage with current Power P= v•i • In these operating regions, either v or I is low – therefore low power dissipated in transistor – design objective is typically to switch through the linear region as rapidly as possible to minimize power consumption – Certain types of amplifiers (so-called Class C and D, etc.) use non-linear properties for special applications (not described in this course) Page 8 ©1997-2004 R.Levine Digital Logic is the Main Non-Linear Application • Technology and design knowledge to make digital logic equipment is highly developed • Fabrication in integrated circuit form is well known, widely available • Small devices switch between cutoff and saturation states quickly – thus minimizing power consumption Page 9 ©1997-2004 R.Levine Boolean Algebra* Description •Boolean Algebra is the symbolic “language” of digital logic system design – Computers and digital switching systems almost all use hardware with 2 voltage levels – Multi-level (e.g. 4 level) hardware devices announced by Intel Corp. in 1998, but binary symbolism still used •Theoretical invention by George Boole (British mathematician ca. 1860) – “Re-discovered” by Claude E. Shannon and applied to relay logic circuit design in 1939 (master’s thesis). •Two-valued variables – Usually represented by the symbols 0 and 1 – Closely related to binary numbering system as well. *from the name of the first Arabic book known in Europe on classic algebra, Al'jabr, by Abu Ja’far Muhammed ibn Musa Al-Khwarizmi. Born approx. 780, he is credited with the introduction of the symbol for zero into Europe, and his name led to the word “algorithm.” Historically, Al’jabr means “repair of broken bones.” Today, in general, algebra means “rules for manipulation of symbols”; not limited to high school algebra using decimal numbers. Page 10 ©1997-2004 R.Levine Basic operations analogous to ordinary arithmetic • “Sum” analogous to addition, usually represented by + or sign • “Product” analogous to multiplication, usually represented by • (or * on typewriter) • Confusion is possible when binary arithmetic is under discussion vs. binary Boolean logical operations – Read with care! Page 11 ©1997-2004 R.Levine Binary Variables • Two voltage levels are most widely used – Called TTL (Transistor-transistor logic) levels – Older equipment (and some recent Intel memory chips) use more than two levels in some cases • Typically zero (actually about 0.2) and 5 volts – Lately, 3 or 1.5 volts is also used for the “high” level, for faster switching and compatibility with battery voltage (~1.5 V per cell) • High level is symbolized by 1, low by 0 – Other symbols are occasionally used: T,F; H,L; ON, OFF, etc. – In some special cases, 0 is used for high and 1 for low. This is sometimes called “negative” or “active low” logic. We will not use this method here to avoid confusion. Page 12 ©1997-2004 R.Levine One-stage Amplifier forms an Inverter (graphic symbols) y x JEDEC (Joint Electronic Defense Department Experts Commission) Symbol y x The little circle is the true graphic indicator of inversion. International Electro-technical Commission (IEC) symbol x y 0 1 1 0 • Signal flow is normally left-to-right • “Ground” wires are conventionally not drawn • The small circle represents the negation (logical negation changes 1 to 0; 0 to 1) • The triangle symbol is also used to represent a linear amplifier in other contexts. – Read with care! Page 13 ©1997-2004 R.Levine Two Chained Stages form a non-inverting device IEC Symbol y y x x y x x y 0 0 1 1 JEDEC Symbol • Logically, this does “nothing,” but in practical circuits it allows greater “fan-out” and delay • It produces greater delay – However, in modern devices, the delay per stage is typically 20 to 50 nanoseconds – Simple analysis ignores delay – Intentional delay is desired in some cases to synchronize two signal paths ©1997-2004 R.Levine Page 14 Boolean Symbolic Operations • Finite number of combinations, well represented by a table • Only 2-input forms shown here, but multiple inputs are used in general Logical sum Logical product (inclusive OR) (AND) x y z=x+y x0 y0 z0 w =x • y 0 0 0 1 1 Note, in this context, that 1+1 is 1, not 2. Page 15 1 0 1 1 1 1 ©1997-2004 R.Levine 0 1 1 1 0 1 w 0 0 0 1 Logical OR Devices • Multiple input non-inverting device with any one input sufficient to raise the output – Examples here use only 2 inputs, but multiple input OR devices are widely used • Several implementations: – – – – Transistor with two controlling electrodes “side by side” Junction transistor with two emitters FET with two gates single control electrode (emitter or gate), with multiple inputs connected via resistors (used in past with discrete components) • Either controlling electrode alone can turn the anode current ON, thus lowering Vout. – Then a second chained inverting stage used to produce binary 1 output. Page 16 ©1997-2004 R.Levine Logical AND Device • Non-inverting device constructed so that all inputs must go ON to switch the output ON – Examples here use only 2 inputs, but multiple input AND devices are widely used • Transistor constructed with multiple controlling electrodes “in series” – Any one electrode, if OFF, turns the device anode current OFF – Followed by chained inverting stage to get binary 1 output Page 17 ©1997-2004 R.Levine Other Implementations and Graphic Symbols & x JEDEC “shaped” symbol. Bullet nose, straight back y AND gate symbols • • • Hollow “box” graphic symbol represents amplifier on page 6. Via suitable resistor size choices, the circuit above could act either as an AND or an OR device (see pp. 30ff for details) A multi-input device with special input transistors can be an AND or an OR device Page 18 ©1997-2004 R.Levine JEDEC “shaped” symbol. Bullet or curved and pointed nose, concave back OR gate symbols Basic Building Blocks • In this course, we will use 3 basic building block devices: AND OR NOT • In actual system designs, the basic electronic building block modules may be NOR or NAND (that is NotOR, NotAND) – Corresponds to one-stage output physical devices – Less hardware and less signal delay in some cases – Many abstract algebra structures have multiple choices for their basic building blocks. Further exploration of alternative building blocks is not done in this course. Page 19 ©1997-2004 R.Levine Combinatorial Logical Design • No “ingenuity” is required to make a base working system – of course, further optimization is possible • Desired logical functionality must first be stated in equation or table form, relating all logical inputs to desired output(s) • SUM OF PRODUCTS: Each row in the table which produces binary 1 output can be related to a multi-input AND device, and the outputs of all such devices can be used as input to a multi-input OR device. • PRODUCT OF SUMS: Alternatively, each row in the table which produces a binary 0 can be related to a multi-input OR device, and all these outputs can be used as input to a multi-input AND device. • Choice between these two methods based on smallest component count or other criterion (fastest switching time, minimization of the number of interconnections, etc.) • Many other synthesis or design methods are also known, but not described here Page 20 ©1997-2004 R.Levine Example Logic Table and Formula _ Negation of x denoted x in most documents. We write x’ due to typographic limitations. row 0 1 2 3 4 5 6 7 x 0 0 0 0 1 1 1 1 y 0 0 1 1 0 0 1 1 Page 21 z 0 1 0 1 0 1 0 1 u 1 0 1 0 1 0 1 0 u = (x’ •y’ •z’) + (x’• y • z’) + (x • y’ • z’) + (x • y • z’) This is a “sum of products” formula. An equally valid “product of sums” formula can also be stated. Since this example has 4 zero and 4 one values for u, either method is equally “efficient” using AND and OR building blocks. ©1997-2004 R.Levine Simple Logic Synthesis Note that • or T intersection in wiring graphics represents a connection. & x Small hollow circles represent negation at the input of a multi-input device. Multi-input AND (&) output is 1 when all inputs are 1. Multi-input OR is 1 when one (or more) input(s) is/are 1. & y u & z & Page 22 ©1997-2004 R.Levine Example corresponds to previous page sum of products This design can be simplified and redesigned to operate faster (less gates in the signal path) in different ways depending on the optimization criteria. Many Standard Logic Devices • Many logical functions are required in large quantities, and are typically mass produced in special purpose integrated circuit form. – Hardware logic “works” fast, uses less chip area, has other desirable properties (vis-à-vis software). – Desirable way to implement a function if the quantity needed is large and economically attractive. • Often Called Application Specific Integrated Circuits (ASICs). Examples: – Error protection coding and decoding – Encryption/decryption devices – Devices which scan for a special binary bit pattern (e.g., for synchronization bit string within a bit stream) Page 23 ©1997-2004 R.Levine “Wired” vs. Programmable Logic • Logical operations performed by a programmable computer usually require more time and power, since operations are performed sequentially • Because hardware design (and test) is a large “up-front” cost, special hardware is usually made only for a large quantity (mass produced) product • ASICs often combine special hardware with a CPU for both the flexibility of software and the speed of wired logic • Field “Programmable” Logic Arrays (FPLAs) have numerous multi-input gates on a chip, with interconnect “wiring” (a surface metallic pattern of connections) applied by the designer for a particular application. This allows the economy of mass production with the flexibility of small production quantities. Page 24 ©1997-2004 R.Levine Appendix Supplementary reading to do after the lecture. • Alternative “product of sums” logic synthesis • AND gate vs. OR gate by changing resistors in the same basic circuit design (from p. 18) Page 25 ©1997-2004 R.Levine Alternative Logic Design • On p. 21, a table describing an arbitrary logical requirement is shown with a sum of products Boolean equation • Here is a product of sums equation with the same resulting value: u = (x +y +z’) • (x+ y’ + z’) • (x’ + y + z’) • (x’ + y’ + z’) Page 26 ©1997-2004 R.Levine Equation-Table Correspondence • Equation on p. 21 corresponds to rows 0,2,4,6 of table (rows having value u=1) • Equation on p. 26 corresponds to rows 1,3,5,7 of table (rows having value u=0) • Diagram on next page corresponds to these new Boolean equations from p. 26 Page 27 ©1997-2004 R.Levine Alternative Logic Circuit product of sums; compare with p.22 x y Small circles represent negation at the input of a multi-input device. Multi-input AND (&) output is 0 when one or more of its 4 inputs is/are 0. Output of multi-input OR is 0 when all 3 inputs are 0. & u z Page 28 ©1997-2004 R.Levine This design can be simplified and redesigned to operate faster (less gates in the signal path) in different ways depending on the optimization criteria. Circuit for AND or OR • Diagram on p. 18 can be used to make either an AND gate or an OR gate by changing resistor sizes. • For the inverter circuit on p. 6 – When vin0.9 V, output is zero (low). – When vin 0.5V, output is 5V (high) – The second chained inverter circuit on p.6 will give overall non-inverting output in the final design (see result on p. 32) – Three equal value 1k resistors are shown on p.18. Think about using other values for the two resistors on inputs x and y, with third resistor still 1k Page 29 ©1997-2004 R.Levine Chose Resistor Values • Input circuit with 3 resistors (p.18) is topologically equivalent to circuit with three resistors shown on p. 4. Use same formula. • R1 is like the x input resistor, v1 is like the x input – R2 is like the y input resistor, v2 is like the y input – R3 is like the third resistor (use 1k value) • Design objective: Use equal value (called R) for R1 and R2 , so that specific combinations of v1 and v2 produce 0.9 or 0.5 volts at the amplifier input v – Both input resistors x and y are made equal so the behavior of the device will be symmetrical with respect to the two input voltages – Small resistors produce an OR gate (one input alone can switch the output). Larger resistors produce an AND gate (high voltage on both inputs is needed to switch the output). But if the resistors are too big, the output never will switch... Page 30 ©1997-2004 R.Levine Logic Design Resistor Choices vx (V) 0 0 v=0 0 5 5 0 5 5 v=5/(2+R) Required Conclufor AND sion for AND no conv0.5 clusion v0.5 R8k v=5/(2+R) v0.5 R8k v0.9 R3.55k v=10/(2+R) v0.9 R9.11k v0.9 R9.11k • • • vy v at amp(V) lifier input Required Conclufor OR sion for OR no conv0.5 clusion v0.9 R3.55k 0.5 and 0.9 volts are input voltage “edges” of cutoff and saturation states of amplifier on page 6. For AND gate, an R value in range 8kR9.11kwill be OK For OR gate, an R3.55kwill be OK – Note that OR gate on p.18 already has R=1k Page 31 ©1997-2004 R.Levine AND gate with Resistor Input Circuit x 8 y • Same topology as p. 18, but larger x,y resistors (8k instead of 1k) • Internal construction of “non-inverting” amplifier is usually two chained inverting amplifiers like this example Page 32 ©1997-2004 R.Levine Practical Component Notes • Although an AND or OR gate can be made using resistors at the input, the operation is less reliable if the voltages or resistor values are not precise. Multiple gate FETs or multiple emitter BJTs are more reliable over a range of power and signal voltage, and require less semiconductor chip area. • Many “real” logic designs use NOR (not OR) or NAND (notAND), which do not require a second inverting amplifier. Details are omitted here for brevity. Page 33 ©1997-2004 R.Levine