* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Lecture 41

Variable-frequency drive wikipedia , lookup

Public address system wikipedia , lookup

Negative feedback wikipedia , lookup

Electrical substation wikipedia , lookup

Audio power wikipedia , lookup

Flip-flop (electronics) wikipedia , lookup

Control system wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Alternating current wikipedia , lookup

Stray voltage wikipedia , lookup

Signal-flow graph wikipedia , lookup

Voltage optimisation wikipedia , lookup

Power inverter wikipedia , lookup

Current source wikipedia , lookup

Wien bridge oscillator wikipedia , lookup

Power electronics wikipedia , lookup

Voltage regulator wikipedia , lookup

Mains electricity wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Two-port network wikipedia , lookup

Schmitt trigger wikipedia , lookup

Buck converter wikipedia , lookup

Power MOSFET wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Network analysis (electrical circuits) wikipedia , lookup

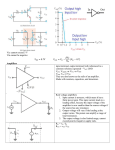

Lecture #41: Active devices • This week we will be reviewing the material learned during the course • Today: review – Active circuits – Digital logic – CMOS transistors 12/8/2004 EE 42 fall 2004 lecture 41 1 Example of the Load-Line Method Lets hook our 2K resistor + 2V source circuit up to an LED (light-emitting diode), which is a very nonlinear element with the IV graph shown below. Again we draw the I-V graph of the 2V/2K circuit on the same axes as the graph of the LED. Note that we have to get the sign of the voltage and current correct!! At the point where the two graphs intersect, the voltages and the currents are equal, in other words we have the solution. I (ma) I + 2V - LED 2K + 4 LED Solution: I = 0.7mA, V = 1.4V V - 2 5 12/8/2004 EE 42 fall 2004 lecture 41 V (Volt) 2 Simplification for time behavior of RC Circuits We call the time period during which the output changes the transient We can predict a lot about the transient behavior from the pre- and post-transient dc solutions 12/8/2004 input time voltage Long after the input change occurs things “settle down” …. Nothing is changing …. So again we have a dc circuit problem. voltage Before any input change occurs we have a dc circuit problem (that is we can use dc circuit analysis to relate the output to the input). EE 42 fall 2004 lecture 41 output time 3 RC RESPONSE Example – Capacitor uncharged: Apply voltage step of 5 V 5 Vin Input node Output node + Vout Vin - 0 0 R time Vout C ground • Clearly Vout starts out at 0V ( at t = 0+) and approaches 5V. • We know this because of the pre-transient dc solution (V=0) and post-transient dc solution (V=5V). So we know a lot about Vout during the transient - namely its initial value, its final value , and we know the general shape . 12/8/2004 EE 42 fall 2004 lecture 41 4 LOGIC GATE DELAY D Time delay D occurs between input and output: “computation” is not instantaneous Value of input at t = 0+ determines value of output at later time t = D F A Logic State B Capacitance to Ground Input (A and B tied together) 1 0 t 0 1 Output (Ideal delayed step-function) F 0 12/8/2004 D Actual exponential voltage versus time. 0 EE 42 fall 2004 lecture 41 t 5 SIGNAL DELAY: TIMING DIAGRAMS Show transitions of variables vs time Oscilloscope Probe A B C D Logic state A Note B changes one gate delay after A switches Note that C changes two gate delays after A switches. 1 0 B t 2 t 2 3 t C Note that D changes three gate delays D after A switches. 12/8/2004 t 0 EE 42 fall 2004 lecture 41 6 EXAMPLE OF THE USE OF DEPENDENT SOURCE IN THE MODEL FOR AN AMPLIFIER AMPLIFIER SYMBOL Differential Amplifier V+ V + A V0 A(V V ) AMPLIFIER MODEL Circuit Model in linear region V0 Ri + V1 + AV1 + V0 depends only on input (V+ V-) See the utility of this: this Model when used correctly mimics the behavior of an amplifier but omits the complication of the many many transistors and other components. 12/8/2004 EE 42 fall 2004 lecture 41 7 V0 NODAL ANALYSIS WITH DEPENDENT SOURCES Example circuit: Voltage controlled voltage source in a branch R5 R1 R3 Va Vb Vc R2 + VAA + AvVc R4 R6 ISS Write down node equations for nodes a, b, and c. (Note that the voltage at the bottom of R2 is “known” so current flowing down from node a is (Va AvVc)/R2.) Va VAA Va A v Vc Va Vb 0 R1 R2 R3 Vc Vb Vc Vb Va Vb Vb Vc ISS 0 R5 R6 R3 R4 R5 12/8/2004 EE 42 fall 2004 lecture 41 CONCLUSION: Standard nodal analysis works 8 NODAL ANALYSIS WITH DEPENDENT SOURCES Finding Thévenin Equivalent Circuits with Dependent Sources Present Method 1: Use Voc and Isc as usual to find VT and RT (and IN as well) Method 2: To find RT by the “ohmmeter method” turn off only the independent sources; let the dependent sources just do their thing. 12/8/2004 EE 42 fall 2004 lecture 41 9 NODAL ANALYSIS WITH DEPENDENT SOURCES Example : Find Thévenin equivalent of stuff in red box. R3 Va Vc R2 + A v Vcs R6 ISS With method 2 we first find open circuit voltage (VT) and then we “measure” input resistance with source ISS turned off. R 2 (R 6 R 3 ) You verify the solution: V ISS R 6 (R 2 AR 3 ) R TH TH R 2 R 3 R 6 (1 - A) R 2 R 3 R 6 (1 - A) 12/8/2004 EE 42 fall 2004 lecture 41 10 EXAMPLE: AMPLIFIER ANALYSIS USING THE AMPLIFIER MODEL WITH Ri = infinity: Assume the voltage between the inputs is zero, and then figure out if that is consistent, or if the amplifier will hit a rail. RF VIN RS V+ V- A + RF VIN RS V- - V0 V+ + V1 + V0 AV1 Method: We substitute the amplifier model for the amplifier, and perform standard nodal analysis - AR F solution: RIN = R F (1 A)R S VO/VIN = R F (1 A)R S 1 A 12/8/2004 EE 42 fall 2004 lecture 41 11 OP-AMPS AND COMPARATORS A very high-gain differential amplifier can function either in extremely linear fashion as an operational amplifier (by using negative feedback) or as a very nonlinear device – a comparator. Let’s see how! Differential Amplifier V+ V + A “Differential” V0 A(V V ) Circuit Model in linear region V0 Ri + V1 + AV1 + V0 depends only on difference (V+ V-) “Very high gain” A But if A ~ , is the output infinite? The output cannot be larger than the supply voltages. It will limit or “clip” if we attempt to go too far. We call the limits of the output the “rails”. 12/8/2004 EE 42 fall 2004 lecture 41 12 V0 WHAT ARE I-V CHARACTERISTICS OF AN ACTUAL HIGH-GAIN DIFFERENTIAL AMPLIFIER ? • Circuit model gives the essential linear part VIN + + V0 • But V0 cannot rise above some physical voltage related to the positive power supply VCC (“ upper rail”) V0 < V+RAIL • And V0 cannot go below most negative power supply, VEE i.e., limited by lower “rail” V0 > V-RAIL Example: Amplifier with gain of 105, with max V0 of 3V and min V0 of 3V. (a) V-V near V0 (V) origin (b) V-V over wider V0 (V) range 3 0.2 0.1 3 2 1 .2 12/8/2004 upper “rail” 2 1 1 2 3 VIN(V) lower “rail” 30 20 10 EE 42 fall 2004 lecture 41 1 2 3 10 20 30 VIN(V) 13 THE RAILS The output voltage of an amplifier is of course limited by whatever voltages are supplied (the “power supplies”). Sometimes we show them explicitly on the amplifier diagram, but often they are left off. VDD=2V Differential Amplifier V+ V + A V0= A( V V ) V+ V + A V0= A( V V ) VSS=0 If the supplies are 2V and 0V, the output cannot swing beyond these values. (You should try this experiment in the lab.) For simplicity we will use the supply voltages as the rails. So in this case we have upper rail = 2V, lower rail = 0V. 12/8/2004 EE 42 fall 2004 lecture 41 14 I-V CHARACTERISTICS OF AN ACTUAL HIGH-GAIN DIFFERENTIAL AMPLIFIER (cont.) Example: Amplifier with gain of 105, with upper rail of 3V and lower rail of 3V. We plot the V0 vs VIN characteristics on two different scales (b) V0 (V) V-V over wide range 3 upper “rail” (c) Same V0 vs VIN over even wider range V0 (V) 3 2 1 2 1 lower “rail” 12/8/2004 30 20 10 1 2 3 10 20 30 VIN(V) 3 2 1 EE 42 fall 2004 lecture 41 1 2 3 1 2 3 VIN(V) 15 Logic Gates These are circuits that accomplish a given logic function such as “OR”. We will shortly see how such circuits are constructed. Each of the basic logic gates has a unique symbol, and there are several additional logic gates that are regarded as important enough to have their own symbol. The set is: AND, OR, NOT, NAND, NOR, and EXCLUSIVE OR. A A AND C=A·B B B A B A C=A+B B OR A A NOT 12/8/2004 A B NAND C = A B NOR C = A B C AB EXCLUSIVE OR EE 42 fall 2004 lecture 41 16 Evaluation of Logical Expressions with “Truth Tables” The Truth Table completely describes a logic expression In fact, we will use the Truth Table as the fundamental meaning of a logic expression. Two logic expressions are equal if their truth tables are the same 12/8/2004 EE 42 fall 2004 lecture 41 17 Some Useful Theorems 1) A B B A Defined from form of truth tables Communicative 2) A B B A 3) A B C C B A Associative 4) A B C C B A 5) A A 0 6) A A 1 7) A B A C A (B C) Distributive 8) A B A B 9) A B A B 12/8/2004 Each of these can be proved by writing out truth tables } de Morgan’s Laws EE 42 fall 2004 lecture 41 18 Synthesis Designing the combinatorial logic circuit, con’t Method 3: NAND GATE SYNTHESIS. If we may use De Morgan’s theorem we may turn the sum-of-products expression into a form directly implementable entirely with NAND gates. (We also need the NOT function, but that is accomplished by a one-input NAND gate). function. Starting with any SUM-OF-PRODUCTS expression: Y = ABC+DEF we can rewrite it by “inverting” with De Morgan: Y (ABC) (DEF) Clearly this expression is realized with three NAND gates: one three-input NAND for (ABC) , one for (DEF) , and one two-input gate to combine them: A B C The NAND realization, while based on Y DeMorgan’s theorem, is in fact much D E simpler: just look at the sum of products F expression and use one NAND for each term and one to combine the terms. 12/8/2004 EE 42 fall 2004 lecture 41 19 Synthesis Designing the combinatorial logic circuit, con’t Method 3: NAND GATE SYNTHESIS (CONTINUED). Two Examples of SUM-OF-PRODUCTS expressions: X AB AB (X-OR function) Y ABC AB C A B C A X Y B (No connection) 12/8/2004 We could make the drawings simpler by just using a circle for the NOT function rather than showing a oneinput NAND gate EE 42 fall 2004 lecture 41 20 Controlled Switch Model of Inverter VDD = 3V + - SP SP is closed if VIN < VDD by 2V RP VIN + RN Input Note top, type P, switch is “upside down” VOUT + +SN is closed if Output SN VIN > VSS by 2V - VSS = 0V The idea: If input is 3V then top switch open, bottom one closed. And if input is 0V, bottom switch is open, and top switch closed. Thus we connect the output (through one of the resistors RP or RN) to either ground or VDD. 12/8/2004 EE 42 fall 2004 lecture 41 21 CMOS Both NMOS and PMOS on a single silicon chip NMOS needs a p-type substrate PMOS needs an n-type substrate But we can build in the same substrate by changing doping type D G S G D S oxide p p n-well n n p-well We can butt the p and n together, or even let, for example the entire non n-wellEE region be lecture p type. 12/8/2004 42 fall 2004 41 22 Basic CMOS Inverter Inverter CMOS Inverter IN VDD OUT IN VDD p-ch OUT n-ch Al “wires” IN VDD PMOS Gate Example layout of CMOS Inverter N-WELL OUT NMOS Gate GROUND 12/8/2004 EE 42 fall 2004 lecture 41 23 Al “wires” IN VDD PMOS Gate N-WELL OUT NMOS Gate GROUND 12/8/2004 EE 42 fall 2004 lecture 41 24 NMOS TransistorV DS - + VGS drain gate - + source ID IG metal oxide insulator metal n-type metal n-type p-type metal G IG ID S 12/8/2004 - VDS + D EE 42 fall 2004 lecture 41 25 NMOS I-V Characteristic G IG ID S - VDS + D • Since the transistor is a 3-terminal device, there is no single I-V characteristic. • Note that because of the insulator, IG = 0 A. • We typically define the MOS I-V characteristic as ID vs. VDS for a fixed VGS. • The I-V characteristic changes as VGS changes. 12/8/2004 EE 42 fall 2004 lecture 41 26 NMOS I-V Curves ID triode mode saturation mode VGS = 3 V VDS = VGS - VTH(n) VGS = 2 V VGS = 1 V cutoff mode (when VGS < VTH(N)) 12/8/2004 EE 42 fall 2004 lecture 41 VDS 27 Saturation in a MOS transistor • At low Source to drain voltages, a MOS transistor looks like a resistor which is “turned on” by the gate voltage • If a more voltage is applied to the drain to pull more current through, the amount of current which flows stops increasing→ an effect called pinch-off. • Think of water being sucked through a flexible wall tube. Dropping the pressure at the end in order to try to get more water to come through just collapses the tube. • The current flow then just depends on the flow at the input: VGS • This is often the desired operating range for a MOS transistor (in a linear circuit), as it gives a current source at the drain as a function of the voltage from the gate to the source. 12/8/2004 EE 42 fall 2004 lecture 41 28