* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download MOS Sequential logic III

Solar micro-inverter wikipedia , lookup

Opto-isolator wikipedia , lookup

Power inverter wikipedia , lookup

Electronic musical instrument wikipedia , lookup

Oscilloscope history wikipedia , lookup

Electronic engineering wikipedia , lookup

Flexible electronics wikipedia , lookup

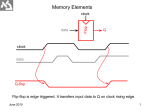

Flip-flop (electronics) wikipedia , lookup

Digital Integrated Circuits A Design Perspective Jan M. Rabaey Anantha Chandrakasan Borivoje Nikolic Designing Sequential Logic Circuits Revised from Digital Integrated Circuits, © Jan M. Rabaey el al © Digital Integrated Circuits2nd Sequential Circuits Other Latches/Registers: TSPC VDD VDD VDD VDD Out In CLK CLK In CLK CLK Out Negative latch Positive latch The main advantage is the use of single clock, but 12 transistors for the register. Also, output node might be floating (dynamic storage). It needs either a static inverter or to be made pseudo-static. © Digital Integrated Circuits2nd Sequential Circuits Embedding Logic in true single phase clock VDD VDD VDD In1 PUN VDD In2 Q In CLK CLK PDN Q CLK CLK In1 In2 Example: logic inside the latch AND latch: implements AND + latch The setup time of the embedding TSPC is smaller compared to the conventional approach, resulting in a smaller clock period, thus improves the system performance. This approach is extensively used in EV4 DEC Alpha and other processors © Digital Integrated Circuits2nd Sequential Circuits Simplified TSPC: split output VDD VDD VDD A Out In CLK VDD In CLK A Positive latch Out Negative latch Advantage: reduced complexity, reduced clock load Disadvantage: not all voltage nodes have full logic swing, e.g., node A for positive latch is VDD-VT when In=0, which results in a reduced drive for the following NMOS. © Digital Integrated Circuits2nd Sequential Circuits A specialized TSPC Register VDD VDD VDD Hold time: 1 inv M3 CLK M6 M9 Y D CLK X M2 M1 CLK M5 M4 Q PD time: 3 inv Q CLK Setup: 1 inv M8 M7 When CLK=0, X=D, second inverter is in precharge and Y=1. Third inverter is in hold mode. On rising edge of CLK, second inverter evaluates X and third inverter is on and passes Y to Q (X can make only 1->0 change during2ndthis time) © Digital Integrated Circuits Sequential Circuits An Alternative Approach to register: Pulse-Triggered Latches Up to now, we have been constructing registers using master-slave configuration. A fundamentally different approach is to use pulse signals, which is to construct a short pulse around the rising/falling edge of the clock. The pulse acts as the clock input to the latch, sampling the input only in a short window time. Race condition can be avoided by keeping the opening time of the latch very small. © Digital Integrated Circuits2nd Sequential Circuits Pulse-Triggered Latches Ways to design an edge-triggered register cell: Master-Slave registers L1 Data Pulse-Triggered Latch L2 D Q D Q Clk Clk L Data Clk D Q Clk Clk More used in AMD processors © Digital Integrated Circuits2nd Sequential Circuits Pulsed Latches VDD VDD M3 M6 CLK VDD Q D CLKG M2 CLKG M1 MP M5 CLKG X MN M4 (a) register (b) glitch generation CLK CLKG © Digital Integrated Circuits2nd (c) glitch clock Sequential Circuits Pulsed Latches When CLK=0, node X is charged up to VDD (transistor MN is off now), CLKG=0 When CLK=1, there is a short period of time when both inputs to the AND gate are high, causing CLKG=1. So, there is initial delay between the rising edge of the clock and that of the glitch pulse signal. When CLKG=1, MN is activated, pulling X to low and eventually CLKG=0. The delay time is the MN delay, AND and two Inverter gates delay, which also determines the pulse width. © Digital Integrated Circuits2nd Sequential Circuits Pulsed Latches Setup time=0, hold time=length of the pulse, propagation delay=two inverter gate delays. Advantage of the approach is reduced clock load and smaller number of transistors (pulse generation circuitry can be amortized over multiple registers). Disadvantage is a substantial verification effort (need to simulate all corners to ensure the clock pulse always reliable). © Digital Integrated Circuits2nd Sequential Circuits Another Pulsed Latch CLK VDD VDD P1 P3 x M6 M3 D Q P2 M2 M5 VDD M1 CLKD M4 Hybrid Latch – Flip-flop (HLFF) used in AMD K-6 and K-7 © Digital Integrated Circuits2nd Sequential Circuits Another Pulsed Latch When CLK=0, P1 on, X precharged to 1, Q is decoupled from X and is in hold mode. On rising edge, M3 and M6 are on and M1/M4 are on for a short period determined by the delay of three inverters. Now, D is sampled by the latch. Once CLKD goes to low, X is decoupled from D and is either held or precharged to 1 through P2. CLK CLKD Overlapping clock pairs © Digital Integrated Circuits2nd Sequential Circuits Hybrid Latch-FF Timing © Digital Integrated Circuits2nd Sequential Circuits CLK Reference data path b CLK CLK REG REG CLK REG CLK Out REG b log REG CLK REG a REG a REG Pipelining log CLK CLK Pipelined data path Simplifying the analysis, assume each logic module in the reference datapath has equal delay, then each is active for only one-third of the clock period. Pipelining is a popular design technique used to accelerate the operation of datapath in microprocessor. It improves resource utilization and increase the functional throughput. © Digital Integrated Circuits2nd Sequential Circuits Out CLK Reference © Digital Integrated Circuits2nd b CLK CLK log REG REG CLK REG CLK Out REG log REG b REG CLK a REG a REG Pipelining CLK CLK Pipelined Sequential Circuits Out Latch-Based Pipeline H E Operation of the pipeline: When CLK high, E/G writing C1/C3, while C2/C4 hold Computed F sampled onto C2 Computed G sampled onto C3 When CLK low, F/H writing C2/C4, while C1/C3 hold Disadvantage: Potential race condition with clock overlap. (e.g., if input sampled onto C1 propagates to C2 before CLK goes to low) © Digital Integrated Circuits2nd Sequential Circuits Non-Bistable Sequential Circuits─ Schmitt Trigger V OH Vou t In Out •VTC with hysteresis V OL •Fast response time •Employs positive feedback © Digital Integrated Circuits2nd VM– VM+ Vi n Sequential Circuits Noise Suppression using Schmitt Trigger © Digital Integrated Circuits2nd Sequential Circuits CMOS Schmitt Trigger Switching threshold of an inverter is determined by the kn/kp ratio of NMOS/PMOS. Increasing the ratio raises Vm, while decreasing the ratio lowers Vm. VDD M4 M2 Vin If Vin=0 so that Vout=0, M4 on, M3 off (M4,M2 together with M1). Vout X M1 M3 When it switch, M4 off, M3 on, this speeds up the transition. Similarly with Vin=1, Vout=1. Moves switching threshold of the first inverter © Digital Integrated Circuits2nd Sequential Circuits Schmitt Trigger Simulated VTC 2.5 2.5 2.0 2.0 VM1 1.5 1.0 1.5 1.0 VM2 k=1 k=3 0.5 0.0 0.0 k=2 0.5 0.5 1.0 1.5 Vin (V) 2.0 2.5 Voltage-transfer characteristics with hysteresis. © Digital Integrated Circuits2nd k=4 0.0 0.0 0.5 1.0 1.5 Vin (V) 2.0 2.5 The effect of varying the ratio of the PMOS device M4. The width is k* 0.5m m. Sequential Circuits CMOS Schmitt Trigger (2) In=0, Out=1, M5 on so that when In changes from 0 to 1, it has to be larger to discharge M5 (through VDD to M1). VDD M4 M6 M3 In Out M2 X M1 © Digital Integrated Circuits2nd M5 VDD On the other hand, once Out switches, M6 on, so positive feedback to allow fast transition (M6 diverts current to GND so that M3, M4 charges less to Out). Sequential Circuits Multivibrator Circuits R S Bistable Multivibrator flip-flop, Schmitt Trigger T Monostable Multivibrator one-shot Astable Multivibrator oscillator © Digital Integrated Circuits2nd Sequential Circuits Transition-Triggered Monostable In DELAY td © Digital Integrated Circuits2nd Out td Sequential Circuits Astable Multivibrators (Oscillators) 0 1 2 N-1 Ring Oscillator simulated response of 5-stage oscillator © Digital Integrated Circuits2nd Sequential Circuits PLL Block Diagram Reference clock Up Phase detector Local clock Charge pump Loop filter vcont VCO Down Divide by N System Clock PLL is an analog circuit, which is sensitive to all sources of noise (it might need to be guarded by careful layout). When stable, the system clock is N times the reference clock frequency and ideally 0 skew from the reference clock © Digital Integrated Circuits2nd Sequential Circuits