* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Homework #8 - University of California, Berkeley

Switched-mode power supply wikipedia , lookup

Transmission line loudspeaker wikipedia , lookup

Opto-isolator wikipedia , lookup

Flip-flop (electronics) wikipedia , lookup

Power inverter wikipedia , lookup

Two-port network wikipedia , lookup

Solar micro-inverter wikipedia , lookup

History of the transistor wikipedia , lookup

Control system wikipedia , lookup

Curry–Howard correspondence wikipedia , lookup

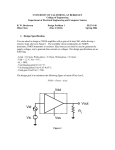

UNIVERSITY OF CALIFORNIA College of Engineering Department of Electrical Engineering and Computer Sciences Last modified on March 22, 2006 by Zhengya Zhang (zyzhang@eecs) Borivoje Nikolić EE 141 Homework #8: Pass transistor and dynamic logic Problem #1 What is the function of the pass transistor logic below? Design an alternative implementation of this gate’s logic function in pass transistor logic using two NMOS transistors and an output inverter. You may assume both polarities of A and B are available. A B’ ? A’ Problem #2 The logic function of a 2:1 multiplexer can be written as F = AC + BC’, which means when C is high, A is selected and when C is low, B is selected. a) Implement the 2:1 multiplexer in pass-transistor logic using the least number of transistors. b) Implement P1 and P2 (see the diagram below) in pass-transistor logic, so that you can build the 2:1 multiplexer in a complementary pass-transistor logic style. P1 P2 F’ F c) Implement the 2:1 multiplexer in one stage of dynamic logic. Is there any potential problem with this design? Explain. Problem #3 VDD clk M2 1um PMOS: 4um NMOS: 1um out in M3 2um clk M1 2um A domino buffer is shown above. All transistors are sized at minimum length. The widths of the transistors have been labeled on the diagram. Capacitances can be calculated as 2fF/um. VDD=2.5V. Assume γ=1. a) Find the logical effort of this domino buffer during the evaluation phase. b) Assume the output node is connected to a load CL=50fF. Calculate the delay (during the evaluation phase) from input to output in terms of tp0, the intrinsic delay of a minimum symmetrically sized inverter. A keeper PMOS is M4 added to the circuit as shown below. VDD clk M2 1um M4 out in M3 2um clk M1 2um PMOS: 4um NMOS: 1um c) Find the maximum size of M4 for proper operation of this domino buffer. You can ignore body effect. Use Table 3-2 in the textbook for parameters. d) Assume M4 is sized at 1um and output load is CL=50fF. Calculate the delay (during the evaluation phase) from input to output in terms of tp0, the intrinsic delay of a minimum symmetrically sized inverter.