* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download Undergraduate Admissions & College of Engineering

Survey

Document related concepts

Transcript

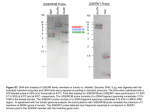

Course Overview ECE/ChE 4752: Microelectronics Processing Laboratory Gary S. May January 8, 2004 Outline Introduction Silicon Processing History of ICs Review of Semiconductor Devices Conductivity and Resistivity MOS Transistors Hot-Point Probe 4-Point Probe Growth of Electronics Industry Electronics industry is fundamentally dependent on semiconductor integrated circuits (ICs). What do you learn in 4752? This course deals with the fabrication of semiconductor devices and ICs. ICs today have over 107 components per chip, and this number is growing. Fabricating these circuits requires a sophisticated process sequence which consists of hundreds of process steps. In this course, we’ll go through a process sequence to make complementary metal-oxidesemiconductor (CMOS) transistors. Outline Introduction Silicon Processing History of ICs Review of Semiconductor Devices Conductivity and Resistivity MOS Transistors Hot-Point Probe 4-Point Probe Types of Semiconductors Elemental Compound Si GaAs, InP (III-V) Ge CdS, CdTe (II-VI) Silicon vs. Germanium Ge was used for transistors initially, but silicon took over in the late 1960s; WHY? (1) Large variety of process steps possible without the problem of decomposition (as in the case of compound semiconductors) (2) Si has a wider bandgap than Ge => higher operating temperature (125-175 oC vs. ~85 oC) (3) Si readily forms a native oxide (SiO2) high-quality insulator protects and “passivates” underlying circuitry helps in patterning useful for dopant masking (4) Si is cheap and abundant Silicon Disadvantages Low carrier mobility (m) => slower circuits (compared to GaAs) Material Si Ge GaAs Mobility (cm2/V-s) mn = 1500, mp = 460 mn = 3900, mp = 1900 mn = 8000, mp = 380 Indirect bandgap: Weak absorption and emission of light Most optoelectronic applications not possible Outline Introduction Silicon Processing History of ICs Review of Semiconductor Devices Conductivity and Resistivity MOS Transistors Hot-Point Probe 4-Point Probe The Transistor Bell Labs invented the transistor in 1947, but didn’t believe ICs were a viable technology REASON: Yield For a 20 transistor circuit to work 50% of the time, the probability of each device functioning must be: (0.5)1/20 = 96.6% Thought to be unrealistic at the time 1st transistor => 1 mm x 1 mm Ge ICs and Levels of Integration 1st IC: TI and Fairchild (late 50s) A few transistors and resistors => “RTL” Levels of integration have doubled every 34 years since the 1960s) Moore’s Law Complexity Acronyms SSI = small scale integration (~100 components) MSI = medium scale integration (~1000 components) LSI = large scale integration (~105 components) VLSI = very large scale integration (~105 - 106 components) ULSI = ultra large scale integration (~106 - 109 components) GSI = giga-scale integration (> 109 components) State of the Art 1 GB DRAM 90 nm features 12” diameter wafers Factory cost: ~ $3-4B => Only a few companies can afford to be in this business! Outline Introduction Silicon Processing History of ICs Review of Semiconductor Devices Conductivity and Resistivity MOS Transistors Hot-Point Probe 4-Point Probe Diamond Lattice Tetrahedral structure 4 nearest neighbors Covalent Bonding Each valence electron shared with a nearest neighbor Total of 8 shared valence electrons => stable configuration Doping Intentional addition of impurities Adds either electrons (e-) or holes (h+) => varies the conductivity (s) of the material Adding more e-: n-type material Adding more h+: p-type material Donor Doping Impurity “donates” extra e- to the material Example: Column V elements with 5 valence e-s (i.e., As, P) Result: one extra loosely bound e- eP Acceptor Doping Impurity “accepts” extra e- from the material Example: Column III elements with 3 valence e-s (i.e., B) Result: one extra loosely bound h+ h+ B Outline Introduction Silicon Processing History of ICs Review of Semiconductor Devices Conductivity and Resistivity MOS Transistors Hot-Point Probe 4-Point Probe Ohm’s Law J = sE = E/r where: s = conductivity, r = resistivity, and E = electric field s = 1/r = q(mnn+ mpp) where: q = electron charge, n = electron concentration, and p = hole concentration For n-type samples: s ≈ qmnND For p-type samples: s ≈ qmpNA Resistance and Resistivity length = L area = A R = rL/A Outline Introduction Silicon Processing History of ICs Review of Semiconductor Devices Conductivity and Resistivity MOS Transistors Hot-Point Probe 4-Point Probe MOSFET Metal-oxide-semiconductor field-effect transistor IDn D + VSG - + G B + VGS - + VB S S n-channel device VDS G S + VS B B - + VS D - -IDp D p-channel device G = gate, D = drain, S = source, B = body (substrate) MOSFET Cross-Section S VG VD > 0 ID G oxide n+ ID n+ L D S p-type Si cross-sectional view (not to scale) top view (not to scale) Basic Operation 1) Source and substrate grounded (zero voltage) 2) (+) voltage on the gate Attracts e-s to Si/SiO2 interface; forms channel 3) (+) voltage on the drain e-s in the channel drift from source to drain current flows from drain to source valve (gate) pipe (channel) drain source Hot-Point Probe Determines whether a semiconductor is n- or p-type Requires: Hot probe tip (soldering iron) Cold probe tip Ammeter Hot-Point Probe 1) Heated probe creates high-energy “majority” carriers holes if p-type electrons if n-type 2) High-energy carriers diffuse away 3) Net effect: a) deficit of holes (net negative charge for p-type); OR b) deficit of electrons (net positive charge for n-type) 4) Ammeter deflects (+) or (-) 4-Point Probe Used to determine resistivity 4-Point Probe 1) Known current (I) passed through outer probes 2) Potential (V) developed across inner probes r = (V/I)tF where: t = wafer thickness F = correction factor (accounts for probe geometry) OR: Rs = (V/I)F where: Rs = sheet resistance (W/ ) => r = Rst Virtual Cleanroom http://www.ece.gatech.edu/research/labs/vc/ Web site that describes entire ECE/ChE 4752 CMOS Fabrication Process!