* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Security and Testing - Information Systems and Internet Security

Survey

Document related concepts

Transcript

Security and Testing

by

Kurt Rosenfeld

M.S., City College of New York, 2004

B.S., City College of New York, 2002

A thesis submitted to the

Faculty of the Graduate School of the

Polytechnic Institute of NYU in partial fulfillment

of the requirements for the degree of

Doctor of Philosophy

Department of Computer Science and Engineering

2012

Microfilm or copies of this dissertation may be obtained from:

UMI Dissertation Publishing

ProQuest CSA

789 E. Eisenhower Parkway

P.O. Box 1346

Ann Arbor, MI 48106-1346

Vita

Kurt Rosenfeld was born in 1972, in Palo Alto, California. He received the B.S.

degree in Electrical Engineering from The City College of New York in 2002 and the

M.S. degree in Electrical Engineering from The City College of New York in 2004.

From 2005 to the present, he has been in the Information Systems and Internet

Security Lab at Polytechnic institute of NYU, studying with Professors Ramesh

Karri and Nasir Memon.

His research interests include hardware security, distributed system security, and

testing. He is an engineer at Google, Inc.

Acknowledgements

I would like to express my gratitude for all of the help I got from my family,

advisors, friends, colleagues, and my employer. Without your support I would have

failed. Your patience, generosity, and encouragement have been my extremely good

fortune.

This work was partly supported by NSF award numbers 0831349 and 0621856.

Abstract

This dissertation presents research on improving the security of computing platforms at a physical and logical level. The main contributions are to improve the

security of:

1. test data communication between chips

2. test data communication within chips

3. communication between sensors and chips

4. verification of chip authenticity

We investigated the security of IEEE 1149.1 JTAG and studied existing attacks.

We invented two new attacks and experimentally verified them. After generalizing

the threats, we designed and implemented a security-enhanced backwards compatible

version of JTAG.

We identified security vulnerabilities that stem from the use of shared test onchip test data wiring in system-on-chip (SoC) designs, particularly where trusted

and untrusted cores coexist. We developed an efficient architecture and protocol

that mitigates test-related risks.

We extended the concept of the physical unclonable functions to encompass sensors. The result is a sensor whose measurement can be verified by the logic inside

the trust perimeter.

We propose countermeasures to the growing problem of counterfeit components.

We developed an inexpensive end-to-end scheme for ensuring the authenticity of

parts received by a system integrator.

The four platform security enhancements we developed complement each other.

They solve non-overlapping problems that exist today and they can be applied individually or together. Applied together, they significantly raise the bar for platform

security.

Contents

Chapter

1 Introduction

1

1.1

The Core Root of Trust . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1

1.2

Trustworthy Hardware . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1

1.3

Testing

2

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2 Security of Digital System Testing

2.1

3

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3

2.1.1

Development of Test Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3

2.1.2

Example: Testing a Two-bit State Machine . . . . . . . . . . . . . . . . . . . . . . . .

4

2.1.3

Fault Testing versus Trojan Detection . . . . . . . . . . . . . . . . . . . . . . . . . . .

10

2.1.4

VLSI Testing: Goals and Metrics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11

2.1.5

Conflict Between Testability and Security . . . . . . . . . . . . . . . . . . . . . . . . .

12

Scan-based Testing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

12

2.2.1

Scan-based Attacks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

13

2.2.2

Countermeasures for Scan Attacks . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

14

2.3

BIST . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

16

2.4

JTAG . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

18

2.4.1

JTAG hacks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

22

2.4.2

JTAG Defenses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

23

2.2

v

2.5

2.6

2.7

SoC test Infrastructure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

26

2.5.1

SoC Test Hacks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

27

2.5.2

Defenses for SoC Test Mechanisms . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

28

Emerging Areas of Test Security . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

30

2.6.1

OBD-II for Automobile . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

30

2.6.2

Medical Implant Interface Security . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

31

Recapitulation and Projection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

32

3 JTAG Security

33

3.1

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

33

3.2

JTAG Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

35

3.2.1

BYPASS Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

35

3.2.2

EXTEST Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

35

3.2.3

INTEST Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

35

3.3

JTAG Attacks

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

36

3.3.1

Sniff Secret Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

38

3.3.2

Read Out Secret . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

39

3.3.3

Obtain Test Vectors and Responses . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

40

3.3.4

Modify State of Authentic Part . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

41

3.3.5

Return False Responses to Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

41

3.3.6

Forcing TMS and TCK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

42

3.4

Prior Work on Attacks and Defenses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

46

3.5

Defenses for JTAG . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

46

3.5.1

Secure JTAG Communication Protocol

. . . . . . . . . . . . . . . . . . . . . . . . . .

48

3.5.2

Level 0 Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

49

3.5.3

Level 1 Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

50

3.5.4

Level 2 Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

50

vi

3.5.5

3.6

3.7

Level 3 Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

51

Costs and Benefits Associated with JTAG Defenses . . . . . . . . . . . . . . . . . . . . . . . .

52

3.6.1

Die Area Overhead . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

52

3.6.2

Test Time Overhead . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

53

3.6.3

Operational Costs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

54

3.6.4

Impact of Defenses on Known Threats . . . . . . . . . . . . . . . . . . . . . . . . . . .

54

Conclusion

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4 Testing Cores in a System on Chip

4.1

55

57

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

57

4.1.1

Assumptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

58

4.1.2

Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

59

4.1.3

Core Test Wrappers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

60

4.2

Prior Work . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

60

4.3

Proposed Approach . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

61

4.3.1

Security-enhanced Test Wrapper . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

61

4.3.2

A Security Overwrapper for Prewrapped Cores . . . . . . . . . . . . . . . . . . . . . .

66

4.3.3

Interoperability with Noncompliant Cores . . . . . . . . . . . . . . . . . . . . . . . . .

66

Costs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

66

4.4.1

Die Area Cost

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

66

4.4.2

Test Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

68

4.4.3

Effort for SoC Integrator

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

69

Conclusion and Future Work . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

69

4.4

4.5

5 Integrity and Authenticity of Sensors

5.1

71

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

71

5.1.1

Related Work . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

72

5.1.2

Our Contribution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

73

vii

5.1.3

5.2

5.3

5.4

5.5

5.6

Security Properties . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

74

Candidate Sensor PUF . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

74

5.2.1

Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

75

5.2.2

Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

79

Electrical Analysis and Experimental Results . . . . . . . . . . . . . . . . . . . . . . . . . . .

80

5.3.1

Assumptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

80

5.3.2

Distribution of Cut Points . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

80

5.3.3

Hamming Distance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

84

5.3.4

Verification of Offset Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

85

Security Context of Sensor PUFs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

87

5.4.1

Substitution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

87

5.4.2

Tampering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

87

5.4.3

Manufacturer Resistance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

88

5.4.4

Sensor Decoupling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

88

Security Analysis . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

89

5.5.1

Attack Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

89

5.5.2

Attack Trees . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

90

Future Work in Sensor PUFs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

93

6 Future Work in Hardware Security

95

7 Publications

96

Bibliography

98

Figures

Figure

2.1

A two-bit counter with synchronous reset has four states. From each state, there are two

possible next states. This realization provides an output signal that is asserted when the

counter is in state S03. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2

5

The machine behaves similarly to the machine shown in Figure 2.1, but deviates for certain

rare inputs. Starting in initial state S00, if RST is given the sequence 0,1,0,0,1,0,0,0 the

machine enters state S23, at which point the behavior of the system deviates from that shown

in Figure 2.1. S23 is a terminal state. The only way to exit S23 is to reinitialize the system

(e.g., cycle the power). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7

2.3

A cascadable section of a synchronous binary counter with synchronous reset. . . . . . . . . .

10

2.4

The simplest scan flip-flop cell is simply composed of a multiplexer and a regular D flip-flop.

The Q output of one scan cell can be connected to the TEST INPUT of another scan cell,

enabling a chain configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5

13

Secure Scan state diagram. The only way to get from secure mode, where the mission key

is loaded, to insecure mode, where the chip is testable, is to go through a power cycle reset,

which wipes all volatile state variables.

2.6

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

15

Secure Scan architecture. The mirror key register (MKR) is loaded only when Load Key is

active, which is controlled by the state machine shown in Figure 2.5.

. . . . . . . . . . . . .

16

ix

2.7

Bed of nails test fixture. Automated test equipment (ATE) generates stimulus signals and

measures responses. The ATE is connected to the test fixture, which contains one nail per

test channel. Each nail is spring-loaded so it maintains a controlled pressure when contacting

the test points on the printed circuit board being tested. . . . . . . . . . . . . . . . . . . . . .

2.8

18

The JTAG state machine. There are 16 states. The TMS signal determines the next state.

The SHIFT DR state is used for applying stimuli and collecting responses. From any state,

the TEST LOGIC RESET state can be reached by holding TMS high for five clock cycles. .

2.9

20

A typical JTAG system. TMS, TCK, and TRST are bussed to all of the devices. TDO of

each component is connected to TDI of the next component, thereby forming a daisy-chain

topology.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

21

2.10 The essential components of a basic JTAG implementation include a test access port state

machine, an instruction register, one or more data registers, and an output multiplexer. Each

chain of scan flip-flop cells (internal or boundary) appears to JTAG as a data register that

can be selected with the appropriate instruction. . . . . . . . . . . . . . . . . . . . . . . . . .

22

2.11 A chain of scan cells is used for distributing keys to each of the cores. The scan cells are

configured not to expose key bits at their outputs while they are being shifted. . . . . . . . .

3.1

29

The typical deployment of JTAG is a chain of several devices on a printed circuit board. Each

device may come from a different vendor. The test mode select (TMS), test clock (TCK), and

test reset (TRST) signals are typically common to all chips. The test data in (TDI) signal and

test data out (TDO) signals loop through the chips. The path returns to the source, which is

usually either a PC or an embedded microcontroller, functionally called a “system controller.” 34

x

3.2

Conceptual security model: A set of attackers A1, A2, and A3 have a set of goals G1 through

G6. Each attacker has a set of attack capabilities, some or all of which are masked by defenses

that are in place. There is a set of attacks, K1 through K4, each of which requires a certain

set of unmasked attack capabilities. Each attack can be used to reach some set of goals. This

example shows that attacker A1 can achieve goals G2 and G4 since it has capabilities P2 and

P4, which are the requirements for attack K2. Attackers A2 and A3 do not have sufficient

unmasked capabilities to execute any of the attacks. . . . . . . . . . . . . . . . . . . . . . . .

36

3.3

The attacker obtains secret data by sniffing the JTAG data path.

. . . . . . . . . . . . . . .

38

3.4

The attacker obtains an embedded secret by forcing test vectors onto the JTAG lines. . . . .

39

3.5

The attacker obtains a copy of the test vectors and normal responses of a chip in the JTAG

chain. This can be a passive attack. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6

The attacker can intercept test vectors that are sent to another chip, and can send false

responses to the tester.

3.7

40

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

41

A Philips 8052 (the system controller) was programmed to keep one of its pins low. The I-V

curve for this output driver was extracted using a pulsed I-V measurement. A Xilinx Spartan

3e was programmed to keep one of its pins high. This pin’s I-V curve was also extracted.

The result is shown. The solid line is the FPGA; the dashed line is the microcontroller. The

intersection is at 2.1V, exceeding VIH for most 3.3V logic.

3.8

. . . . . . . . . . . . . . . . . . .

A length of PCB wiring connects the hijacker to the JTAG master. This allows the attacker

to inject short pulses onto the wiring without being hindered by the master.

3.9

44

. . . . . . . . .

45

We define four levels of assurance. Levels correspond to the set of assurances that are provided. 49

xi

3.10 Area overhead is shown for the protection levels 1 through 3, from bottom to top. The cost

of the security enhancements independent of design complexity, so the percentage overhead

is lower for more complex designs. The four levels of assurance provide progressively higher

levels of assurance. An indication of the area cost of each protection level is given by the

number of additional FPGA slices used by the enhanced JTAG circuitry. These figures are

for a Spartan 3e. There are no fuses in the FPGA so fuses are modeled as hard-coded bit

vectors. Overhead in an ASIC will be less.

4.1

. . . . . . . . . . . . . . . . . . . . . . . . . . . .

53

Data sent from the test controller to core 2 passes through core 1, giving core 1 an opportunity

to intercept it. Likewise, data passing from core 2 back to the tester passes through core 3,

giving core 3 an opportunity to intercept it. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2

A chain of scan cells is used for distributing keys to each of the cores. The scan cells are

configured not to expose key bits at their outputs while they are being shifted. . . . . . . . .

4.3

59

62

The key setup scan chain conveys data from the test controller to the core wrapper key

registers without allowing it to be sniffed or modified by other cores. Other than the basic

distributed shift register functionality, the only extra functionality we require of our scan cell

is an output inhibit input (O INH) to ensure that the key is not leaked during shifting. After

the tester has the key bits shifted to their intended location, the tester deasserts the output

inhibit signal so that the cores receive their key data. . . . . . . . . . . . . . . . . . . . . . . .

4.4

64

In a typical security-enhanced wrapped core, a word of compressed test data arrives via the

parallel data input, is decrypted instantaneously, decompressed and applied to the inputs

of the core’s scan chains. The outputs are compressed, encrypted, and sent out. Standard

wrapper components are not shown, such as the parallel bypass. . . . . . . . . . . . . . . . .

5.1

The naı̈ve secure sensor architecture does not bind the sensing with the cryptography, allowing

the analog link between the sensing element and the crypto processor to be easily attacked. .

5.2

65

72

A conventional silicon PUF has a binary input and a binary output. The sensor PUF has a

binary input, physical quantity being sensed, and a binary output. . . . . . . . . . . . . . . .

73

xii

5.3

The analog portion of the light level sensor PUF includes the coating, the photodiode groups,

the switches, the summing junctions, and the analog comparator. The challenge applied to

the sensor PUF determines the keystream input to the control circuit, which controls the

random selection of left gate signals GL.i and the right gate signals GR.i, which determine

the set of sensors that are included in the summations. The left and right sums are compared,

producing one raw bit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.4

76

a: The offset generator produces a DC voltage that is determined by the optical transmittance

of the coating at the sites of photodiodes P D1 and P D2 . b: The slope generator produces a

voltage proportional to the light input at photodiode P3 . . . . . . . . . . . . . . . . . . . . . .

5.5

77

In all four subfigures, the sensor input level is on the x-axis and the electrical response is on

the y-axis. Subfigure (a) shows eight photodiode group response lines generated by simulation

of the candidate light sensor PUF. The bold line is the sum of the eight lines. Subfigures (b),

(c), and (d) show pairs of response lines that occur for different values of the left and right

gate signals. Assuming a sensor input value of 10 and assuming that solidline > dashedline

is interpreted as a “1”, evaluating the comparisons for the line pairs shown in (b), (c), and

(d) gives the raw bit sequence “0”, “1”, “0”. In our simulations, the raw bit sequences are

256 bits long.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

78

5.6

The probability density function of offset current ratios observed in simulation. . . . . . . . .

82

5.7

The density function of the offset signal of each individual photodiode group. . . . . . . . . .

82

5.8

The green trace shows the probability density function of the cut points in the sensor input

domain, as observed in simulation. The red trace shows the Cauchy density function for χ = 0

and γ = 20.

5.9

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

83

Hamming distance for five statistically independent instances of the candidate sensor PUF . .

84

5.10 The offset generator circuit shown in Figure 5.2.1 was constructed and tested using light from

an LED driven by a variable current source. The offset voltage is plotted across the range of

currents for three different relative transmittances. We see ±2.5% variation over the range. .

86

5.11 SPICE simulation of the offset generator output voltage across a range of light intensity values. 86

xiii

5.12 Attack tree for replay. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

91

5.13 Attack tree for cloning.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

92

5.14 Attack tree for inducing errors in measurement. . . . . . . . . . . . . . . . . . . . . . . . . . .

93

Chapter 1

Introduction

1.1

The Core Root of Trust

Trust in information systems is built from the ground up. Just as human knowledge is built on a set

of core beliefs, information system security is based on a set of assumptions. These assumptions form the

root of trust for the system. For example, common assumptions in microprocessor-based systems are that

data written to memory will be read back correctly and that the computer’s internal state is secret unless

an I/O operation is made that explicitly writes the data. The root of trust can be different for different

systems, but if a system is to provide any kind of assurance, there must be a root of trust.

Untrustworthy components can be useful parts of a trustworthy system as long as they are outside the

core root of trust, explicitly untrusted, and appropriate design measures are taken. For example, consider a

computer where the secrecy of the data in main memory cannot be ensured. The architecture can encrypt

data when writing it to main memory and decrypt it when reading it, thereby eliminating exposure of secret

data. Here, although the main memory is untrusted, the encryption, decryption, and key management is

trusted. This is a typical example of trust relocation. The architect has freedom to relocate the root of trust

but cannot eliminate it.

1.2

Trustworthy Hardware

Traditionally, in most information systems, the root of trust has been the behavior of the hardware.

This trust has been informally justified by the relative difficulty for an attacker to change the behavior of

2

the hardware. Although it remains to be seen whether trustworthy hardware is actually a requirement for

trustworthy computation, it is certainly a convenient assumption. The field of hardware security aims to

make the assumption correct.

When we say that hardware is secure, we mean that it provides functionality the can be relied on

despite physical threats. For example, a soda vending machine is secure hardware. It is intended to behave

correctly in a moderately hostile physical environment. In contrast, personal computers generally are not

secure hardware. In a hostile physical environment, most personal computers yield total control to an

attacker. Once a personal computer enters the attacker’s physical control, the machine can no longer be

trusted by its rightful owner. Trusted platform modules are only a partial remedy. In their most common

use case, they are islands of trust in a sea of untrustworthy components. Personal computers with trusted

platform modules offer little security in physically hostile environments.

1.3

Testing

Testing and security are closely related. Both aim to provide some kind of assurance to humans

about what we can expect from a system. A battery tester tells us how much more life we can expect from

a battery. A security evaluation of a system tells us what threats the system can be expected to resist.

Testing, as opposed to measurement, is rarely passive. Testing typically involves application of a stimulus

and observation of a response. Since this generalization encapsulates all functional interactions between

modules in a system, the stimulus-response frameworks that are built for testing are often used for other

maintenance tasks, like configuring and programming the system.

Chapter 2

Security of Digital System Testing

2.1

Introduction

Test interfaces are present in nearly all digital hardware. In many cases, the security of the system

depends on the security of the test interfaces. Systems have been hacked in the field using test interfaces as

an avenue for attack. Researchers in industry and academia have developed defenses over the past twenty

years. A diligent designer can significantly reduce the chance of system exploitation by understanding known

threats and applying known defenses.

2.1.1

Development of Test Interfaces

Test interfaces have been part of man-made systems for at least 100 years. They address a need for

applying a stimulus and/or making an observation via a path other than the primary functional path. For

example, large tanks holding liquids or gases usually have inspection ports. These ports allow the internal

condition of the tank to be visually evaluated to avoid unexpected failure due to corrosion. Otherwise, it

would be difficult to predict failure. Brake systems on cars often have inspection holes in the calipers. This

allows the condition of the brake pads to be assessed without disassembling the brakes. More than just

the functional question of whether the brakes work, the inspection hole allows the mechanic to answer the

deeper question of how much more life is left in the brake pads. In areas where operational reliability and

efficiency are valued, features are added to products to make them testable, to let their maintainers probe

their internal condition.

As electronic devices grew more complex in the mid 20th century, it became difficult to tune them or

4

diagnose problems with only an input-output view of the system. Take, for example, a 1960’s radio receiver.

These receivers contain several filters and mixers cascaded to form the desired frequency response. There

are dozens of adjustments, many of which interact, and all of which affect the output. Optimal receiver

performance is achieved for a specific vector of settings. Applying a signal to the input while observing the

output, it is almost impossible for the technician to infer which adjustment to change to bring the receiver

closer to correct alignment. To make their equipment maintainable, manufacturers provided test points

in their circuits, where signals could be measured or injected. This allowed the circuit to be structurally

decomposed to make maintenance straightforward. Each section can be independently aligned, a process

involving only a small number of adjustments.

When electronic computers were first developed in the 1940’s and 50’s, it was customary to write “test”

or “checkout” programs that could be run on the system to verify correct functionality of the hardware. Test

programs were designed so that if it failed, it would provide the technician with an indication of where it

failed, speeding diagnosis and repair. The method of running programs on the computer to test the computer

is really just functional testing, and since there isn’t enough time for the tests to cover all possible states

and transitions of the hardware, this testing paradigm can never provide rigorous assurance of the hardware

even if all of the tests pass.

As the complexity of computers grew in the 1960’s, designers sought stronger assurance from testing,

and faster fault isolation. From an operational standpoint in the field, designers wanted to minimize the

mean time between when a fault is detected and when the system is back up. As computers began to

play crucial roles in real-time operations, high availability became a goal, in addition to the traditional

performance goals. All of these factors led major computer developers such as IBM to develop techniques

for testing the structural blocks independently.

2.1.2

Example: Testing a Two-bit State Machine

As an illustration of a digital circuit testing problem, consider testing a 2-bit synchronous circuit with

the state diagram shown in Figure 2.1. The circuit has two inputs: clock and reset. It has one output

signal, which is high if and only if the state is S3. On every rising edge of the clock signal, the next state is

5

determined as follows:

• If the reset signal is asserted, the next state is S0.

• Otherwise, the next state is oldstate+1 mod 4.

RST=0

S01

RST=1

RST=0

S02

RST=1

S00

RST=0

S03

RST=X

RST=1

Figure 2.1: A two-bit counter with synchronous reset has four states. From each state, there are two possible

next states. This realization provides an output signal that is asserted when the counter is in state S03.

The process of testing a practical state machine implementation is affected by three main considerations:

(1) What are we trying to determine?

(2) What can we assume about the device under test?

(3) How is our testing constrained?

2.1.2.1

What are we trying to determine?

For the first question, one possible answer is that we are trying to determine whether the device

under test is equivalent to a reference implementation or model. Equivalence, in this case, means that for all

possible input sequences, the outputs are the same. Another possibility is that we aim to determine whether

the device is equivalent to the reference implementation for some restricted set of inputs. Yet another

possibility is that we are checking whether an invariant rule is satisfied for some set of input sequences.

6

2.1.2.2

What can we assume?

Assumption 1: Number of States

The second question we must ask when testing a circuit is what we can assume. A state machine is composed

of a set of states, a set of edges (transitions), a set of inputs, a set of outputs, and an initial state. It is

profoundly helpful to know how many states the system has, how many flip-flops are in the circuit. If we

know how many states it has, we can, for example, apply the pumping lemma for regular languages [3], to

place limits on the state machine’s behavior. The pumping lemma states that if the number of states is

finite, there must be an infinite set of input sequences that result in the same final state. This has practical

ramifications for testing. If the number of states is bounded, it is possible, at least in theory, to completely

test the circuit using a finite set of test vectors.

Under adverse security circumstances, we are not able to safely assume that the device under test has

the number of states it is specified to have. A trojan horse might be inserted into the circuit during design

or fabrication. A typical trojan horse waits for a trigger, which is a special pattern or a sequence. The

trigger occurs in, for example, the input data stream, the trojan activates its payload. A payload carries out

a malicious action which can be as complex as executing an embedded program, or as simple as halting or

resetting the system. Trojans are designed to pass normal testing, so they typically contain all of the benign

specified logic, plus extra logic for trigger detection and payload execution. Consequently, from a testing

standpoint, the trojan is more an extra feature than a defect.

Testing for the presence of extra state variables is exceedingly difficult. Consider testing a system that

is intended to implement the four-state state machine shown in Figure 2.1. There are two inputs: clock and

reset. There is one output. The output is “1” when the state is S0. The system could faithfully implement

the intended state machine (Figure 2.1), or it might, for example, implement the state machine shown in

Figure 2.2, where the output is “1” when the state is S00, S10, S20, or S30.

RST=0

S11

RST=1

7

RST=0

S12

RST=0

RST=1

RST=0

S10

S21

RST=1

S22

RST=0

S13

RST=1

S20

RST=0

S23

RST=X

RST=X

RST=1

RST=1

RST=1

RST=0

RST=0

S01

S02

S31

S32

RST=1

RST=0

RST=1

S00

RST=0

S03

RST=0

RST=0

S30

RST=X

RST=1

S33

RST=X

RST=1

RST=1

Figure 2.2: The machine behaves similarly to the machine shown in Figure 2.1, but deviates for certain rare

inputs. Starting in initial state S00, if RST is given the sequence 0,1,0,0,1,0,0,0 the machine enters state

S23, at which point the behavior of the system deviates from that shown in Figure 2.1. S23 is a terminal

state. The only way to exit S23 is to reinitialize the system (e.g., cycle the power).

For normal inputs, the machine shown in Figure 2.2 might be indistinguishable from the machine in

2.1, but it has more states than the intended design. Certain rare sequences of inputs cause the two machines

to differ in their outputs. Black-box testing would be much more likely to conclude that the state machines

8

are the same than to find the difference. The rare sequence that causes them to differ can be the trigger for

an embedded trojan, and the way in which the they differ can be the payload of that trojan. For example,

if we assume that the machine has four states, as intended, then we would expect the test sequence shown

in Table 2.1 would thoroughly test the circuit.

RST

1

0

0

0

0

1

0

0

1

0

1

0

0

0

1

Current Output

X

0

0

0

1

0

0

0

0

0

0

0

1

0

1

Transition

X → S0

S0 → S1

S1 → S2

S2 → S3

S3 → S0

S0 → S0

S0 → S1

S1 → S2

S2 → S0

S0 → S1

S1 → S0

S0 → S1

S1 → S2

S2 → S3

S3 → S0

Table 2.1: Test routine for a two-bit counter. All edges of the specified state transition graph are tested.

Since we cannot force the counter directly into a arbitrary state, we must sequentially visit the states

and test each of the edges while observing the functional output.

However, consider the effect of that test sequence on the machine shown in Figure 2.2. The machine

goes through the following sequence of states: S00, S01, S02, S03, S00, S00, S01, S02, S00, S01, S10, S11,

S12, S13, S10. At no point during the test sequence does its externally observable behavior differ from the

intended behavior, that shown in Figure 2.1, although the final state is not the initial state. In the case

of this example, running the test sequence repeatedly will not uncover any differences between the actual

state machine and the specified one. Although the Figure 2.1 system and Figure 2.2 system are the same for

the Table 2.1 test sequence, they behave quite differently for other test sequences, specifically, any sequence

that puts the Figure 2.2 system into the S23 state, where it locks up. In summary, when testing a state

machine, we make an assumption about the number of states. If our assumption is wrong, we are likely to

make invalid inferences about the system under test.

9

Assumption 2: Determinism or Randomness

A pivotal assumption is that the device under test is deterministic. If it is not, then we must characterize

its behavior statistically instead of logically. That completely changes the nature of the testing procedure.

One example is a testing pseudorandom bit sequence generator. The output is expected to satisfy certain

statistical requirements. There are standard requirements, such as Golomb’s randomness postulates. A single

test is not sufficient to establish the randomness of a sequence. Standard suites of tests have been developed

for the purpose of comparatively evaluating cryptographic systems [4]. Related to the testing pseudorandom

sequence generators is the testing of “true” randomness sources, which derive their randomness from a

physical source. Typically a diode is used as a noise source, which is then digitized to produce random bits.

Testing such devices for their fitness in security-critical applications involves several special criteria such as

their immunity to external factors influencing their output.

How is our testing constrained?

Systems that only allow interaction in their normal functional use pattern demand black-box testing. This

constraint can appear for a variety of reasons, and has wide-ranging implications. One reason for the absence

of test features is their perceived cost, either in engineering effort or in production cost. The implications of

being forced to resort to black-box testing are an exponential increase in the time required to test a system,

and decreased confidence that it is thoroughly tested.

When we are not constrained to black-box testing, the practical approach to testing, for example, a

counter, is to structurally decompose it and test the components and the interconnections, and then argue

that if the components are good, and the interconnections are good, then the system is good. When we

decompose the circuit, we break it into small islands of logic that are easily testable, avoiding the exponential

explosion of test complexity seen in the previous paragraph. A 2-bit counter can be implemented as two

1-bit sections cascaded. A 128-bit counter can be implemented as 128 cascaded sections, each containing a

flip flop and three logic gates, as shown in Figure 2.3.

carry_out

10

Qi

carry_in

Q

D

Q’

reset’

Figure 2.3: A cascadable section of a synchronous binary counter with synchronous reset.

If suitable test structures are provided, the 128 sections can be tested independently. The number of

tests necessary for one isolated section is

#tests = 2F2I

where F is the number of flip-flops in each section and I is the number of inputs to each section. We

have F=1 and I=2, so eight tests a required per section of the counter. If the stages of a B-bit counter are

tested sequentially, the number of tests is

#tests = 2F2IB = 8B

Without structural decomposition, we have to visit each state and test the circuit’s response to the

RESET=0 input and the RESET=1 input. This requires two tests per state, so

#tests = 2 * 2B = 2B+1

Structural testing is not just somewhat more efficient than black-box testing. It is profoundly more

efficient. The number of tests required for structural testing is of linear complexity, O(B), while black-box

testing is of exponential complexity. O(2B). Similar general results apply to circuits other than counters.

The total complexity of the pieces of a logic circuit is almost always less than the complexity of the circuit

as a whole. Consequently black-box testing of whole circuits is avoided for all but the simplest systems.

2.1.3

Fault Testing versus Trojan Detection

The standard goals of test engineering are to detect flaws that occur naturally during fabrication and

isolate the exact location of the flaw. Any significant deviation from the behavior intended by the designers

is considered a fault. By this definition, a piece of malicious logic that is added to the design by an attacker

11

before fabrication is a fault. Although it might seem elegant, and it is certainly correct, to group malicious

modifications with manufacturing faults, it is not practical to do so. The fault models assumed when testing

for manufacturing faults do not include the changes that would be made by a malicious party who adds some

kind of trojan horse to the design.

2.1.4

VLSI Testing: Goals and Metrics

VLSI testing is always done in terms of a prescribed fault model. For example, a common fault model

for logic circuitry is that each node can be correct, stuck at 1, or stuck at 0. If this stuck-at fault model is

used, the goal of testing is determine, for each node, which of the three conditions describes it. A set of tests

is said to cover a fault if the test would detect the fault, if the fault were present in the device being tested.

Test coverage is the percentage of possible faults that are covered by a given set of tests. In many cases, it

is practical to create a set of tests that has 100% coverage. In some cases, 100% coverage is not reachable

for a practical number of test vectors.

The number of test vectors that are needed for 100% test coverage is an indication of the testability

of the circuit. Two factors are important in determining the testability of the circuit:

• controllability

• observability

Certain topologies are known to result in poor testability. One example is reconvergent fanout. This

is when a signal fans out from a single node and follows multiple parallel paths, and the reconverges into

a single node. This topology exhibits poor testability because the signals along the parallel paths are not

independently controllable. Logic gates with a large number of inputs, particularly XOR gates, are also

problematic.

Design for Test (DFT) is a design process that runs in parallel with the functional design process. The

goal of DFT is to ensure that the final design meets testability goals while minimizing the costs associated

with testing. There are four main costs that relate to testing.

• Die area cost

12

• Time required to apply tests

• Cost of the required testing station

• Computation required to generate test vectors

2.1.5

Conflict Between Testability and Security

Conventional security best practices are to conceptualize the system as a set of modules which expose

simple interfaces and hide their internal implementation. This type of control limits the complexity of the

interactions in the system. However, black-box testing is profoundly inefficient. Providing controllability

and observability of the internal elements within a module makes that module testable, but the module then

loses the security that comes from having a single, restricted interface. Thus, there is an apparent conflict

between security and testability.

2.2

Scan-based Testing

As we discussed in the previous section, an important approach for achieving testability in a VLSI

chip is to include elements in the design that allow it to be structurally decomposed for testing. Most designs

are synchronous, meaning that they are composed of logic and flip-flops, and the flip-flops only change state

during the rising or falling edges of the clock. Synchronous designs can be separated into a set of logic gates,

which can be tested by verifying their truth table, and a set of flip-flops, which can be tested by chaining

them to form a shift register. This scan-based testing paradigm replaces the regular flip-flops in the design

with “scan flip-flops” as shown in Figure 2.4.

13

D

TEST

ENABLE

Q

DFF

TEST INPUT

CLOCK

Figure 2.4: The simplest scan flip-flop cell is simply composed of a multiplexer and a regular D flip-flop.

The Q output of one scan cell can be connected to the TEST INPUT of another scan cell, enabling a chain

configuration.

These are flip-flops with input multiplexers which select between the regular “functional” input, and

the test-mode input. Typically, the test-mode input comes from the output of another flip-flop, thus forming

a scan chain. The operation of a scan chain can be thought of as having three phases:

• Assert test mode. All flip-flops are configured into a distributed shift register. Test data is shifted

in. This data is applied to the inputs of the logic.

• Deassert test mode. Flip-flops are configured to get their data from the outputs of the logic. The

flip-flops are clocked, thus latching in the output value of the logic.

• Reassert test mode. All flip-flops are configured into a distributed shift register. Test data is shifted

out. This data is returned to the tested for analysis and comparison with the expected output.

Using this testing method, the tester only tests combinational logic, instead of testing state machines.

This amounts to a profound reduction in the testing time required to achieve a given level of test coverage.

2.2.1

Scan-based Attacks

Systems that support scan-based testing are potentially vulnerable to attacks that use the scan chains

as vectors for reading or modifying sensitive data contained in the device. Cryptographic keys are common

targets for this kind of attack.

The most basic scan attack applies to chips that contain a key register that can be scanned. In

this attack the attacker typically connects to the JTAG port of the victim chip, selects the scan chain that

14

contains the key register, and shifts out the key.

Less naive chips avoid having the key directly scannable. However, simply excluding the key register

from the scan chain is not sufficient to prevent a skilled attacker from extracting the key. Yang, Wu, and

Karri [5] present a practical attack against an AES hardware implementation with a non-scannable key

register. They exploit the scan chains as an information leakage path, allowing recovery of the crypto key.

They assume that the key is not directly scannable, and their attack uses indirect information to reconstruct

the key. They also assume that the attacker does not have knowledge of the internal scan chain structure of

the crypto chip. The attack begins with discovering the scan chain structure, determining which bit positions

in the scan chain correspond to the bits of the intermediate result register. Next, using the observability of

the intermediate result, the attacker recovers the round key. The attack shows that even if the key register

is not exposed directly though any scan chain, the byproducts of the key contain enough information for the

attacker to infer the key bits.

2.2.2

Countermeasures for Scan Attacks

Countermeasures are available for protecting against scan attacks. There is a tradeoff between security

and testability. Effective countermeasures for scan attacks must simultaneously provide acceptable levels of

security and testability.

Hely, Flottes, and Bancel, et. al. [6] observe that a static assignment of functional registers to positions

in the scan chain is risky because an attacker can infer the assignment and then use the scan chain to extract

secret information from the chip. To mitigate this threat, they introduce Scan Chain Scrambling. For the

authorized user, a test key is provided to the chip and assignment of registers to scan chain positions is

static. For an attacker without the ability to authenticate, the assignment is semi-random. Chunks of the

set of scannable flip-flops are mapped to chunks of the scan chain sequence, but the order will be unknown

to the attacker. The permutation changes periodically while the chip is operating.

Yang, Wu, and Karri [7] propose the “Secure Scan” scheme for protecting embedded keys from being

leaked via scan chains. To allow the crypto hardware to be fully tested without exposing the key or its

byproducts, Secure Scan introduces a second embedded key, the mirror key for use during testing.

lxxv

15

Figure 4.2: State diagram of secure scan architecture

Figure 2.5: Secure Scan state diagram. The only way to get from secure mode, where the mission key is

crypto chip is powered off. The operations of crypto chips using the proposed secure scan

architecture

are summarized

in Figure

4.2. is to go through a power cycle reset, which wipes all

loaded, to

insecure mode,

where the chip

is testable,

The design of MKR is shown in Figure 4.3. A multiplexer controlled by Load Key

volatile state variables.

can be inserted either at the input to the MKR (Figure 4.3(a)) or at the output of MKR

(Figure 4.3(b)). In Figure 4.3(a), when Load Key signal is active, the input of the MKR is

locked to secret key. Any operation that writes to or scans the MKR is disabled. In Figure

At any moment, as shown in Figure 2.5, the chip is either in mission mode (“Secure mode”) or test

4.3(b), the output of the MKR is masked by secret key when Load Key signal is active. The

MKR structure

doesmode,

not modify

the scan

and

the

insertion

of

mode (“Insecure

mode”).shown

Whenin

theFigure

chip is4.3(b)

in secure

the mission

key iscell

used

but

scanning

is disallowed.

the additional multiplexer does not modify the scan chain. Therefore it is easy to integrate

When the chip is in insecure mode, scanning is allowed, but only the mirror key is used. It is impossible

secure scan into current scan DFT design flows.

The secure

DFT architecture

introduces

threeoff

new

Scan

In, almost

to get from secure

modescan

to insecure

mode without

powering

thecontrol

chip. signals

Secure Enable

Scan thus

allows

Enable Scan Out and Load Key. There are two ways to generate these signals. One way

completeisstructural

exposing

the mission

key. Since

the mission

key is not

to modifytestability

the IEEE without

1149.1 JTAG

Controller

as shown

in Figure

4.4 by adding

one used

morewhile the

named

Secure

the isstandard

16-state

TAP FSM.

new instruction

nameddrawback

chip is instate

insecure

mode,

the Mode

missiontokey

obviously

untestable.

This is,A however,

not a serious

Drive Secure Mode that can be applied through TMS pin is added. In the 16-state TAP

in practice

sincethe

theSelect-IR-Scan

correctness of the

can be

verified by state

functional

FSM,

statekey

jumps

intoquickly

Test-logic-reset

when testing.

a one is received

from TMS pin. In the modified TAP controller that supports secure scan architecture, the

Select-IR-Scan state jumps into Secure Mode when a one is received from TMS pin. Once

the TAP Controller is in this state, it does not take instructions from TMS any more. The

transition from Secure Mode to Test-logic-reset will not happen until the chip is reset or

lxxiv

16

Figure 4.1: Secure scan architecture with a mirror key register

Figure 2.6: Secure Scan architecture. The mirror key register (MKR) is loaded only when Load Key is

isolate the secret key from the crypto core. The mirror key register works like a normal

register. Enable Scan In and Enable Scan Out signals are active and general scan-based

DFT can be performed. The states of all registers in the design can be scanned in and out

to verify if the fabricated chip performs as expected. Note that in the model we used for

Lee, Tehranipoor, and Plusquellic [8] point out that the intellectual property contained in an integrated

scan-based side channel attack, the key register is not included in the scan chain. On one

circuit

is also

risk because

of scan

chains.

An attacker

and observe

signals inside

a chip

hand

suchatmodel

provides

limited

security

sincethat

we can

needcontrol

to perform

the two-step

attack

shown

in previous

the other

it alsoTo

limits

the this,

test the

maytoberecover

able to the

inferkey

theas

logical

structure

of thesection.

chip, andOn

thereby

learnhand,

the design.

prevent

capability since only the functionality involving this key is verified. In the secure scan

authors introduce a technique they call Low-Cost Secure Scan, that blocks unauthorized access to the scan

DFT architecture, higher fault coverage can be expected since multiple test vectors can be

scanned

into the mirror

registers.to the algorithms used for inserting scan chains in designs, but

chains.

The technique

requireskey

modification

Once the function of the crypto chip and upper layer software has been verified, the

the scope of the protection includes the intellectual property of the design, not just embedded keys. To

chip is driven into secure mode for its practical applications. In the secure mode, the secret

use key

the Low-Cost

system,

vectorsLoad

that Key

are applied

bitstime

in addition

to the

is appliedSecure

to theScan

crypto

corethe

by test

enabling

signal.contain

At thekey

same

the scan

function is disabled by de-activating Enable Scan In and Enable Scan Out signals. This

test stimulus. If the key bits are correct, the chip produces the pre-calculated output. Otherwise, the test

prevents access to the mirror key register. Scan mode signal remains inactive during secure

response

pseudorandom.

Theoperation

pseudorandom

response is intended to raise the difficulty for an attacker

modeisand

hence no shift

is performed.

Once

the chip

is in secure

it cannot

return

insecureexplicit

mode indication

to perform

who wishes

to launch

a guessing

attack,mode,

as opposed

to giving

an to

immediate

of any

whether

test and debug operation. The secret key is loaded to the crypto core only when the chip

the attacker’s guess is correct.

is in the secure mode. Although the temporary results are stored in other registers, they

cannot be scanned out. The only way to re-enter the insecure mode is to reset the chip

2.3by power

BIST

off followed by a power on operation. All registers inside the chip that have

temporary results are cleared. Since in crypto chips such as smart cards, a key is usually

Built-In

Self Test (BIST)

is a popular

technique

testing

hardware

requiringwhen

external

stored

in nonvolatile

memory

or fabricated

as afor

fixed

value,

it will without

not be cleared

the test

active, which is controlled by the state machine shown in Figure 2.5.

equipment. There are many varieties of BIST designed to test different kinds of circuits and to detect

different classes of faults. A common feature of all BIST systems is that a large volume of test data moves

17

between the on-chip BIST logic and the circuit under test, while a minimal amount of data moves between

the chip and it surrounding system. In the extreme, the chip can simply produce a one-bit status indication

of whether it is working correctly, or there is an error.

Two of the most common varieties of BIST are memory BIST and logic BIST. In principle, differentiating between memory and logic is not necessary. In practice, testing techniques that target a specific type

of circuit are much more efficient in terms of test time required to get adequate fault coverage. Typical memory BIST uses a state machine or a small embedded microprocessor to generate memory access signals that

carry out a standard memory test algorithm such as of the March series of tests [9]. In a typical logic BIST

setup, pseudorandom test vectors are generated on-chip and applied to the circuit under test. The responses

are compacted and aggregated during many test cycles, using a Multiple-Input Shift Register (MISR). This

produces a fixed-length final value that is compared with the expected value, which is hard-coded into the

chip.

From a security standpoint, BIST has many ramifications. In both logic and memory testing, the

BIST controller can act as a trusted proxy between the tester and the chip’s core logic. This architecture

can raise security by enforcing a limited set of actions that can be taken by a tester. The enforcement of

limited interfaces is consistent with good security design (e.g., principle of least privilege). The tester of

cryptographic logic needs assurance that the hardware is working correctly, but shouldn’t necessarily have

access to secret data in the chip, such as an embedded key. Similarly, BIST can provide assurance that

a memory is error-free while eliminating the possibility of misuse of memory “debugging” functionality for

tampering with security-critical data.

Despite BIST’s advantages of running at full functional clock speed and improving security, it has

two problems. First, it typically provides fault detection, but not fault isolation. Second, it adds area to the

chip. A BIST implementation contains a test pattern generator and an output response analyzer. Both of

these hardware modules occupy area. However, in certain applications this area cost can be eliminated. A

technique called Crypto BIST [10] uses a symmetric cipher core (AES) to test itself. By looping the output

of the AES core back into the input, the AES core functions as both the test pattern generator and output

response analyzer. Crypto BIST achieves 100% stuck-at fault coverage of the AES core in 120 clock cycles of

18

test time. The essence of the technique is the observation that strict avalanche criterion of the cryptographic

algorithm causes the AES core to act as both a diverse source of test patterns and a sensitive output response

analyzer, leading to high test coverage in few cycles.

2.4

JTAG

In the 1970’s and early 1980’s, a common way of testing printed circuit boards was to add test points,

and to probe these test points with a bed-of-nails test fixture, as shown in Figure 2.7.

test point

component

printed circuit board

test fixture

nail

ATE

Figure 2.7: Bed of nails test fixture. Automated test equipment (ATE) generates stimulus signals and

measures responses. The ATE is connected to the test fixture, which contains one nail per test channel.

Each nail is spring-loaded so it maintains a controlled pressure when contacting the test points on the printed

circuit board being tested.

This approach could not keep up with increases in component density and pin spacing. Alternative

methods of testing were developed. As always, cost was a major factor affecting the choice of test method.

Interoperability was also a factor, since components from many manufacturers coexist on large printed circuit

19

boards. Having a single test interface from which all components could be tested was desired. The solution

was developed by a working group known as the Joint Test Access Group in the 1980’s. This became IEEE

Standard 1149.1 and is widely referred to simply as JTAG.

IEEE 1149.1 standardizes the set of signals used to access test logic inside chips. The standard specifies

the use of scan-based testing for the internal logic of the chip and also for the inter-chip wiring. JTAG uses

synchronous serial communication with separate signals for data and control. Using 1149.1, a tester can force

signals on pins, read signals on pins, apply signals to the core logic, read signals from the core logic, and

invoke arbitrary custom test functions that might exist in certain chips. However complicated the testing

task might be, the communication always takes place over the same wires:

• TCK - test clock, while in test mode, all events happen on edges of TCK

• TMS - test mode select, determines the next state of the JTAG port

• TDI - test data in, test vectors and JTAG instructions are applied via TDI

• TDO - test data out, test responses or data that loops through

• TRST - test reset, optional hardware reset signal for the test logic

20

0

TEST_LOGIC_RST

0

0

RUN_TEST_IDLE

1

SELECT_DR

1

SELECT_IR

0

0

1

1

CAPTURE_DR

CAPTURE_IR

0

0

0

SHIFT_DR

SHIFT_IR

1

1

EXIT1_DR

0

PAUSE_IR

1

0

1

EXIT2_DR

0

0

EXIT2_IR

1

1

UPDATE_DR

Figure 2.8: The JTAG state machine.

1

EXIT1_IR

PAUSE_DR

1

0

1

0

0

1

0

There are 16 states.

UPDATE_IR

1

0

The TMS signal determines the next

state. The SHIFT DR state is used for applying stimuli and collecting responses. From any state, the

TEST LOGIC RESET state can be reached by holding TMS high for five clock cycles.

An important feature of JTAG is its support for daisy chaining. Devices can be wired in a chain where

the TDO (output) of one device is applied to the TDI (input) of the next device in the chain, as shown in

Figure 2.9. The TCK, TMS, and TRST signals can be simply bussed to all chips in the chain, within fan-out

limits. Otherwise, buffers can be used. Each chip in the JTAG chain has a state machine implementing the

21

protocol shown in Figure 2.8.

TDO

DEVICE 5

TMS

DEVICE 3

COMPUTER

WITH

JTAG

INTERFACE

DEVICE 4

TCK

TRST

TDI

DEVICE 1

DEVICE 2

Figure 2.9: A typical JTAG system. TMS, TCK, and TRST are bussed to all of the devices. TDO of each

component is connected to TDI of the next component, thereby forming a daisy-chain topology.

One of the state variables controlled by the state machine is the Instruction Register (IR), shown in

Figure 2.10. The instruction register is typically between 4 and 16 bits. Some instructions are mandated

by the JTAG standard, while implementers are free to define as many of their own instructions as they like.

One of the most important instructions is the required instruction, BYPASS. When the IR contains the

BYPASS opcode, a JTAG-compliant chip places a single flip-flop in the path from its TDI input to its TDO

output. Therefore a chain of chips in the BYPASS state behaves like a shift register.

22

select lines

BYPASS REGISTER

TDO

BOUNDARY SCAN REGISTER

TDI

IDCODE REGISTER

INSTRUCTION REGISTER

TAP

STATE

MACHINE

TMS

Figure 2.10: The essential components of a basic JTAG implementation include a test access port state

machine, an instruction register, one or more data registers, and an output multiplexer. Each chain of

scan flip-flop cells (internal or boundary) appears to JTAG as a data register that can be selected with the

appropriate instruction.

2.4.1

JTAG hacks

JTAG has played a part in many attacks on the security of digital hardware. Attackers have used it

to copy cryptographic keys out of satellite boxes for the purpose of pirating satellite TV service [11]. The

JTAG port in Microsoft’s Xbox 360 has been exploited to circumvent the DRM policies of the device [12].

Powerful low-level capabilities are often exposed through the JTAG interfaces of systems. Attackers have

learned this, and when they attack a device, they look for a JTAG port, among other things.

Rosenfeld and Karri [13] examine the threat of JTAG-level hacking. Specific attention is given to

the vulnerabilities that result from the common daisy-chain topology of JTAG wiring. They consider the

possibility of one malicious node in a JTAG chain attacking other nodes or deceiving the tester. They

examine the threat of a malicious node hijacking the bus by forcing the control signals. With two nodes (the

23

tester and the attacker) both driving a bus wire at the same time, it becomes an analog question, who will

win. The research showed that it was often possible for the attacking node to hijack the bus when the JTAG

bus wires are short, and always possible to hijack when the bus wires are long, due to pulse properties of

transmission lines.

2.4.2

JTAG Defenses

Several defenses for JTAG have been proposed over the years. When considering JTAG defenses, it

is important to keep in mind the many constraints and requirements that affect the design process. For

example, flexibility to provide in-field firmware updates is often valuable, but for this to be secure, some

sort of authentication mechanism is required. Some applications have tight requirements on cost and cannot

tolerate the extra circuitry required for authentication. As always in engineering, there are trade-offs, and

making the best choice requires a detailed understanding of the application.

2.4.2.1

Elimination of JTAG

One way to eliminate the risks associated with JTAG is to eliminate JTAG from the design. There

are several ways this can be done while maintaining low escape rate, the probability of a defective part being

shipped to a customer.

One method is simply to use conservative design rules. Common sources of manufacturing faults are

shorts and opens in the metal wiring of the chip. If wires are made wider, and spacing between wires is

kept greater, many manufacturing faults are eliminated. If transistors have non-minimum gate length, that

eliminates another source of faults. This approach has a high cost in area and speed.

Another method, and one that is very popular, is to use Built-In Self Test (BIST), discussed in Section

2.3. The result of running BIST can be as simple as a single bit indicating whether the chip passes the tests

or fails. In this form, BIST provides security benefits because internal scan can be eliminated from the set

of supported JTAG instructions, thus significantly reducing the chip’s attack surface.

BIST, however, is not always a satisfactory replacement for scan-based testing. Since BIST test vectors

are generated pseudorandomly instead of deliberately, using an automated test pattern generation (ATPG)

24

algorithm, it can be difficult to get full test coverage using BIST. This is partially offset by the fact that BIST

is typically done at-speed, meaning that test vectors are applied at the same rate that functional data would

normally be applied. In contrast, when test vectors are applied using external automated test equipment,

the test clock is typically an order of magnitude slower than the functional clock. Another disadvantage of

BIST is that it does not provide fault isolation. For the engineers developing a chip, it is essential to be

able to quickly iterate toward a successful design that can be shipped. Without the ability to determine the

location and type of the fault, designers are not able to fix the problem. For this reason, BIST is more useful

for testing during full production and in the field, where a failure will simply cause the part to be discarded.

Scan-based test infrastructure is often retained in the design, in case it is needed for engineering purposes.

2.4.2.2

Destruction of JTAG Hardware After Use

In many circumstances, an argument can be made that the test structures in a chip are only needed at

the factory, and constitute nothing more than a security risk once the chip is shipped. In such cases designers

sometimes elect to disable the JTAG circuitry on the chip after testing. A common way of implementing

this is with fuses that can be electrically blown by the tester. For finer grained control over what capabilities

remain enabled, the design can contain more than one fuse. A patent by Sourgen [14] in 1993 discusses these

techniques.

The IMX31 microprocessor from Freescale Semiconductor is an ARM-based chip intended for mobile

and media applications. This type of embedded processor is often required to protect the data that in

processes, in the case of digital rights management, and the code that it runs, in cases where the system

software contains valuable intellectual property. The IMX31 supports four JTAG security modes, selectable

by blowing fuses. In mode 4, the JTAG logic allows all possible JTAG operations. In mode 1, only the JTAG

operations necessary for interoperability are allowed. Blowing fuses is an irreversible operation. Therefore,

the security mode can be raised, but never lowered. This is fits well with a common use case of JTAG,

where it is used at the factory for testing and perhaps by engineers for in-system debugging in their labs,

but should not be used in the field by hackers.

25

2.4.2.3

Password Protection of JTAG

Buskey and Frosik developed a scheme they call Protected JTAG [15], which enhances the security of

JTAG by requiring authentication and authorization to access particular features of the chip’s test structures.

The scheme makes use of a trusted server which uses a pre-shared elliptic curve key pair to prove to the chip

that the user’s JTAG access request has been authenticated. The authors anticipate a use case where the

tester connects directly to the chip and connects to the trusted server via the Internet, using standard Internet

communication security protocols. Once authentication is complete, the chip stays in the authenticated state

for the duration of a test session. The benefits of having a separate trusted server for authentication and

authorization are that these can be managed independently, after the chip is deployed. For example, a new

user can be added anytime, with access to an arbitrary set of test features. A disadvantage of the scheme is

the reliance on the continued security and availability of the authentication server.

2.4.2.4

Hiding the JTAG Behind a System Controller

One approach to JTAG security is to use a system controller chip. In this architecture, the system

controller acts as a proxy for test-related communication with one or more chips, typically on a printed circuit

board. This scheme adds security to a system without requiring any modification to the chips themselves.

The system controller can enforce sensible security policies such as:

• All accesses must be authenticated.

• Authenticated testers can only access the resources for which they are authorized.

• Only signed and verified firmware updates are permitted.

• Backrev (reverting to a previous version) of firmware is not permitted.

• All communication between the tester and the system controller is cryptographically protected

against man-in-the-middle attacks.

The system controller can play an active role in the testing and maintenance of the system, beyond

simply acting as a proxy [16]. The system controller can store test sequences and run the tests automatically

26

at power-up time or when a specific test routine is externally invoked. This architecture provides the benefits

of BIST as discussed in Section 2.3. A controller supporting this type of approach is commercially available

under the name SystemBIST [17]. It also provides functionality for verifying the state of JTAG-connected

devices, for example, to verify that the configuration bit file of an FPGA was correctly programmed. As with

all practical security, it is not absolute. Successful practical approaches have to strike a balance between cost,

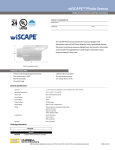

functionality, and security. The value of the system controller approach is that it preserves the economy of