* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Bandgap References

Three-phase electric power wikipedia , lookup

Ground (electricity) wikipedia , lookup

Electrical ballast wikipedia , lookup

History of electric power transmission wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Electrical substation wikipedia , lookup

Stray voltage wikipedia , lookup

Two-port network wikipedia , lookup

Voltage optimisation wikipedia , lookup

Schmitt trigger wikipedia , lookup

Current source wikipedia , lookup

Surge protector wikipedia , lookup

Earthing system wikipedia , lookup

Integrated circuit wikipedia , lookup

Alternating current wikipedia , lookup

Buck converter wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Mains electricity wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Network analysis (electrical circuits) wikipedia , lookup

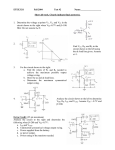

類比電路設計(3349) Bandgap References Ching-Yuan Yang National Chung-Hsing University Department of Electrical Engineering Overview z Reading B. Razavi Chapter 11. z Introduction Analog circuits incorporate voltage and current references extensively. Such references are dc quantities that exhibit little dependence on supply and process parameters and a well-defined dependence on the temperature. In this lecture, we deal with the design of reference generators in CMOS technology, focusing on well-established “bandgap” techniques. In most applications, the required temperature dependence assumes one of three forms: (1) proportional to absolute temperature (PTAT); (2) constant-Gm behavior; (3) temperature independent. In addition, several parameters of reference generators, such as output impedance, output noise, and power dissipation, may be critical as well. Analog Circuit Design 11-1 Ching-Yuan Yang / EE, NCHU Supply-independent biasing z Current-mirror biasing using (a) an ideal current source, (b) a resistor. Te output current is quite sensitive to VDD: ΔI out = (W / L )2 ΔVDD ⋅ R1 + 1/ gm1 (W / L )1 How do we generate IREF independent of the supply voltage? z Simple circuit to establish supply-independent currents. In order to arrive at a less sensitive solution, we postulate that the circuit must bias itself, i.e. , IREF must be somehow derived from Iout. If M1-M4 operate in saturation and λ = 0, then Iout = KIREF, and hence can support any current level. Analog Circuit Design 11-2 Ching-Yuan Yang / EE, NCHU Supply-independent biasing z Addition of RS to define the currents z Alternative implementation eliminating body effect Assuming λ = 0, then Iout = IREF and VGS1 = VGS2 + ID2RS . 2I out 2I out + VTH 1 = + VTH 2 + I out RS μnCox (W / L )N μnCox K (W / L )N Neglecting body effect, we have That is, I out = 1 ⎞ 2I out ⎛ ⎜1 − ⎟ = I out RS μnCox (W / L )N ⎝ K⎠ 2 1 ⎛ 1 ⎞ ⋅ 2 ⎜1 − ⎟ μnCox (W / L )n RS ⎝ K⎠ Analog Circuit Design 2 11-3 The current is independent of the supply voltage (but still a function of process and temperature). Ching-Yuan Yang / EE, NCHU Supply-independent biasing (cont’d) z Addition of RS to define the currents (assuming λ ≠ 0). Determine ΔIout /ΔVDD. R1 = ro1 || (1/gm1), R3 = ro3 || (1/gm3) V VDD − V X + I out R3gm 4 = X R1 ro 4 The equivalent transconductance of M2 and RS is Gm 2 = ⎤ 1 ⎡ 1 I Thus, out = − g m 4R 3 ⎥ ⎢ VDD ro 4 ⎣Gm 2 (ro 4 R1 ) ⎦ Analog Circuit Design gm 2ro 2 I out = RS + ro 2 + (gm 2 + gmb 2 )RSro 2 VX −1 → 0, if ro4 = ∞. 11-4 Ching-Yuan Yang / EE, NCHU Supply-independent biasing (cont’d) z Addition of RS to define the currents An important issue in supply-independent biasing is the existence of “degenerate” bias points. For example, if all the transistors carry zero current when the supply is turned on, they may remain off indefinitely because the loop can support a zero current in both branches. In other words, the circuit can settle in one of two different operating condition z Addition of start-up device The diode-connected device M5 provides a current path from VDD through M3 and M1 to ground upon start-up. This technique is practical on if VTH1 +VTH5 + |VTH3| < VDD and VGS1 +VTH5 + |VGS3| > VDD, the latter to ensure M5 remains off after start-up. Analog Circuit Design 11-5 Ching-Yuan Yang / EE, NCHU Temperature-independent reference z How to generate a quantity that remains constant with temperature? Ð If two quantities having opposite temperature coefficients (TCs) are added with proper weighting, the result displays a zero TC. - Ex. VREF = α1V1 + α2V2, with zero TC, i.e., α1∂V1/∂T + α2∂V2/∂T = 0. Analog Circuit Design 11-6 Ching-Yuan Yang / EE, NCHU Negative-TC voltage For a bipolar device, where IC = IS exp(VBE /VT), where VT = KT /q. The saturation current IS is proportional to μkTni2, where μ denotes the mobility of minority carries and ni is the intrinsic minority carrier concentration of silicon. Temperature dependence: μ ∝ μ0Tm, and ni2 ∝ T3exp[−Eg/(KT)], where m ≈ −3/2 and Eg ≈ 1.12eV is the bandgap energy of silicon. Find TC of VBE: since VBE = VT ln(IC /IS) and I S = bT 4+ m exp − Eg − Eg ⎛ ∂I S = b(4 + m )T 3+ m exp + bT 4+ m ⎜⎜ exp kT kT ∂T ⎝ ⎞⎛ E g ⎞ ⎟⎟⎜⎜ 2 ⎟⎟ ⎠⎝ kT ⎠ ⇒ − Eg kT , then Eg VT ∂I S V = (4 + m ) T + 2 VT I S ∂T T kT ∂VBE ∂VT I C VT ∂I S VBE − (4 + m )VT − E g / q = ln − = I S I S ∂T T ∂T ∂T ⇒ With VBE ≈ 750mV and T = 300oK, ∂VBE /∂T ≈ −1.5mV/oK. The temperature coefficient of VBE itself depends on the temperature, creating error in constant reference generation if the positive-TC quantity exhibits a constant temperature coefficient. Analog Circuit Design 11-7 Ching-Yuan Yang / EE, NCHU Positive-TC voltage z Generation of PTAT voltage If IS1 = IS2, and the base currents are negligible, then ΔVBE = VBE1 − VBE 2 = VT ln nI 0 I − VT ln 0 = VT ln n I S1 IS2 Thus, ΔVBE exhibits a positive temperature coefficient: ∂ΔVBE k = ln n ∂T q The TC is independent of temperature or behavior of z Another type collector currents. ∂ΔVBE k = ln (mn ) ∂T q Analog Circuit Design 11-8 Ching-Yuan Yang / EE, NCHU Bandgap reference z Develop a reference having a nominally zero TC: Let VREF = α1VBE1 + α2(VT lnn), where VT lnn is the difference between the base-emitter voltage of the two bipolar transistors operating at different current densities. How to choose α1 and α2? Since at room temperature ∂VBE /∂T ≈ −1.5mV/oK whereas ∂VT /∂T ≈ +0.087mV/oK, we set α1 =1, and choose (α2lnn)(∂VT /∂T) = −α1∂VBE /∂T = −1.5mV/oK, then α2 lnn ≈ 17.2,indicating that for zero TC: VREF ≈ VBE1 + 1.72VT ≈ 1.25V. z Conceptual generation of temperature-independent voltage Two modifications: A mechanism must be added to guarantee VO1 = VO2. Since lnn = 1.72 translates to a prohibitively large n, the term RI = VT lnn must be scaled up by a reasonable factor. Analog Circuit Design 11-9 Ching-Yuan Yang / EE, NCHU Actual implementation of bandgap reference z Vout = VBE 2 + ⎛ ⎞ ΔVBE (R3 + R2 ) = VBE 2 + (VT ln n )⎜⎜1 + R2 ⎟⎟ R3 ⎝ R3 ⎠ where ΔVBE = VBE1 − VBE2 = VT lnn. z For a zero TC, we have (1 + R2/R3)lnn ≈ 17.2. For example, we may choose n = 31 and R2/R3 = 4. Note these results do not depend on the TC of the resistors. Analog Circuit Design 11-10 Ching-Yuan Yang / EE, NCHU Collector current variation z What happens to the temperature coefficient of VBE if the collector currents are PTAT? Since VBE = VT ln(IC /IS), we have ⎛ 1 ∂I C 1 ∂I S ⎞ ∂VBE ∂VT I C ⎟⎟ ln + VT ⎜⎜ = − ∂T ∂T IS ⎝ I C ∂T I S ∂T ⎠ Since IC1 = IC2 ≈ (VT lnn)/R3 ⇒ ∂IC /∂T ≈ (VT lnn)/(R3T) = IC /T, we have ∂VBE ∂VT I C VT VT ∂I S ln + = − I S T I S ∂T ∂T ∂T = VBE − (3 + m )VT − E g / q T indicating that the TC is slightly less negative than −1.5mV/oK at T = 300oK. Analog Circuit Design 11-11 Ching-Yuan Yang / EE, NCHU Compatibility with CMOS technology z Realization of a pnp bipolar transistor in CMOS technology. The p-type substrate acts as the collector and it is inevitably connected to the most negative supply (usually ground). z Circuit implemented with pnp transistors Analog Circuit Design 11-12 Ching-Yuan Yang / EE, NCHU OP amp offset and output impedance z Effect of op amp offset on the reference voltage If A1 is large, VBE1 − VOS ≈ VBE2 + R3 IC2 and Vout = VBE2 + (R3 + R2)IC2. Thus, Vout = VBE 2 + (R3 + R2 ) VBE1 − VBE 2 − VOS R3 ⎛ R ⎞ = VBE 2 + ⎜⎜1 + 2 ⎟⎟(VT ln n − VOS ) ⎝ R3 ⎠ The key point is that VOS is amplified by 1 + R2/R3, introducing error in Vout. More importantly, VOS itself varies with temperature, raising the temperature coefficient of the output voltage. Analog Circuit Design 11-13 Ching-Yuan Yang / EE, NCHU Reduction of the effect of op amp offset z R1 and R2 are ratioed by a factor of m, producing I1 ≈ mI2. z Neglecting base currents and assuming A1 is large, we have VBE1 + VBE2 − VOS = VBE3 + VBE4 + R3I2 and Vout = VBE3 + VBE4 + (R3 + R2)I2. It follows that Vout = VBE 3 + VBE 4 + (R3 + R2 ) 2VT ln (mn ) − VOS R3 ⎛ R ⎞ = 2VBE + ⎜⎜1 + 2 ⎟⎟[2VT ln (mn ) − VOS ] ⎝ R3 ⎠ z Biased by PMOS current sources The effect of the offset voltage is reduced by increasing the first term in the square brackets. z The implementation is not feasible in a standard z CMOS technology because the collectors of Q2 and z Q4 are not grounded. We modify the series combination z of the diodes as illustrated in Fig.(a), converting to one of the diodes to an emitter follower. Analog Circuit Design 11-14 Ching-Yuan Yang / EE, NCHU Reduction of the effect of op amp offset (cont’d) z Reference generator incorporating two series base-emitter voltage Discussion: Advantage: • The op amp experiences no resistive loading. Disadvantage: • The mismatch and channel-length modulation ¾ of the PMOS devices introduce error at the ¾ output. • Since Q2 and Q4 have a finite current gain β, they generate an error in the emitter currents of Q1 and Q3 and introduce error at the output. Analog Circuit Design 11-15 Ching-Yuan Yang / EE, NCHU Feedback polarity The negative feedback factor is given by β N = The positive feedback factor is given by β P = 1 / g m 2 + R3 1 / g m 2 + R3 + R2 1 / g m1 1 / g m1 + R1 To ensure an overall negative feedback, βP must be less than βN, preferably by roughly a factor of two so that the transient response remains well-behaved with large capacitive loads. Analog Circuit Design 11-16 Ching-Yuan Yang / EE, NCHU Bandgap reference V ∂V ∂V Bandgap reference VREF = VBE + VT lnn, then . REF = BE + T ln n ∂T T ∂T Setting we have ∂VBE VBE − (4 + m )VT − E g / q ∂VREF = = 0 and T ∂T ∂T VBE − (4 + m )VT − E g / q T Thus, we obtain VREF = Eg q =− , VT ln n T + (4 + m )VT The reference voltage exhibiting a nominally-zero TC is given by a few fundamental numbers: the bandgap voltage of silicon (Eg /q), the temperature exponent of mobility (m), and the thermal voltage (VT). The term “bandgap” is used here because as T → 0, VREF → Eg /q. Analog Circuit Design 11-17 Ching-Yuan Yang / EE, NCHU Supply dependence and start-up The output voltage is relatively independent of the supply voltage so long as the open-loop gain of the op amp is sufficiently high. The circuit may require a start-up mechanism because if VX and VY are equal to zero, the input differential pair of the op amp may turn off. The supply rejection of the circuit typically degrades at high frequencies owing to the op amp’s rejection properties, often mandating “supply regulation.” Analog Circuit Design 11-18 Ching-Yuan Yang / EE, NCHU Curvature correction z Curvature in temperature dependence of a bandgap voltage Bandgap voltages exhibit a finite “curvature,” i.e., their TC is typically zero atone temperature and positive or negative at other temperatures. The curvature arises from temperature variation of base-emitter voltages, collector currents, and offset voltages. z Variation of the zero-TC temperature for differences samples Many curvature correction techniques have been devised to suppress the variation of VREF in bipolar bandgap circuits but they are seldom used in CMOS counterparts. This is because, due to large offsets and process variations, samples of a bandgap reference display substantially different zero-TC temperatures (right Figure) ,making it difficult to correct the curvature reliably. Analog Circuit Design 11-19 Ching-Yuan Yang / EE, NCHU PTAT current generation z Generation of a PTAT current z Generation of a PTAT current using a simple amplifier M1 = M2, M3 = M4 → ID1 = ID2 → VX = VY VT ln n R1 In practice, due to mismatches between the transistors I D1 = I D 2 = and the TC of R1, the variation of ID5 deviates from the ideal equation. Analog Circuit Design 11-20 Ching-Yuan Yang / EE, NCHU PTAT current generation (cont’d) z Generation of a temperature-independent voltage M1 = M2, M3 = M4 = M5, the output equals VREF = VBE 3 + R2 VT ln n R1 If ∂VREF /∂T = 0 , we can find the required reference value. In reality, mismatches of the PMOS devices introduce error in Vout. Analog Circuit Design 11-21 Ching-Yuan Yang / EE, NCHU Constant-Gm biasing z Supply-independent bias It is often desirable to bias the transistors such that their transconductance does not depend on the temperature, process, or supply voltage. Supply-independent bias circuit: I out = 2 1 ⎛ 1 ⎞ ⎜1 − ⎟ μ nCox (W / L )N RS2 ⎝ K⎠ 2 2 ⎛ 1 ⎞ ⎛W ⎞ ⎜1 − ⎟ The transconductance of M1 equals , g m1 = 2μ nCox ⎜ ⎟ I D1 = RS ⎝ K⎠ ⎝ L ⎠N independent of the supply voltage and MOS device parameters. In reality, the value of RS does vary with temperature and process. Analog Circuit Design 11-22 Ching-Yuan Yang / EE, NCHU Constant-Gm biasing (cont’d) z Constant-Gm biasing by means of a switched-capacitor resistor. Switched-capacitor resistor RS = 1 CS f CK Since the absolute value of capacitors is typically more tightly controlled and since the TC of capacitors is much smaller than that of resistors, this technique provides a higher reproducibility in the bias current and transconductance. z Voltage-to-current conversion by means of a switched-capacitor resistor. Analog Circuit Design 11-23 Ching-Yuan Yang / EE, NCHU Speed issue z Effect of circuit transients on reference voltages and currents For fast changes in VN, the op amp cannot maintain VP constant and the bias currents of M5 and M6 experience large transient changes. Also, the duration of the transient at node P may be quite long if the op amp suffers from a slow response. For this reason, many applications may require a high-speed op amp in the reference generator. The critical node P can be bypassed to ground by means of a large capacitor (CB) so as to suppress the effect of external disturbances. This approach involves two issues: • The stability of op amp must not degrade with the addition of CB, requiring the op amp to be of one-stage nature. • Since CB generally slow down the transient response of the op amp, its value must be much greater than the capacitance that couples the disturbance to node P. Analog Circuit Design 11-24 Ching-Yuan Yang / EE, NCHU Speed issue (cont’d) z Effect of increasing bypass capacitor on the response of a reference generator z Setup for testing the transient response of a reference generator Analog Circuit Design 11-25 Ching-Yuan Yang / EE, NCHU Noise issue z A/D converter using a reference generator If a high-precision A/D converter employs a bandgap voltage as the reference with which the analog input signal is compared, then the noise in the reference is directly added to the input. z Circuit for calculation of noise in a reference generator iD1 = iD2 = −gmPVP = Vn,out /(R1 + gmN−1) → VP = −gmP−1Vn,out /(R1 + gmN−1) and VP = A0Vin,op Node A: Vn ,out R1 + g −1 mN ⋅ 1 + Vin ,op = Vn ,op + Vn ,out g mN Since typically gmPA0 >> gmN >> R1−1, we have |Vn,out| ≈ Vn,op. The noise of the op amp directly appears at the output. Even the addition of a large capacitor from the output to ground may not suppress low-frequency 1/f noise components ,a serious difficulty in low-noise application. Analog Circuit Design 11-26 Ching-Yuan Yang / EE, NCHU Simplified core of a bandgap circuit (a) Addition of cascode devices to improve supply rejection (b) Use of self-biased cascode to eliminate Vb1 and Vb2 Analog Circuit Design 11-27 Ching-Yuan Yang / EE, NCHU Generation of a floating reference voltage Vout = Analog Circuit Design 11-28 R R4 VBE 4 + 2 5 VT ln n R6 R1 Ching-Yuan Yang / EE, NCHU Regulation of supply voltage to improve supply rejection Analog Circuit Design 11-29 Ching-Yuan Yang / EE, NCHU