* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Si oxidation and dielectrics

Induction heater wikipedia , lookup

Printed circuit board wikipedia , lookup

Waveguide (electromagnetism) wikipedia , lookup

Piezoelectricity wikipedia , lookup

Hall effect wikipedia , lookup

Alternating current wikipedia , lookup

Multiferroics wikipedia , lookup

Electric current wikipedia , lookup

History of electrochemistry wikipedia , lookup

Mains electricity wikipedia , lookup

Electricity wikipedia , lookup

Supercapacitor wikipedia , lookup

Niobium capacitor wikipedia , lookup

Tantalum capacitor wikipedia , lookup

Electromotive force wikipedia , lookup

Electric charge wikipedia , lookup

Aluminum electrolytic capacitor wikipedia , lookup

High voltage wikipedia , lookup

Static electricity wikipedia , lookup

Opto-isolator wikipedia , lookup

Nanofluidic circuitry wikipedia , lookup

Electroactive polymers wikipedia , lookup

Electrostatics wikipedia , lookup

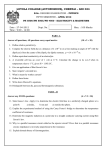

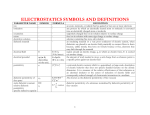

Si Oxidation and Dielectrics Topics: Capacitors & Dielectrics Piezoelectrics Oxide films on Silicon MSE630 Capacitance A parallel plate capacitor when in a vacuum (above) and when a dielectric material is present (below Do ≡ charge density (C/m2) eo = permittivity of free space = 8.85 x 10-12 F/m ξ ≡ electric field strength = V/l P ≡ polarization, or increase in charge density due to presence of a dielectric MSE630 The capacitance, C is related to the quantity of charge stored on either plate Q by : C = Q/V Where V = applied voltage. Units for C are coulombs per volt, or farads Capacitance can also b e expressed as C = eoA/l Where eo is permittivity of free space, A is the area of the plate and l is the plate separation distance MSE630 If a dielectric is placed between the plates, the capacitance is: C = e A/l e is the permittivity of the dielectric. The relative permittivity, er, called the material dielectric constant, is typically used: er = e/eo Thus C = ereo A/l MSE630 The applied electric field aligns the poles of the molecules in the dielectric. This is the source of polarization. The charge density, D, is D = eoξ + P And P may be written as P = eo(er-1)ξ Thus D =eoerξ MSE630 Relative permittivity of nitrobenzene as a function of temperature Effect of frequency and temperature on the permittivity of soda-limesilica glass MSE630 Electronic polarization: fluctuations in the electron cloud Ionic polarization: displacement of ions in an ionic compound Orientation polarization: rotation of permanent dipole moments in presence of an applied field Variation of dielectric constant with frequency of an alternating electric field. Electronic, ionic and orientation polarization contributions to the dielectric constant are indicated MSE630 Dielectric Breakdown Dielectric strength of various solids, gases and vacuum in uniform fields. Breakdown voltage versus dielectric thickness is plotted MSE630 • In a series circuit, capacitance is : C1 C2 • In a parallel circuit, circuit, capacitance is Ctotal = C1 + C2 +…Cn : 1 1 1 Ctotal = .... C1 C2 Cn C1 C2 MSE630 Piezoelectrics Figure (a) shows the electric dipoles in a piezoelectric material In a piezoelectric material, e.g. barium titanate, the Ti4+ and O2- ions are offset as shown When the material is compressed (b) the central Ti4+ is displaced, creating a voltage Applying a voltage (c) reverses this affect, causing the ions to move farther apart MSE630 Piezoelectrics Field produced by stress: = g Strain produced by field: e = d Elastic modulus: 1 E= gd = electric field = applied stress E=Elastic modulus d = piezoelectric constant g = constant MSE-512 MSE630 Thermal Oxidation and the Si/SiO2 Interface Oxides play an important part in semiconductor fabrication. They are: •Easily grown or deposited on many substrates •Adhere well •Block diffusion of dopants and other unwanted impurities •Resistant to most processing chemicals •Easily patterned and etched with plasmas or specific chemicals •Excellent insulators •Have stable and reproducible properties Virtually all other semiconductor/insulator combinations suffer from one or more problems that significantly limit their applicability MSE630 The most critical application of insulators in CMOS devices is as gate insulators. As seen above, these need to be <1 nm thick within the next 4 years MSE630 • SiO2 layers in CMOS are used as: – Gate dielectric layers – A mask against implantation – An isolation region laterally between devices – An insulator between metal layers MSE630 Oxide Growth In ambient conditions, an oxide ~1 nm thick forms After several hours, its final thickness is 1-2 nm Oxides are thermally grown on wafers by heating in the presence of O2 or H2O MSE630 Basic Concepts Because SiO2 is less dense than Si, it expands. This places the Si substrate in tension, and compresses the SiO2, forcing it upward New interface moves downward into Si MSE630 MSE630 SiO2 layers are amorphous. The bridging oxygen bonds can rotate, randomly accommodating SiO2 tetrahedra MSE630 There are four basic types of defects or charges at the interface: 1. Qf, the fixed oxide charge. It has magnitude of 109 – 1011 cm-2 very close to the interface. Results from incompletely oxidized Si atoms with a net positive charge. Qf is stable. Charges associated with the SiO2/Si system 2. Qit, the interface trapped charge. Similar to Qf, with dangling bonds located in oxide, very close to interface. Charge on Qit may be positive, negative or neutral and can change during operation. Density is about the same as Qf. MSE630 There are four basic types of defects or charges at the interface: 3. Qm, mobile charges. These are often processing artifacts causing erratic gate threshold voltages. These problems have been largely eradicated with proper cleanroom techniques. Charges associated with the SiO2/Si system 4. Qot, the oxide trapped charge. Occurring anywhere in the oxide, these result from broken Si-O bonds, away from the interface. Usually caused by processing damage, they can often be removed by high-temperature annealing. All types of charged defects have a negative effect on device performance MSE630 Oxide Measurement Methods Optical Light reflection from a sample with a transparent thin film on its surface. no is the index of refraction in air (1.0), ni is that of the film and n2 is that of the substrate. f is the angle of incident light, b is the angle of reflecting light at the bottom of the interface max, min = 2n1 xo cos b m where no sin f b = sin n 1 1 m = 1,2,3… for maxima and ½, 3/2, 5/2… for minima MSE630 Measurement Methods: the MOS Capacitor If a DC voltage +VG is applied to the gate, negative charges will be attracted across the oxide layer, producing a capacitance Cox accumulation If a negative voltage -VG is applied to the gate, negative charges will be repelled across the oxide layer, producing depletion region with its own capacitance, CD, in series with the oxide capacitance Cox |QG| = |QD| = ND/xD depletion Where QG, QD are units of number of charges per cm2, ND is the doping in the substrate (assumed uniform). xD is the depth of the depletion region. CD = es/xD es = permittivity of Si MSE630 Measurement Methods: the MOS Capacitor If a large enough –VG is applied, it will attract minority carrier holes in the substrate to the surface and form an inversion layer (in this case, of P-type carriers. The gate voltage at which this occurs is called the threshold voltage, Vth. At this point, xD stops expanding at xDMax inversion For all regions of the capacitor, the gate charge must be balanced by the charge on the substrate, or: QG = NDxD + QI, Where QI is the charge density on the inversion layer. Since xD is maximum, the CV curve reaches a minimum as shown above. MSE630 The End MSE630 MSE630 MSE630 MSE630