* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download 3 The MOS Transistor Inverter Dynamic Characteristics

Mercury-arc valve wikipedia , lookup

Stepper motor wikipedia , lookup

Three-phase electric power wikipedia , lookup

Thermal runaway wikipedia , lookup

History of electric power transmission wikipedia , lookup

Electrical substation wikipedia , lookup

Electrical ballast wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Stray voltage wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Distribution management system wikipedia , lookup

Voltage optimisation wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Mains electricity wikipedia , lookup

Alternating current wikipedia , lookup

Two-port network wikipedia , lookup

Voltage regulator wikipedia , lookup

Opto-isolator wikipedia , lookup

Current source wikipedia , lookup

Solar micro-inverter wikipedia , lookup

Semiconductor device wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Power electronics wikipedia , lookup

Buck converter wikipedia , lookup

Power inverter wikipedia , lookup

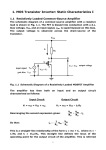

3. MOS Transistor Inverter: Dynamic Characteristics 3.1 The MOS Inverter with Capacitive Loading A schematic diagram of the simple MOS transistor inverter with a capacitive load is shown below in Fig. 3.1. Operation is governed by similar considerations as in the case of the bipolar transistor inverter. When the transistor is conducting it actively contributes to driving the load, but when it is off the output conditions become heavily load dependent. VDD iRD RD iCL iD CL VO = VDS Vi =VGS Fig. 3.1 Circuit of the Capacitively Loaded Simple MOS Inverter 3.2 Transistor Turn-Off and Inverter Rise-Time If the switching of the transistor is taken as ideal, then when the transistor is turned off the capacitor simply charges up exponentially through RD. This is the same process for any C-R charging circuit so that the same expressions will apply for the 10% and 90% points of the output voltage as in the case of the bipolar transistor inverter. Consequently, an almost identical expression is obtained for the 10% to-90% rise time as: tR 2.2CLRD If CL = 10pF and RD =100kΩ, then tR = 2.2µs. This is much higher than in the case of the bipolar transistor inverter because of the much higher value of resistor RD which is used because of the lower levels of current in MOS transistors. 1 3.3 Transistor Turn-On and Inverter Fall-Time In this case, the transistor conducts and plays an active role in discharging the capacitance by drawing charge from it. The waveform of the output voltage is shown in Fig. 3.2. Initially the output voltage will be at the supply voltage, VDD, with the capacitance fully charged. If an input voltage of Vi = VDD is applied to the gate of the transistor, then this means that initially the transistor operates with VGS = VDD and with VDS = VDD so that VDS > VGS – VT and therefore the transistor operates in the saturation region as shown in the waveforms. Once the output voltage falls below the supply voltage by an amount equal to the threshold voltage, then VDS < VGS – VT and the transistor operates in the non-saturation region. Ultimately, the capacitor will be discharged to the value of the output logic LO voltage, VOL, determined previously. As can be seen from the waveform, generally the 90% point will be reached while operating in the saturation region but the 10% point will be reached while operating in the non-saturation region. This complicates the solution of equations for the fall-time. A further complication is the square term in the expression for the drain current when operating in the non-saturation region, which makes it more difficult to obtain a solution. This is cumbersome and the problem can be simplified if approached in a different manner. transistor operates in the saturation region VO(t) VDD transistor operates in the nonsaturation region 90% VDD - VT final logic LO value is reached VOL 10% t10 t90 Fig. 3.2 A Waveform of the Output Voltage from the Capacitively Loaded MOS Inverter 2 t Things can be simplified if the transistor is treated simply as a current source having an average value of current iD AVE discharging the capacitor as shown in Fig 3.3. The average current can be taken as the average of the initial and final values of current during the discharging operation. VDD iRD RD iCL iD AVE VO (t) CL Fig. 3.3 Equivalent Circuit with the MOS Transistor as a Current Source The initial value of current can be taken as the value for operation in saturation with Vi = VDD as: iD t 0 Kn VDD VT 2 The final value of current can be taken as the current flowing through the load resistor RD when the capacitor has been discharged to the minimum voltage of VOL , which with VOL > 0 is: iD (t ) VDD VOL VDD RD RD This then gives the average current as: K V VT VDD /R D n DD 2 2 iD AVE 3 From the circuit of Fig. 3.3, using Kirchhoff’s Current Law it can be seen that: iD AVE iR D iCL iD AVE VDD VO dVO CL RD dt Dividing across by CL and rearranging gives: dVO 1 V i VO DD D AVE dt CLRD CLRD CL Taking the Laplace transform with VO(t=0)=VDD and reorganising gives: 1 VDD i s VO s VDD D AVE CLRD sCLRD sCL 1 1 VDD iD AVER D VDD CLR D CLR D VO s 1 1 1 s s s s s C R C R C R L D L D L D Taking the inverse Laplace transform gives: VO t VDD e -t CL R D -t C L VDD 1 e R D -t C RD L i D AVER D 1 e So that finally: VO t VDD -t iD AVERD 1 e CLR D 4 As before, we want to identify the 90% and 10% points on the waveform. So at t = t90 with VO = 0.9VDD then: 0.9VDD VDD -t 90 C iD AVERD 1 e LR D When manipulated this gives: iD AVERD t 90 CLRD ln iD AVERD 0.1VDD Similarly: iD AVERD t10 CLRD ln iD AVERD 0.9VDD So that the fall time is then given as: i R 0.1VDD t f t10 t90 CLRD ln D AVE D i R 0 . 9 V DD D AVE D With parameter values Kn=100μAV-2, RD=100kΩ, VT=1V and VDD=10V: K n VDD VT VDD /R D 10 4 x 81 10/10 5 4mA 2 2 2 iD AVE t f 10 -11 4x10 -3 x105 1 399 6 x10 ln 10 ln -3 5 391 4x10 x10 9 5 So that: t f 20ns This is again a little higher than for the bipolar transistor inverter because of the higher value of load resistance. 5